目录

FIFO IP核的使用——篇2

完成:1.读模块,

2.整合到顶层文件、例化,管脚约束

3.编写激励、使用ILA逻辑分析联调硬件

1.编写FIFO“读模块”

因为“读模块”和“写模块”几乎完全对应,所以写起来会轻松很多

直接复制所有的fifo_wr代码,然后做修改即可

没有读空,就将读使能打开,一直读数据

和写模块组成循环:因为本次实验,想展示:写——写满——再读——读空——再写,的一个功能。

2.例化 读/写/IP核 模块

1.例化

//虽然IP核创建使用的异步时钟,但实际上输入时钟用的同一个(意思一下)

//如果需要使用不同的时钟,使用MMRC 时钟IP核,创建两个不同的时钟输出即可——见笔记1

//但是注意:重新定义FIFO IP核的位宽,输入输出速度要一致,否则出现上/下溢出,需要写等待的功能,如果没写,会造成数据的丢失!

//不要读数据的输出fifo_rd_data,直接在顶层做一个ILA的软核看输出数据

//wire fifo_rd_data ;

例化

修改完以后,保存代码,在Vivado中综合一下——成功!

2.管脚约束:打开原理图——I/O planning

管脚约束操作:

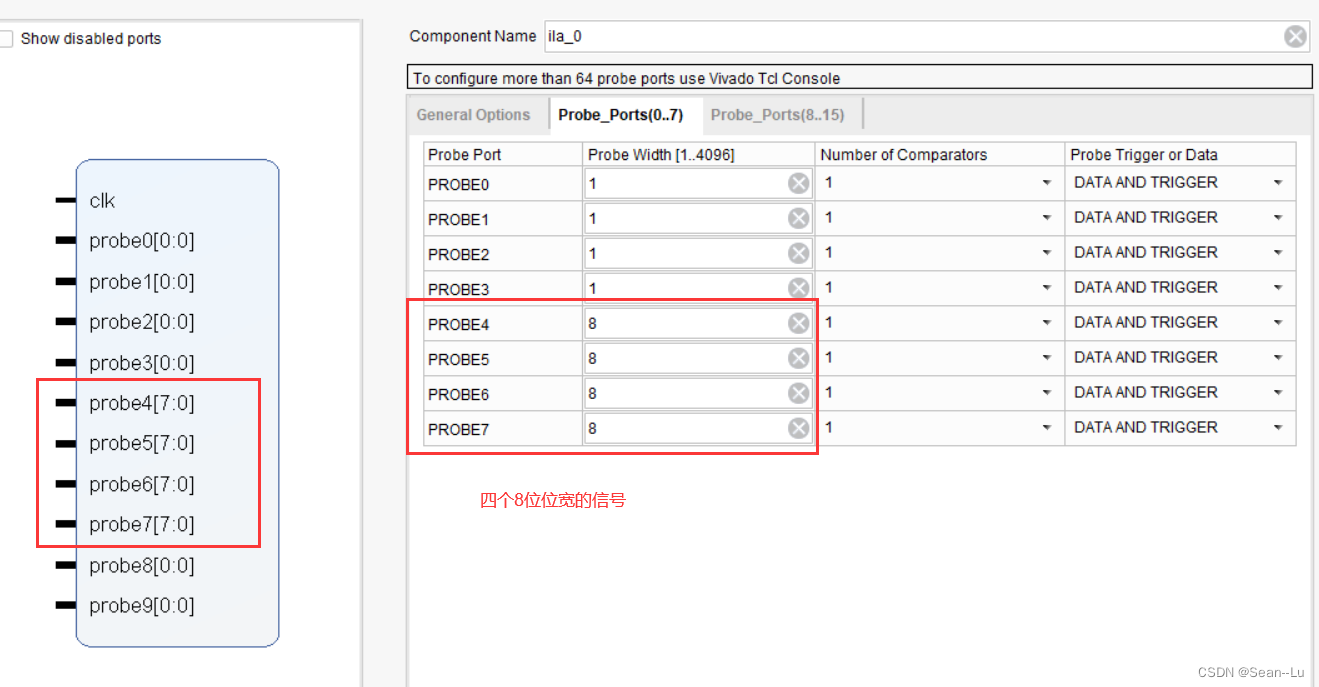

3.ILA逻辑分析仪(10根信号)+ 激励

1.创建ILA+例化

在顶层文件例化好

2.生成bit流文件,下载到板子,联调

这次遇到一个问题,一开始一直打不开program device这个界面,最后重启了Vivado才终于有了!

3.分析结果

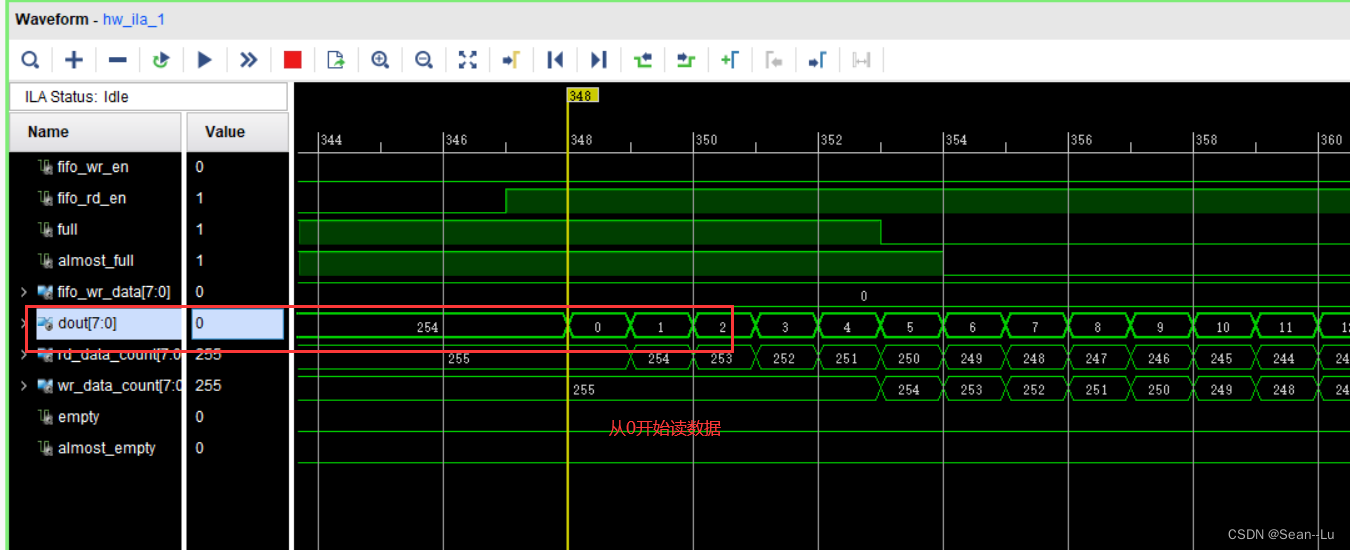

1.从0开始写数据,写到254!

2.从0开始读出数据,读到254

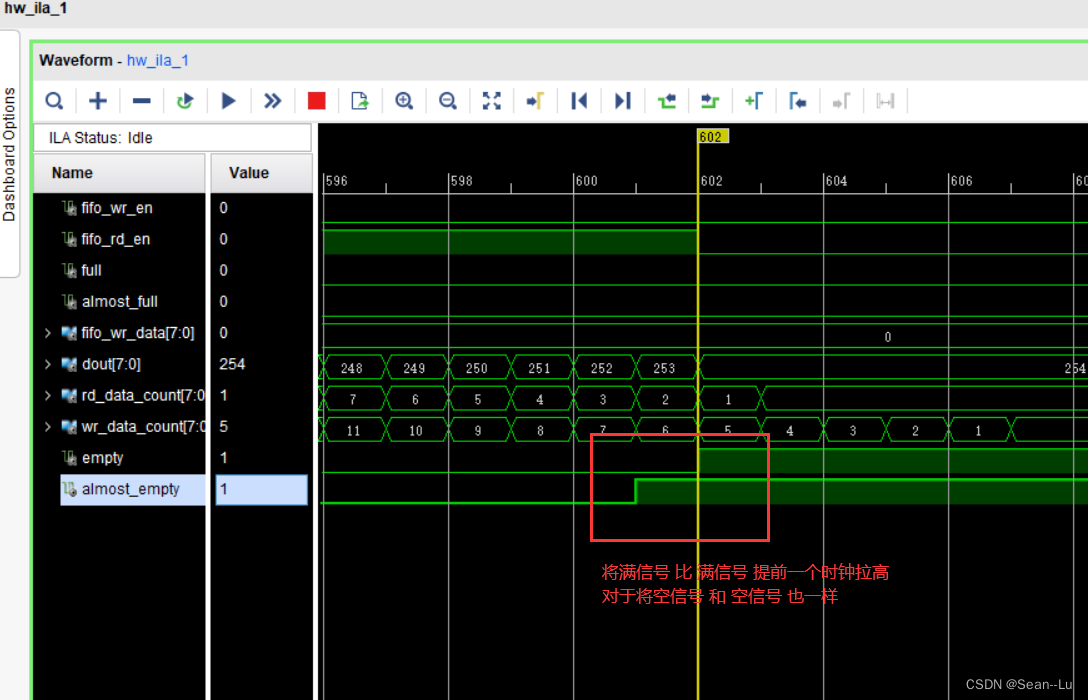

3. 将空/将满 空/满信号——符合一个时钟差

4120

4120

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?