DDR信号的构成

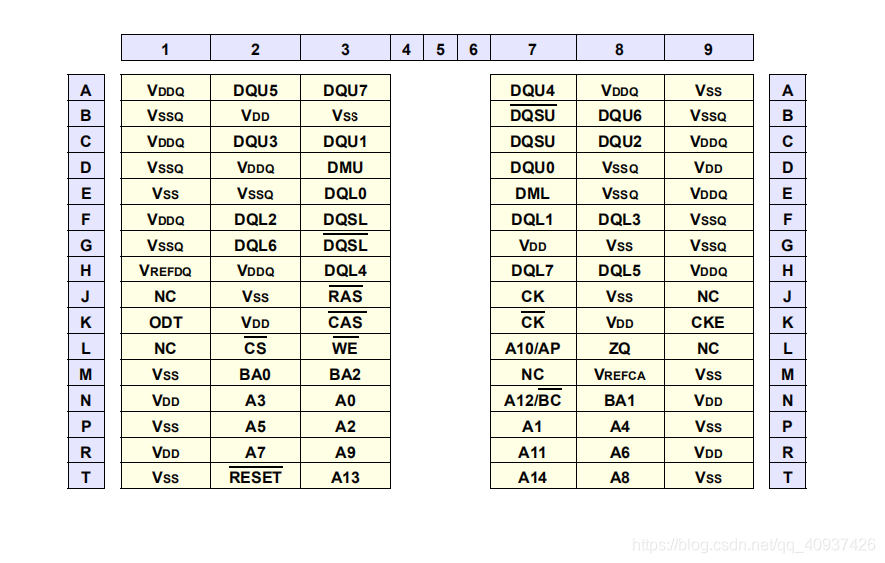

以三星DDR3内存颗粒为例:

| 信号名 | 功能描述 |

|---|---|

| CK,CK# | 全局时钟输入,差分信号 |

| CKE | 时钟使能信号 |

| CS# | 芯片使能信号 |

| ODT | 片内电阻端接,控制芯片内部的端接电阻 |

| RAS, CAS, WE | [命令信号]行地址信号,列地址信号,写使能有效 |

| DM(DMU), (DML) | 数据掩码 |

| BA0 - BA2 | Bank地址信号 |

| A0 - A14 | 地址总线 |

| A10 / AP | 自动预充电 |

| A12 / BC# | 突发终止(Burst Chop) |

| RESET# | 低电平复位 |

| DQ(DQU,DQL) | 数据总线 |

| DQS, (DQS#) | 数据控制,差分信号 |

| TDQS, (TDQS#) | 终止信号控制 |

| VDDQ | DQ电源提供 1.5V或者1.35V |

| VSSQ | DQ地 |

| VDD | 电源 1.5V或者1.35V |

| VSS | 地 |

| VREFDQ | DQ参考电压 |

| VREFCA | CA参考电压 |

| ZQ | ZQ校准参考脚 |

以三星为例

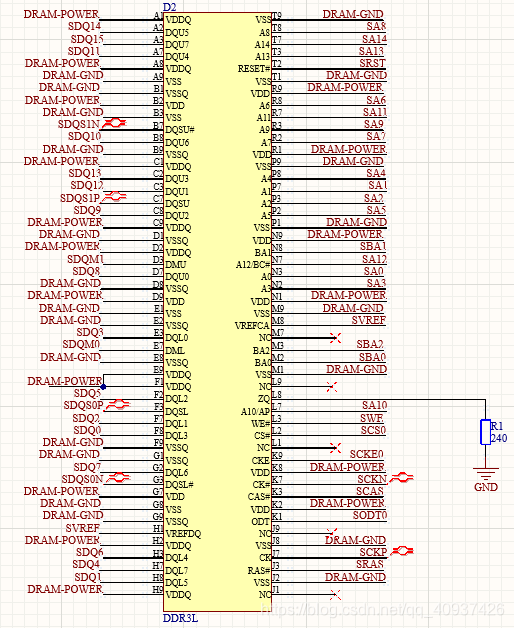

对应的原理图

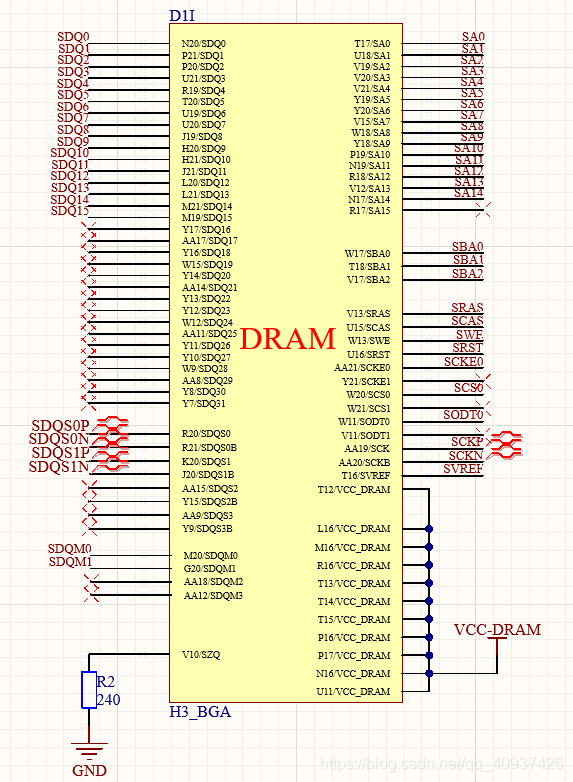

对应CPU接口

| 芯片管脚名称 | 作用 |

|---|---|

| VDDQ,VDD,VSS,VSSQ | 电源和隔离电源,地和隔离地。 |

| DQU0-7,DQL0-7 | 数据总线 |

| DMU[DQM1] DML[DQM0] | 分别对应DQU0-7和DQL0-7的数据掩码 |

| 差分DQSU,差分DQSL | 分别对应DQU0-7和DQL0-7数据选通 |

| A0-A14 | 地址线 |

| BA0-BA2 | Bank地址线 |

| 差分CK | 时钟线 |

| 其他的控制线 | / |

简单分个类

数据线:DQ

地址线:A0-A14,DM(DMU), (DML) ,DQS, (DQS#) |

控制线:ZQ,CS,RAS, CAS, WE,RESET#,BA0 - BA2,CKE,ODT

时钟线:CK,CK#

电源线和GND

阻抗特性

- 单端50欧

- 差分100欧

注意,厂家的标准设计中是向PCB板厂定制的阻抗板,作为个人(除非你有钱)你必须得按照PCB提供的标准参数进行阻抗设计,而不是按照芯片厂家提供的数据进行阻抗计算。

走线

数据线(高八位,低八位分别为一组)尽量走在一层上

信号线直接间距3W或者2W原则,W为信号线宽。

信号线,地址线,控制线,时钟线,也满足3W或者2W原则,或者20mil

VREF电源线宽20mil-30mil

间距

具体请看厂家给出的标准设计中的说明,不同厂家的芯片能接受的误差不一样,有的教程里宣称误差应该小于50mil,实际设计中,同组内500mil的误差是可以接受。

唯一可以确定的是,差分线长度的误差请尽可能的小!!!一般不大于10mil

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?