本节介绍TRAVEO™ T2G微控制器(MCU)的启动顺序。有关TRAVEO™ T2G微控制器的安全特性、不同的生命周期阶段以及“安全启动”序列的详细描述,请参阅 AN228680 -Secure system configuration in TRAVEO™ T2G family.

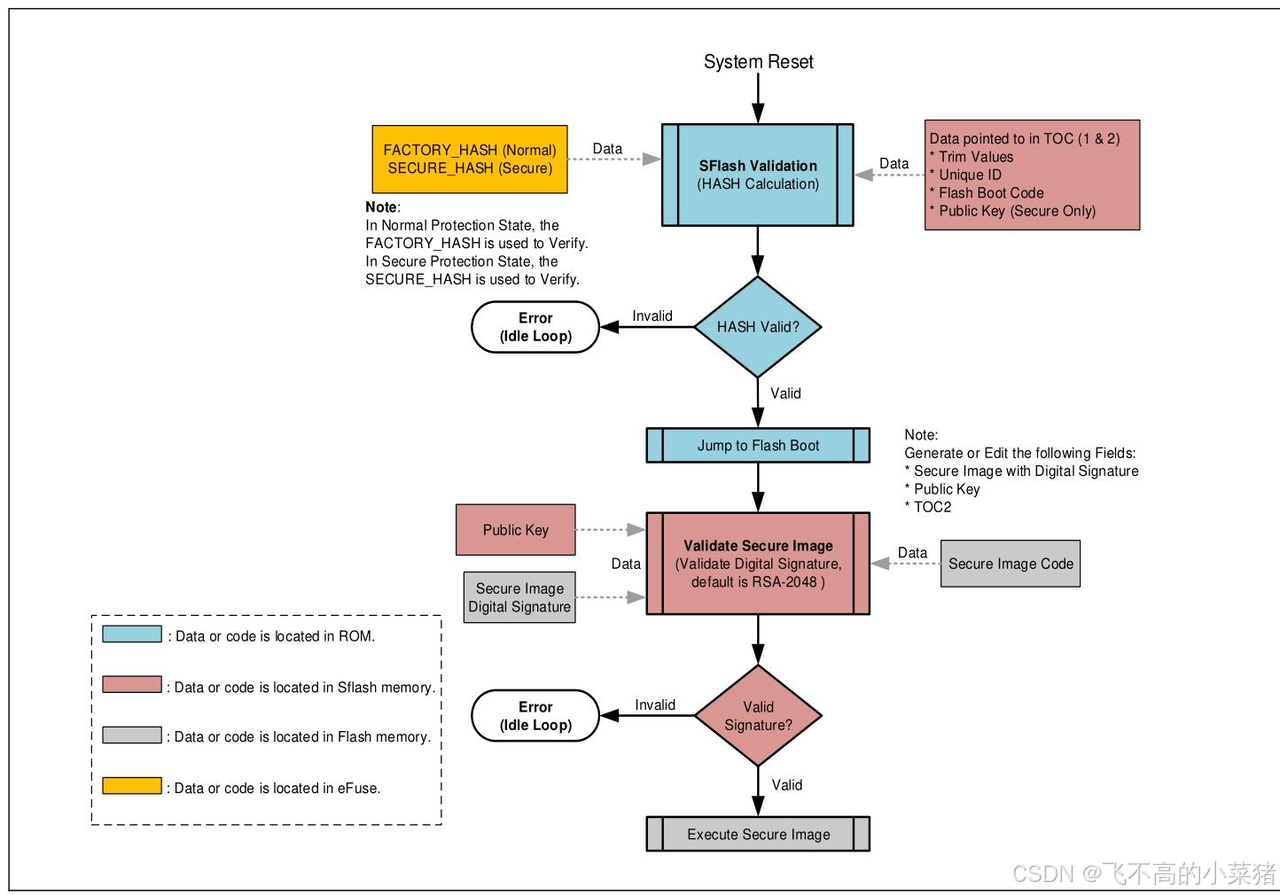

TRAVEO™ T2G微控制器(MCU)的启动序列(见图3)基于为不同生命周期阶段实现的ROM启动代码和闪存启动代码。图3展示了CM0+从复位开始的操作过程。复位后,CM0+从ROM启动代码开始执行。ROM启动代码会验证监控闪存(SFlash)。SFlash验证完成后,执行流程跳转到闪存启动代码,并根据保护状态的需要配置调试访问端口(DAP)。请注意用于表示数据和代码所在内存类型的颜色编码。

然后,闪存启动会验证TOC2中列出的第一个应用程序。如果验证通过,就会跳转到其入口点。这个镜像就是 “安全 ”镜像。如果发现 “安全 ”镜像无效或损坏,CPU将跳转到空闲循环,并一直停留在空闲循环中,直到设备复位。

1. 安全FOTA的“安全启动”机制

本应用笔记提出的安全FOTA架构和示例代码在“

订阅专栏 解锁全文

订阅专栏 解锁全文

46

46

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?