数据选择器的应用想了想还是把一些简单的东西写出来,希望对刚入门的初学者有所帮助

(1)用3线-8线译码器编译宏模块74LS138设计和实现三人表决电路。用FPGA实现其逻辑功能并测试。使用QuartusII 完成创建工程、编辑电路图、编译,编辑波形文件仿真,测试其功能,记录波形并说明仿真结果。

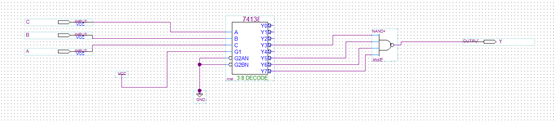

原理图

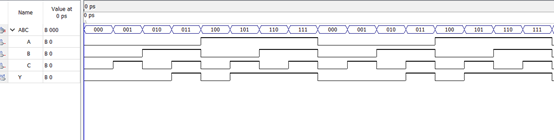

波形图

74LS138-三人表决电路

最新推荐文章于 2023-08-19 16:15:42 发布

数据选择器的应用想了想还是把一些简单的东西写出来,希望对刚入门的初学者有所帮助

(1)用3线-8线译码器编译宏模块74LS138设计和实现三人表决电路。用FPGA实现其逻辑功能并测试。使用QuartusII 完成创建工程、编辑电路图、编译,编辑波形文件仿真,测试其功能,记录波形并说明仿真结果。

原理图

波形图

1万+

1万+

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?