1. 均衡

在Tx端有FFE(Feed Forward Equalizer,前馈均衡器);在Rx端有:CTLE(Continuous Time Linear Equalizer,连续时间线性均衡器)和DFE(Decision Feedback Equalizer,判决反馈均衡器)。通过FFE和CTLE,可以去除大部分由ISI所引入的抖动;通过DFE可以进一步去除ISI,它还能去除部分的阻抗失配所造成的反射。通过这些均衡处理,就能够最大程度上地保证在接收端判决输入处将眼图打开,保证信号的质量能够满足数据传输的要求。

再PCIE4.0版本之后,规范针对RC(downstream port) 以及EP (upstreamport)的phase分别进行了说明。

- 均衡procedure 必须要在第一次速率进行切换时进行,它不需要因为可靠性差导致link fail 而进行重复操作,他会存储Transmitter setting 为了方便后续进入更高的速度。规范允许在均衡完成后对Receiver 进行微调(只要其不影响link 稳定性)或者进入Recovery 重新训练。

- 均衡procedure 可以通过sofrware 或者硬件自动运行,但是规范强烈建议使用自动运行方式,如果不支持硬件自动运行则必须要是虚掩软件可配置以确保可以控制。

- 若两边的设备均支持8.0GT 及以上的速率则会硬件自动均衡,硬件自动均衡仅仅会及进行8GT/s的自动均衡操作(两端设备均支持此8GT and 16 GT 或仅支持16GT)。但是对于链路两端支持16GT 设备,软件触发则需要进行16GT/s的均衡流程。

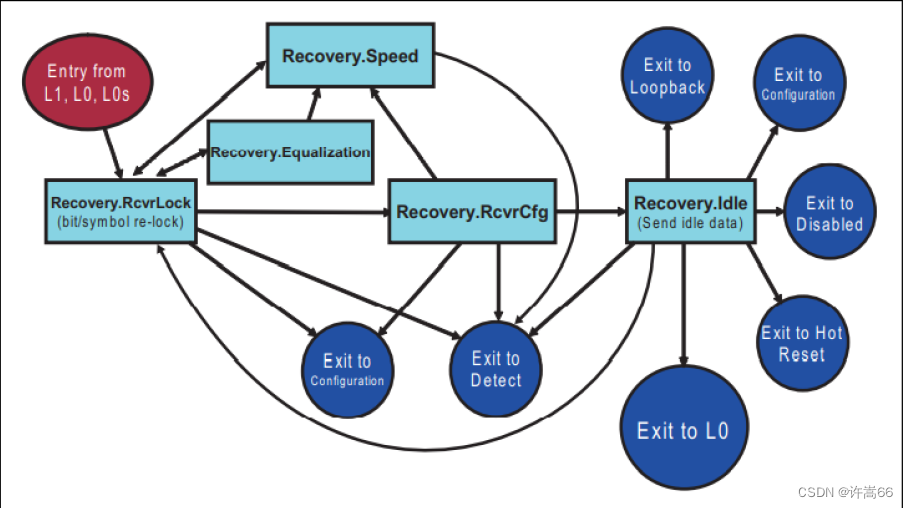

- RC 想去开始一个均衡进程,但是不能保证是否会对EP产生影响,规范允许它请求EP 发送均衡请求,这通过再RcvrCfg阶段发送Request Equalizaton bit =1 and Request Data Rate = desired speed and Quiesce Guarantee =1来完成请求,EP收到之后便会发起均衡操作(规范并未要求EP再收到后多久发起请求) ,RC再收到EP的response之后,如果均衡操作不会对operation造成影响则需要在Recovery -> L0 1ms内以商定的速度开启均衡 or 将相应速度下的Link Equalization Request of Link Status 2 register 设置为1。

-任何因速度切换而启动的均衡进程时间最长200ms,如果RC当前速度2.5GT 5GT ,想要进行8GT redo equalization ,需要向EP请求speed change to 8GT,如果EP想要使用8GT 并且收到RC发送的speed_change =1的EQ TS1 则EP需要向RC通告8GT能力。如果RC当前速度8GT ,想要进行16GT redo equalization ,则需要首先发送一个speed change to 8GT的操作,当前speed 调整到8GT 通过发送speed_change=1 and Equzalization Redo bit =1 TS 序列发起16GT/s的均衡操作,如果EP想要使用16GT 并且收到RC发送的speed_change =1 and Equalization Redo bit =1的EQ TS1 则EP需要向RC通告16GT能力。[这一部分会在RcvrLock 子阶段发送这些information]

1.2 autonomous (硬件自动)

若两边的设备均支持8.0GT 及以上的速率则会硬件自动均衡,RC 在进行8GT/s 均衡操作时不应该通告其具备16GT/s 的能力,在8GT均衡操作完成后,再开始16GT的均衡操作。

如果RC 检测到均衡错误 or EP 请求8GT/s 均衡操作(在RcvrCfg阶段设置TS 2序列中Request Equalizaton and Equalization Requeset Data reate 为0), RC则开始进行redo 均衡,同样时在8GT 均衡顺利结束后才会进行16GT的均衡(即便是两端设备均支持16GT/s,也需要8GT/s均衡成功完成后开始进行),**其中8GT redo 均衡的次数由用户指定。**如果在8GT/s 达到了redo 均衡最大尝试次数,还无法稳定工作在8GT/s 则必须回退到2.5GT/s or 5GT/s。

自动均衡操作完成之后才可以开始自动位宽降低的操作,EP禁止发送任何DLLP直到收到了DLLP,并且完成了均衡操作。 RC可以根据自己情况以及 EP的请求决定是否开启新的请求。

1.3 software

软件均衡必须保证不会对正常work产生副作用(timeout),软件配置流程 Perform Equalization bit =1, update Target link speed,Retrain LInk =1,与autonomous 均衡类似,只有等到8GT/s 完成之后才会进行16GT/s 的均衡。

2. Downstream

RC代表Downstream port, RC 需要从Recovery.rcvrlock 跳转到 Recovery.Equalization,它分为phase1 phase2 phase3 三个阶段。当进入Equalization状态后,需要将start_equalization_w_preset = 0 and equalization_done_8GT_data_rate = 1 and equalization_done_16GT_data_rate = 1

2.1 phase1

在此阶段会清除当前速率(8GT or 16 GT)的EQ_phase_successfullz指示位,同时也会设置start_equalization_w_preset = 0 。在该子状态下RC会持续发送EC =01 (symbol6 ), Transmitter Preset 根据当前的速率分别进行设定, FS LT Cursor 这些系数则根据preset值进行设定的TS1 order set。

其中Transmitter Preset 设定遵循如下三种原则:(优先级依次降低)

1. 如果当前速度为16GT (Gen4) 则基于在Recovery.RcvrCf状态收到的8GT EQ TS2 order set中的Transmitter preset value进行设定。

2. 否则需要根据当前速率的Lane Equalization Control Register (8GT) or 16 GT/s Lane Equalization Control Register (16GT) 中的字 端进行设置。

3. 要用一种特殊实现的方法选择一个有效的Transmitter preset values。

note:如果RC需要调整自己Receiver 则允许在phase1 等待500ns后,再去评估接收到的TS1 order set。

phase1 -> phase2

所有configured lanes 收到两个连续的TS1 order set with EC=01,且 RC想去调整到下一个phase2 or phase3 (可以立即为RC自己对Receiver 调节自身的BER,以保证可以稳定接收后续的EQ order set)。 [必须保证在2ms内可以完成bit lock 并可以稳定识别 Order set;设置相应速率的phase1 successfull = 1 ]

phase1 -> Recovery.Rcvrlock

所有configured lanes收到两个连续的TS1 order set with EC=01,且 RC不想想去调整到下一个phase2 or phase3。 [设置相应速率的phase1/2/3 successfull = 1 complete bit = 1]

phase1 -> Recovery.Speed

上述两个条件未满足,24ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]。

2.2 phase2

在该子状态TX会持续发送EC=10的TS1 order set,其关于FS LT cursor的系数设置在每条lanes是独立的,设置规则如下:

- 在接收到两个连续的EC=10的TS1 order set ,(包括当前的两次连续的TS序列中的参数,与上一次两次连续TS序列中的参数不同)的前提下,如果收到的preset 以及系数是合规的,则RC需要再收到第2个包含新请求的TS序列500ns内完成自身TX参数的调整(此时发送的TS1 序列中preset设置为请求的值,系数设置为Transmitter setting),否则保持当前TX电路的Transmitter setting 不变,但是需要在发送的TS序列中setting 设置为 EP请求的value并将Rejet Coefficient Vaule为1。

- 如果没有接收连续的的EC=10 的TS1 order set ,则按照当前的值保持不变。

phase2 -> phase3 - 所有configured lanes 收到两个连续的TS1 order set with EC=01,[必须保证在2ms内可以完成bit lock 并可以稳定识别 Order set;设置相应速率的phase2 successfull = 1]

** phase2 -> Recovery.Speed**

上述两个条件未满足,32~36ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]。

2.3 phase3

在该子状态TX会持续发送EC=11的TS1 order set,会根据接收的TS1 order set评估信号质量,并向EP请求新的preset 和相关系数。若 Preset bit =1,此时是一个Preset 更改请求,否则是 Cursor 系数请求。另外协议要求RC必须持续请求1us,等待500+ns后,EP会使用RC请求的值填充子的TS1 序列的相应字段,并发送给RC。

只有RC接收到了从EP返回来的TS1 序列,且Preset以及相关系数相同,且Rejection Coefficient =0表示EP 接收了RC发送的请求。此外DSP负责发送的TS序列中设置Reset EIEOS Interval Count bit ,它根据自己的需求以及评估准测进行设定。

从请求到最终完成均衡一般不允许超过2ms,但是可以允许以同样的参数第二次尝试(此时的超时时间可以超过2ms但是不能超过24ms的状态超时),所有的lanes需要同时发送new preset and 系数,但是如果其中一些lane不需要改变当前设置,也是允许保持当前值不变继续发送。

phase3 -> Recovery.Rcvrlock

所有的configured lanes工作在最佳的工作模式,8 GT

所有的configured lanes工作在最佳的工作模式,且收到两个连续 Retimer Equalization Extend Bit = 0的TS1 序列 16 GT

设置相应速率的phase3_ successfull = 1 and complete bit =1。

phase3-> Recovery.Speed

上述两个条件未满足,24~26ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]。

3 Upstream

upstream 比downstream 多了一个phase0,一共包含phase0 phase1 phase2 phas3 四个阶段。当进入Equalization状态后,需要将start_equalization_w_preset = 0 and equalization_done_8GT_data_rate = 1 and equalization_done_16GT_data_rate = 1。

3.1 Phase0

在此阶段会清除当前速率(8GT or 16 GT)的EQ_phase_successfullz指示位,同时也会设置start_equalization_w_preset = 0。

当从2.5 or 5 GT -> 8GT时候,EP会使用在Recovery.RcvrCfg阶段的EQ TS2 order set (序列)中的Transmitter Preset field填充当前需要发送的TS1序列。当从8GT -> 16GT时,EP会使用8GT EQ TS2 序列中的Transmitter Preset field进行填充,如果收到的preset 字段是非法,则由实现者决定发送什么东西。

在该子状态会首先发送EC=00 的TS 序列,对于一些异常情况, Transmitter Preset field的填充遵循如下规则:

- 接收到了EQ TS2 or 8GT EQ TS2 序列再Recovery.RcvrCfg 状态,但是其中相应preset 字段RC 不支持,则待发送的preset使用EQ序列中解析出来的transmitter preset 进行填充,Coeffiient 由实现者指定,并且set Reject Coefficient bit = 1。

- 对于未收到EQ TS2 or 8GT EQ TS2 序列,则待发送的preset and coefficent 根据由实现者自行指定,并且clear Reject Coefficient bit。

note:如果RC需要调整自己Receiver 则允许在phase1 等待500ns后,再去评估接收到的TS1 order set。

补充:此阶段RC 和EP会交互Tx preset and RX preset hint 值,这个value 来源于EQ TS2 序列中的相应字段,序列中的字段为EP的Lane Equalization Control Reg的信息。对于16GT的协商, EP可以在RcvrCfg阶段发送rx and tx preset 由实现者指定的EQ TS2 的序列,并在phase 0会发送使用上述TS序列中的rx and tx preset 填充的TS序列(可选)。

**phase0 -> phase1 **

接收到两个连续的EC=01的TS1 order set。[LF FS 需要存储起来,放在phase2 使用;必须保证在2ms内可以完成bit lock 并可以稳定识别 Order set]。

phase0 -> Recovery.Speed

上述两个条件未满足,12ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]

3.2 Phase1

phase1 会根据phase0 决定的transmitter setting 构造TS1 序列,并设置EC=01b。

phase1 -> phase2 **

接收到两个连续的EC=10的TS1 序列,并设置相应速率的phase1 successful =1。

** phase1 -> Recovery.Rcvrlock

接收到8个连续的EC=00的TS1序列,并设置相应速率的phase1 successful = 1。

phase1 -> Recovery.Speed

上述两个条件未满足,12ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]。

3.3 Phase2

会通过Receiver 接收到的TS 序列完成信号的评估,并向RC(Downstream)请求相应的参数,在该子状态TX会持续发送EC=11的TS1 order set,会根据接收的TS1 order set评估信号质量,并向RC请求新的preset 和相关系数。若 Preset bit =1,此时是一个Preset 更改请求,否则是 Cursor 系数请求。另外协议要求EP必须持续请求1us(也就是说1us后才可以更新发送的preset),等待500+ns后,EP会使用RC请求的值填充子的TS1 序列的相应字段,并发送给EP。

从请求到最终完成均衡一般不允许超过2ms,但是可以允许以同样的参数第二次尝试(此时的超时时间可以超过2ms但是不能超过24ms的状态超时),所有的lanes需要同时发送new preset and 系数,但是如果其中一些lane不需要改变当前设置,也是允许保持当前值不变继续发送。

3.4 Phase3

会发送EC=11的TS1 序列,与RC phase2 类似 此时EP会根据RC的请求调节自身的Transmitter参数。

** phase3 -> Recovery.RcvrLock**

所有的lanes 均收到两个连续的EC=00的TS1 序列,这表示RC已经从phase3 退出进入了RcvrLock 子状态,EP需要将相应速率下的Phase3 successful and Complete bit 置1.

phase3 -> Recovery.Speed

上述两个条件未满足,32ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]。

2687

2687

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?