本章目录:

1.电容的失配

2.分段结构CDAC

3.CDAC传统开关切换策略

4.单调开关切换策略

5.Sanyal开关切换策略

6.VCM-Based开关切换策略

目录

一、概述

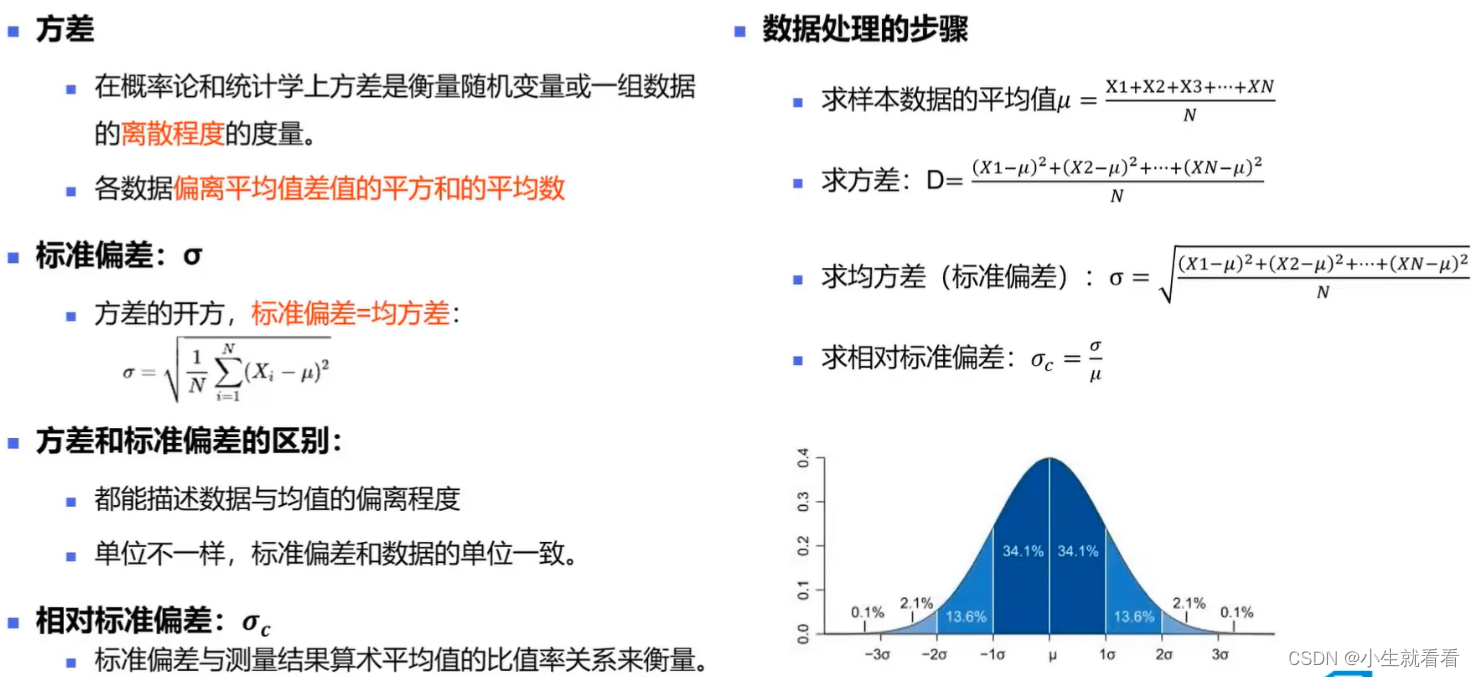

方差、标准偏差、相对标准偏差

失配

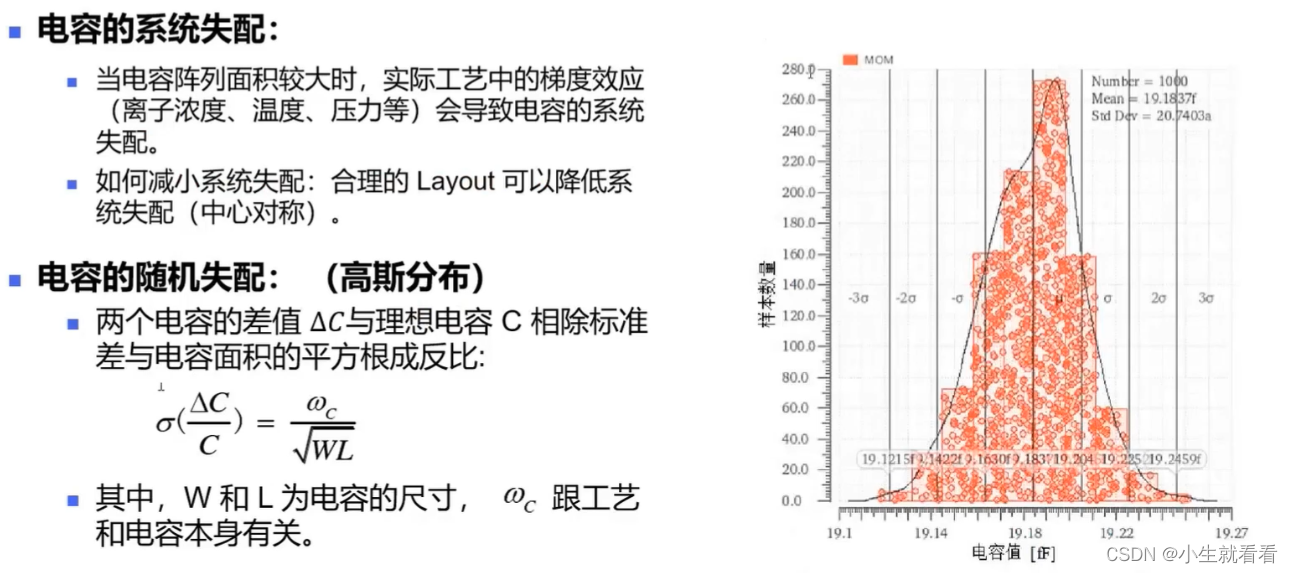

如图,蒙特卡洛仿真1000个点,平均值μ=19.2f,标准差1σ=20a,也就是电容有千分之一的误差。

电容的mismatch和sqrt(WL)成反比,即mismatch降低至原来2倍,电容面积要提升到4倍。

电容的随机失配:单个电容

问题:C1 = M个单位电容Cu,求C1的标准偏差σ1 和 相对标准偏差σc1 = σ1 / μ

已知:单位电容Cu的标准偏差为σ,相对标准偏差为σc

根据方差的定义:

所以有:

故: C1的均值:M*Cu

C1的方差:D(C1) = D(Cu1 + Cu2 + ...... +Cum) = D(Cu1) + D(Cu2) +......+D(Cum) = M*σ²

两个随机变量X,Y相对独立,则有D(X+Y)=D(X)+D(Y)

结论:

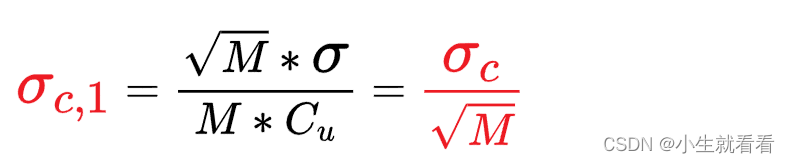

C1的标准偏差: ![]()

C1的标准偏差对C1均值(M*Cu)归一化得到相对标准偏差:

举例:100fF 电容的标准偏差 σ = 1fF

200fF 电容的标准偏差 = sqrt(2)*σ = 1.414fF ——(2个100fF的单位电容)

400fF 电容的标准偏差 = 2*σ = 2fF ——(4个100fF的单位电容)

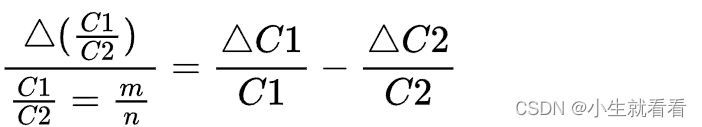

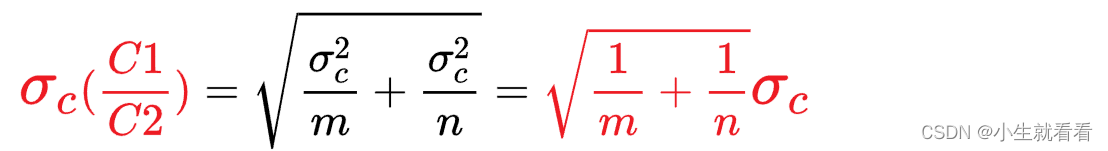

电容的随机失配:多个电容之比

已知:单位电容Cu的标准偏差为σ,相对标准偏差为σc ; C1= m*Cu , C2=n*Cu

问题:C1/C2的相对标准偏差?

C1/C2的差值(绝对偏差) = 实际C1/C2 - 理想C1/C2

![]()

归一化得C1/C2相对偏差 = 绝对偏差 / 平均值

有前文可得,△C1/C1 和 △C2/C2 分别为C1和C2 的相对标准偏差(绝对偏差/平均值)

![]()

所以C1/C2的相对标准偏差

结论:

当 m = n = 1 时,增益的相对标准偏差为 sqrt(2)*σc

当 m = 4, n=1 时,增益的相对标准偏差为 sqrt(5)*σc

当 m 远大于 n 时,增益的相对标准偏差为 sqrt(1/n)*σc

二、电容随机失配:Matlab验证

在Marlab中,使用 normrnd( mu, sigma, m, n )函数来验证电容的标准差

■ 生成正态分布,以 mu 为均值,sigma 为标准差,m行,n列。

C0 = normrnd(1, 1e-2, 1, 10000)

avg = mean(C0)

for i = 1:1:1000

C1(i) = sum( C0(8*(i-1) + 1:1:8*(i-1)+4) );

C2(i) = sum( C0(8*(i-1) + 5:1:8*i) );

i = i+1;

end

std_C1 = std(C1)

std_C2 = std(C2)

std_C1divC2 = std(C1./C2)Code解析:

■ C0是均值为1,σ 为0.01的随机变量;

■ C1和C2是样本数为1000的矩阵,其中每个元素皆为任意4个C0之和;

■ C1(或C2)的理论均值为4,理论标准差=sqrt(4)*σ = 0.02

■ C1/C2的理论均值为1,理论相对标准差=sqrt(1/4 +1/4)*σ = 0.0071(均值为1,标准差和相对标准差一样)

%C1

k1 = 10;

k2 = 20;

C0 = normrnd( 1, 1e-2, 1, 500000 );

]for i = 1 : 1 : 5000

C1(i) = sum( C0(k1*(i-1)+1 : 1 : k1*i) );

i = i+1;

end

%C2

C0 = normrnd( 1, 1e-2, 1, 500000 );

for i = 1 : 1 : 5000

C2(i) = sum( C0(k2*(i-1)+1 : 1 : k2*i) );

i = i+1;

end

std_C1 = std(C1)

std_C2 = std(C2)

gain = C1./C2;

avg_gain = mean(gain);

std_gain = std(gain/avg_gain)Code解析

■ C0是由均值=1,σ=0.01的随机变量构成的矩阵

■ C1为样本数=5000的矩阵,C1的每个元素皆为任意10个C0元素之和。

■ C2为样本数=1000的矩阵,C2的每个元素皆为任意20个C0元素之和。

■ C1的理论均值=10,理论标准差=sqrt(10)*σ=0.0316

■ C2的理论均值=20,理论标准差=sqrt(20)*σ=0.0447

■ C1/C2的理论均值=0.5,理论上的相对标准差=sqrt(1/10+1/20)*σ=0.003873

三、电容失配对CDAC线性度的影响

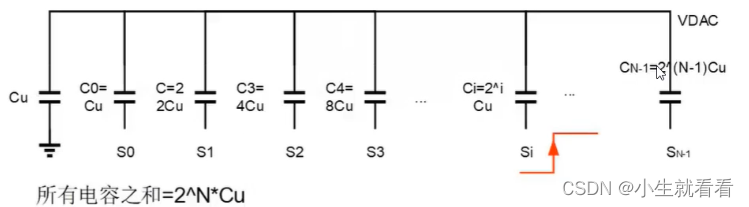

理想电容阵列

■ CDAC各个电容理想:Ci = 2^i *Cu

■ CDAC阵列电容之和:2^N *Cu

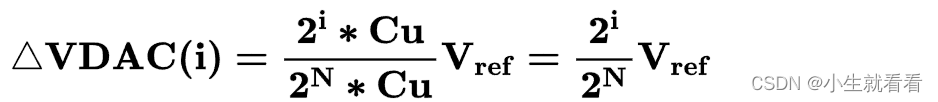

■ 第 i 位电容对应的VDAC输出:

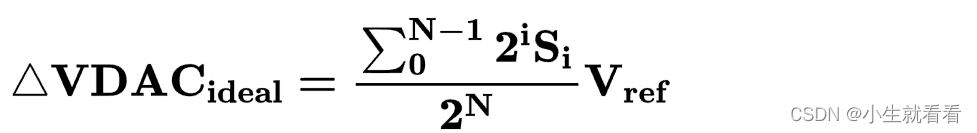

■ 总的VDAC输出:

实际带Mismatch的电容阵列

■ CDAC各个电容存在失配:Ci = 2^i *Cu + σi ==》 式子中的 σi = sqrt(2^i) *Cu

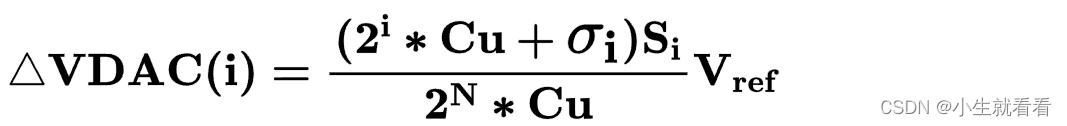

■ 第 i 位电容对应的VDAC输出:

■ 总的VDAC输出:

![]()

■ VDAC的模拟误差:

![]()

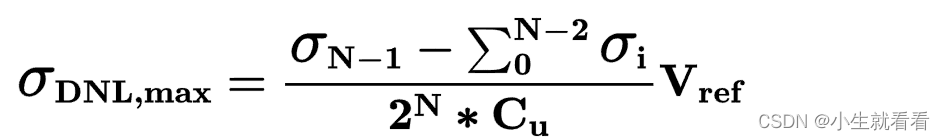

对DNL的影响:

![]()

最大的DNL发生在 011……1 变为 100…… 0 的时候,即每一个code都发生了跳变。

DNL定义:当前code宽度 - 前一个code宽度 - LSB

DNL = △VDAC(100......0) - △VDAC(011......1) - LSB

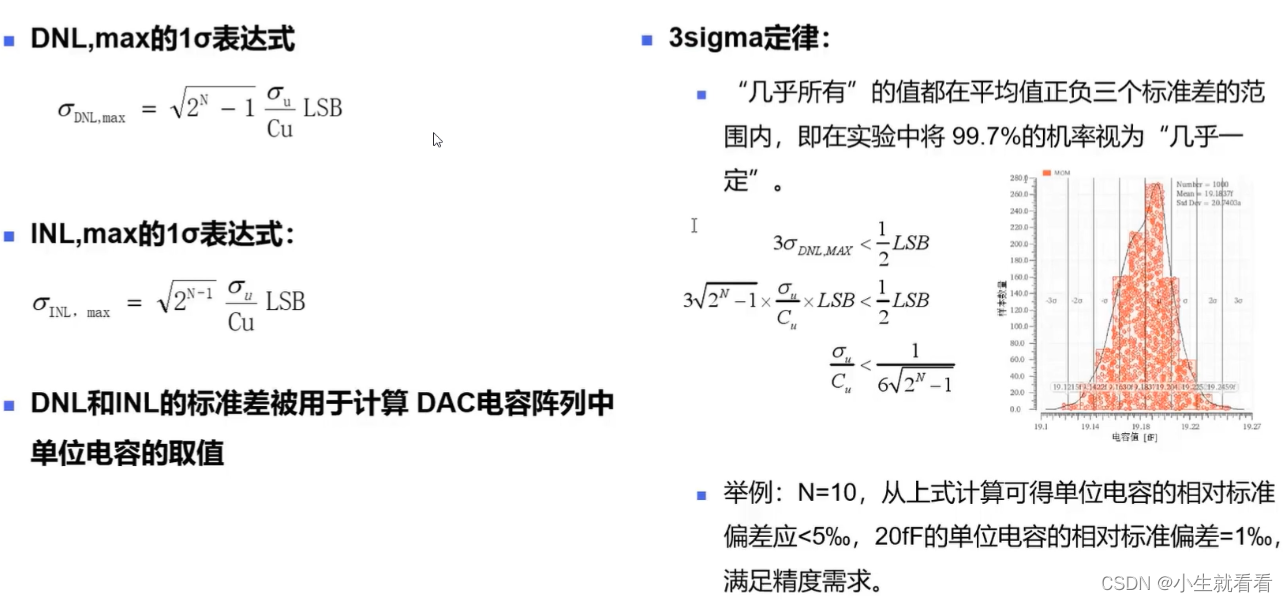

先求 D( σDNL,max ) 方差,再开方得到标准差:

![]()

DNL定量计算公式

结论:单位电容的相对标准偏差直接影响 DNL,max 的标准偏差,所以需要注意DAC中单位电容的匹配度

例如,给了位数N,给了单位电容相对标准差,就可以计算DNL,max 的标准偏差σ

假设要求 3倍DNL,max 的标准偏差σ(DNL99%落在此区间)为 xxLSB,就可以计算单位电容的相对标准差的要求。

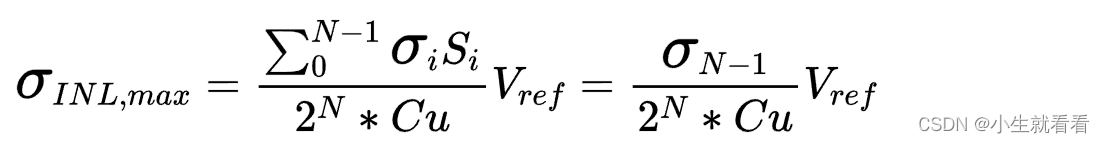

对INL的影响

VDAC模拟误差表达式:(INL为实际跳变值和理论跳变值求差)

![]()

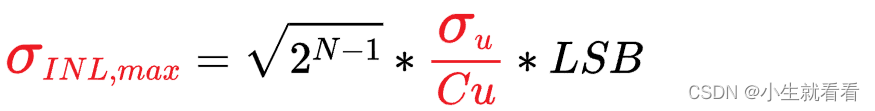

INL的最大值也发生在code = 100......00 处,即 i = N-1 时

此时 INL,max 的 σ 表达式:

INL,max 的方差:

得到的INL,max的标准差:

四、总结:单位电容的取值

文章探讨了电容失配对CDAC(电容数字-to-模拟转换器)线性度的影响,包括单个电容和多个电容比例的随机失配,以及其在Matlab中的验证。通过方差和标准偏差的概念,计算了电容失配导致的DNL(差分非线性)和INL(积分非线性)的量化影响,强调单位电容的匹配度对DNL和INL标准偏差的重要性。

文章探讨了电容失配对CDAC(电容数字-to-模拟转换器)线性度的影响,包括单个电容和多个电容比例的随机失配,以及其在Matlab中的验证。通过方差和标准偏差的概念,计算了电容失配导致的DNL(差分非线性)和INL(积分非线性)的量化影响,强调单位电容的匹配度对DNL和INL标准偏差的重要性。

1678

1678

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?