目录

一、综述

二乘二取二架构的优点是可以从两套设备,每套设备有两路通道同时采集(可以是异构)

采集的实时信息中进行比对和表决,最后从2组中取一组数据与另一套设备表决出的一组数据进行同步得到最后的结果(简写为2X2O2)

这一思路在轨道交通行业应用较为成熟,主要分为两个方面来扼要概括,实时性和通信,但是其通过数据表决来保证数据完整的方法可以应用在很多设计和领域中,故在此简单发表下我结合实际工作经验总结提炼的一些重要思路和经验

1、概念

“二乘二取二” 是一种在铁路信号等安全相关系统中广泛应用的冗余技术和表决机制。“二乘” 指双套独立冗余系统,每套系统里有两个独立的通道或单元,所以一共有四个独立系统或单元,“二取二” 是指这两个通道或单元的输出结果需要同时满足一定条件(比如两个结果相同)才能被系统所采纳或者输出。(这里简单了解下即可)

(PS:本人经常记混,也记不住,后来在看C++的相关书籍时想到一个记忆方法很有效,分享一下:指针章节中指针操作符*和取址操作符&的区别:

*p可以抽象理解一个动作,是取出数据

&p抽象为一个名词,是数据地址,一个地址

一个动词,一个名词,这样一下就可以轻松记住!

同理,二乘的符号2X,抽象成x2,就是双份,备份的意思

二取,抽象成取二,取自于两个通道同时满足才可以输出)

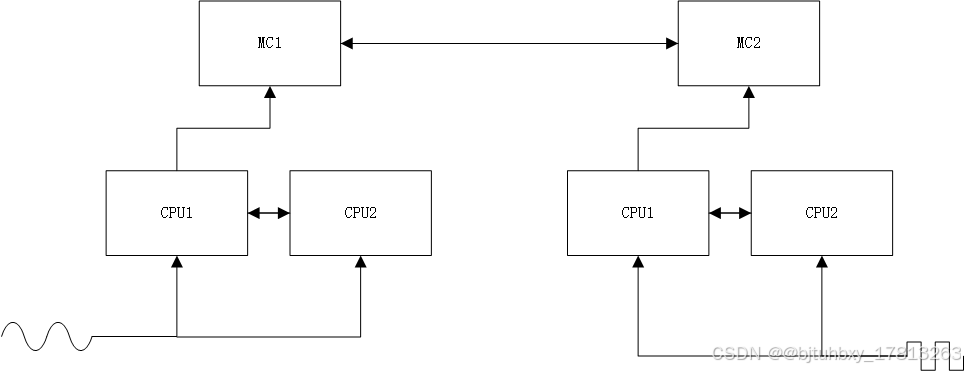

2、2X2O2工作流程介绍

在介绍这两个方面前,先介绍下2X2O2的完整流程,如图一所示,先说左半部分,两个CPU分别对同一信号采集(注意:硬件板卡上要设计两个独立的采集通道分别连接两个CPU的采集通道,这个硬件通道可以选择异构,这样更好)

两个CPU通过高速串口将采集的数据进行同步、表决(为了确保数据完整性要增加CRC校验,增加两种最好,CPU1和CPU2各自使用一套CRC来校验)

数据表决一致后,CPU1将数据上传到MC1(MC1也是一个CPU处理单元),右半部分同上

这样,MC1和MC2之间通过CANFD通信,将数据同步、表决,最后得到一组数据

重要的是,以上所有的数据过程都是有严格的周期性和实时性的,比如CPU1和CPU2要在10毫秒内完成所有数据的采集,在1毫秒内完成数据同步,1毫秒内完成数据表决,1毫秒内完成数据处理(表决一致则上传MC1,表决不一致则丢弃数据或者其他处理)等等步骤,这些步骤都有严格的执行时间和顺序,不能超时也不能跳步骤或者颠倒步骤顺序,(CPU1和CPU2之间通信可以不增加发送序列号和接收序列号,但是要增加通信超时判断和硬线反转)

MC1和CPU1之间也有通信机制,每个周期都要通信,有什么数据就传什么数据,且要更新发送报文序列号和接受报文序列号,确保发送连续和接受连续

MC1和MC2之间也要进行周期通信,且需要增加发送序列号和接收序列号,MC1和MC2之间要增加硬线反转

再补一点,两个MC,是可以作为主备系,工作时只有一个为主系,另一个跟随为备系,主系宕机时立即升主,继续工作。(这部分暂不介绍)

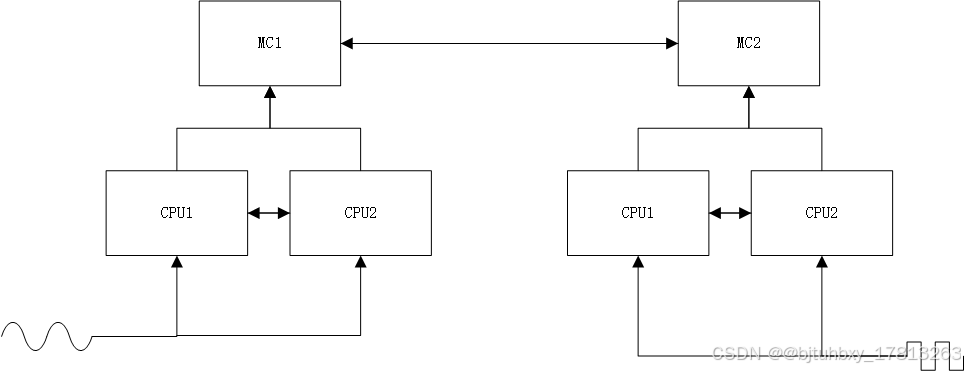

图二和图一不同的是,CPU2增加了与MC1之间的CANFD通信可以不增加,也可以增加后不使用,预留。也可以增加通信机制,使用该通信通道

以上就是2X2O2的工作流程简要介绍,其中比较重要的是通信和实时性

对于2X2O2应用方面的一些思考?有哪些价值和借鉴硬件?

1)双CPU架构是具有独特性的,双CPU采集和表决设计确保采集的准确性无疑要比单CPU要可靠,比如一些工业上对模拟量和数字量的采集,可以增加双CPU来使产品更加的可靠

2)CPU与MC之间的通信时效及通信机制,确保数据传输过程中的时效性和完整性,报文收发序列号的设计,CRC校验的设计,通信超时的设计,都提供了一种数据通信和传输的参考思路,以后做一些产品和设计,都可以拿来借鉴,在满足正常通信的同时,能够更加的使通信链路可靠

3)MC之间的通信和数据表决,在一系宕机时,另一系可以立即工作,这一设计原本是为了保证地铁设备工作时能够不间断的处于安全控制状态,但是这个机制很完美的给我们提供了一个系统可靠不间断工作的思路,比如一些重要场合要求设备不能宕机,或者设备宕机会造成重大损失的场合时,可以考虑该设计思路,一系宕机另一系立即工作。

(这里是本人的粗浅总结,也不完善,欢迎大佬和有想法的小伙伴评论留言~)

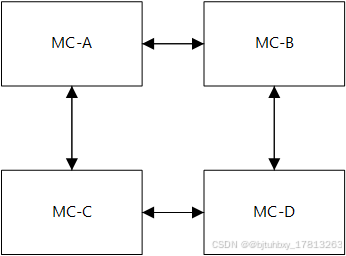

二、主控MC间通信

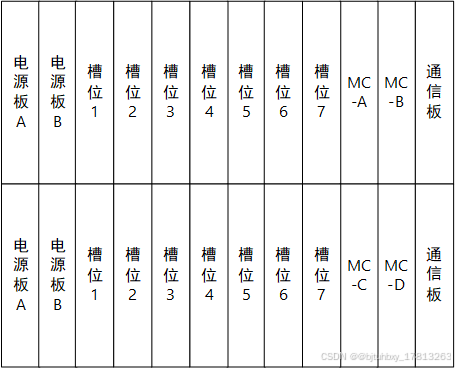

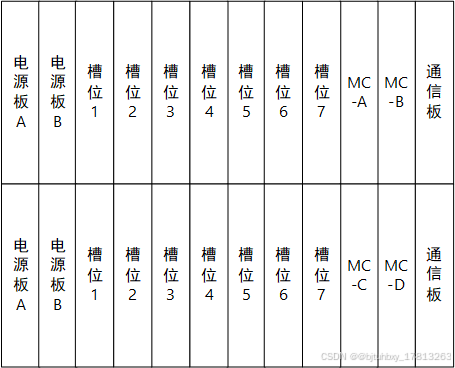

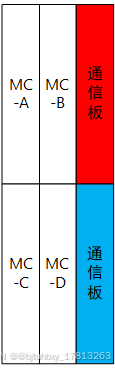

6U插箱机笼,分为上下两层,每一层为3U,MC-A和MC-B为单独一系,MC-C和MC-D为单独一系,默认上层称为I系,下层称为II系

通信设计为系内通信和系间通信,系内是A和B,C和D

系间是A和C,B和D

系间是同步,系内是表决。

(这里如果很抽象晦涩,没关系,混个眼熟即可,下面会展开讲解)

三、周期同步

周期同步属于实时性要保证的范围,双CPU之间要在保证同步进行工作处理,采用信号翻转的方式来同步周期,硬件设计可以采用两根IO进行直连,每个CPU控制分别一个IO。周期同步保证了双CPU的工作周期开始时间和结束时间几乎都是一起的,对于处理外界输入进来的一个数据,可以保证双CPU是同时处理,同时对该处理结果进行表决,增加处理结果的可靠性,这种双CPU处理的思路方式有个名词叫:“二取”或者“二取二”

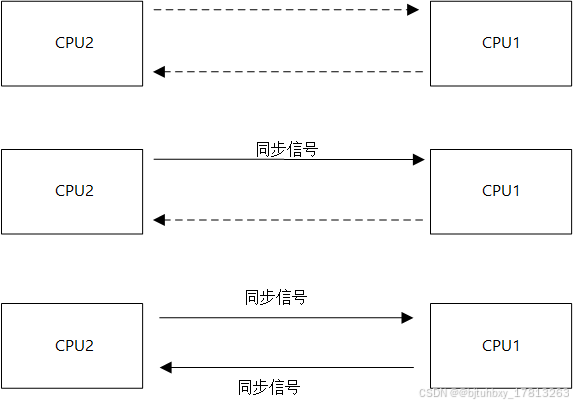

下图来描述同步逻辑,虚线表示未发送翻转信号且被箭头所指的CPU正在检测该信号,实线表示发送了翻转信号且被箭头所指的CPU检测到该信号

第一步:CPU2和CPU1都处于检测对方的翻转信号状态中

第二步:CPU2发送同步信号,此时CPU1接收到同步信号

第三步:CPU1接收到同步信号后,控制另外一个IO发送同步信号,CPU2收到同步信号

第四步:复位信号,进入下一周期

最后完成同步,将同步标志位置位,两个CPU同时进入下一个周期

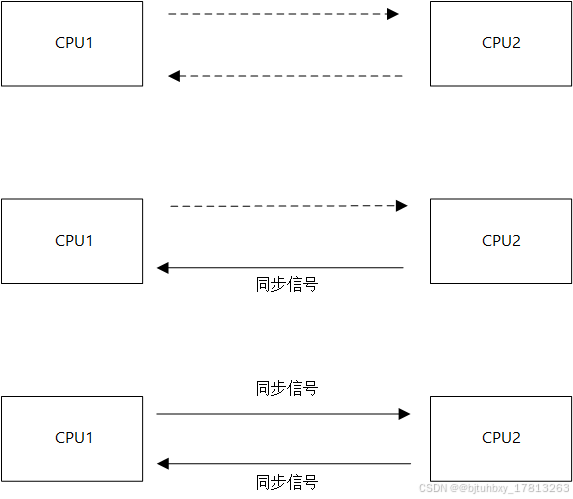

下图是以CPU1的视角来描述同步信号(都是在一个函数内实现的)

第一步:CPU2和CPU1都处于检测对方的翻转信号状态中

第二步:CPU1接收到CPU2发送的同步信号

第三步:CPU1接收到同步信号后,控制另外一个IO发送同步信号,CPU2收到同步信号

第四步:复位信号,进入下一周期

补充一些:

1)结合硬件实现方法来总结,周期翻转还使用到了硬线翻转的思路,以上的信号引脚使用两个GPIO直连,通过控制GPIO输出高低电平来传递同步信号

2)同步信号功能在周期结束末尾来调用

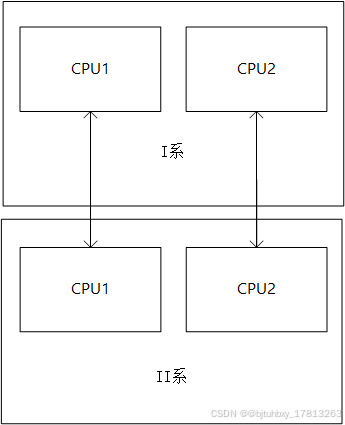

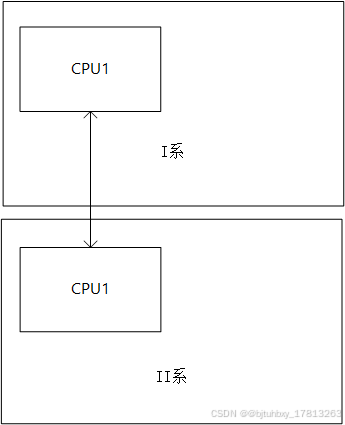

四、双系、2乘2取2及2乘

下图是2XX2OO2(2乘2取2,为方便用符号代替),注意一点,I系是6U机笼里对应上一层的板卡(3U),两个槽位的两块CPU板卡

II系是机笼里下面一层的板卡(3U),占两个槽位的两块CPU板卡

一个6U机笼分上下两层,一层3U

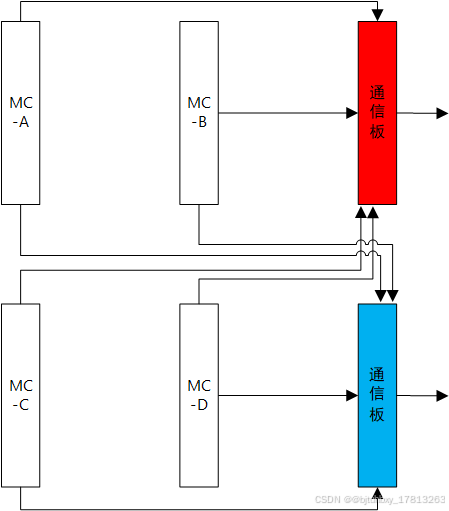

下图只画出来系间通信,系间通信为以太网,走机笼背板

下图是2XX2,简单来看就是,两系分别去掉一块主控板,系间通信还有,但是系内通信,系内表决去掉,从代码实现上变为简单,但是防护等级下降,各有取舍

这里再放一张机笼示意图,结合上面的网络链路关系,方便理解,上面是抽象出来的关系图,下面是具体应用的案例

五、TCP协议、UDP协议

2xx2oo2是系统是支持TCP协议和UDP协议的,在这里引入红蓝网,也叫做双网冗余

(没错,轨道安全产品,一般喜欢有冗余设计,供电电源冗余,执行单元冗余,处理单元冗余,网络冗余等等......但不是简单的加个备份就是所谓的‘安全’了,如何处理冗余单元间的运行关系,协调任务等是个需要深思熟虑的问题)

把机笼图拆出来,并以颜色区分,如下图所示

再加上网络通信连接图

综上所示,每个板卡也就是每个CPU分别连接到红网,蓝网,也就是通信板,一块通信板也就是承担红蓝网的功能

主控板和外界设备间使用通信板作为间隔,并且设计双网冗余(红蓝)

通信板功能:主控可以将相当一部分的外界的通信任务放到通信板来做,通信板可以做成非安功能,仅把通信板当作一个通信模块不承担安全功能

外界的大量以太网数据报文,在通信板处理,通信板可以过一遍协议,再将有用的信息摘出来,再进行攒包,拼包最后发给主控

分担一部分主控的数据处理开销,通信板攒包可以降低主控的网络开销

主控板控制指令下发时,可以制定协议,通信板根据协议解析指令,执行一些通信任务

通信板可以接多个设备,主控板使用一个网口即可控制多个设备

存储网络通信日志,设计有RTC时钟校时(这是两个是附加功能)

从设备和通信板间的协议支持UDP和TCP来完成,通信板使用Linux系统,可以很好的支持这两种协议,方便开发和调试周期,主控板使用Vxworks系统,与通信板通信使用UDP网络加安全通信协议即可

————————————————————PS—————————————————————

写的很随意,欢迎大家留言讨论

如果有时间我会再次更新、完善

7710

7710

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?