摘要

本文记录了笔者调试采样率125Msps的某款ADC时遇到的各种现象和解决方法,希望能帮到看到这篇文章的人。主要是讲一下和FPGA接口的各种问题。主要分为2大类:时序问题;码制问题(反码和补码)。

类一:时序问题

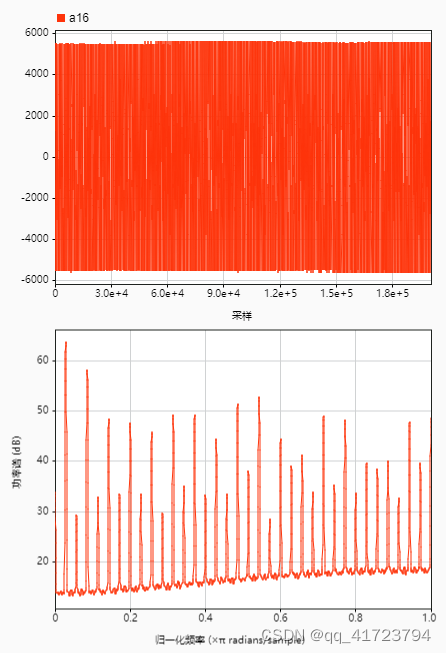

问题描述:我采样的波形十分难看,还有很多次谐波

波形图非常丑,而且可以看到过零处有大的突起

使用matlab分析可以看到上图全是各次谐波

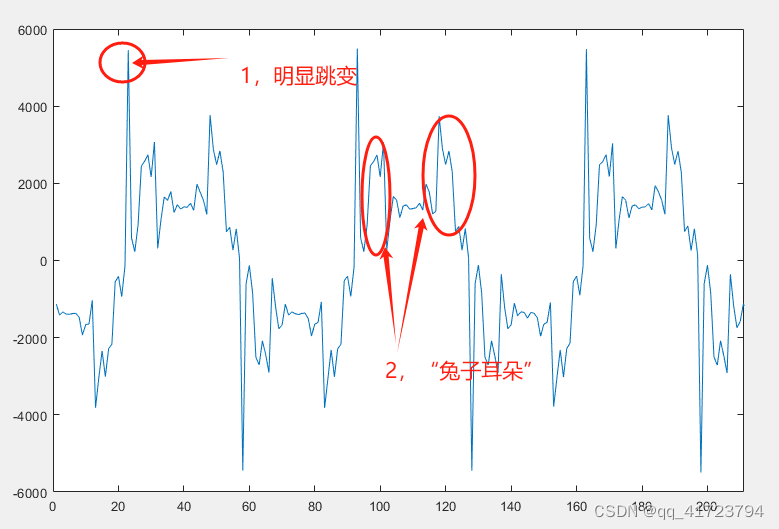

明显跳变

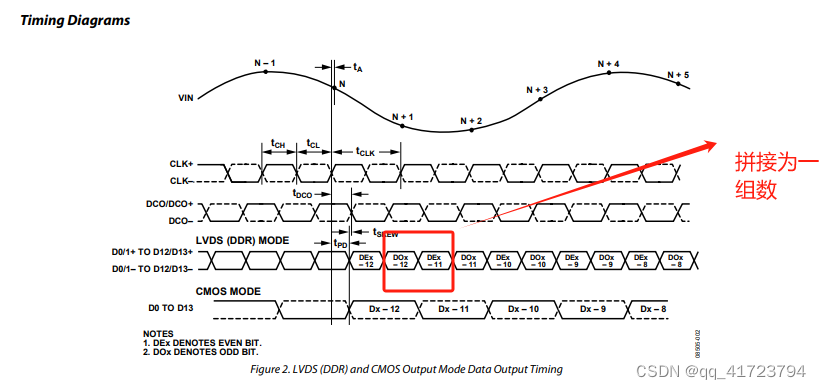

问题原因:ADC接口采用并行的DDR总线(不是指DDRx这类协议),上升沿和下降沿都带数据。但是拼接错误,前一个采样的上升沿(奇数位)和后一组采样的下降沿(偶数位),被拼接到一组数据中了。

“兔子耳朵”

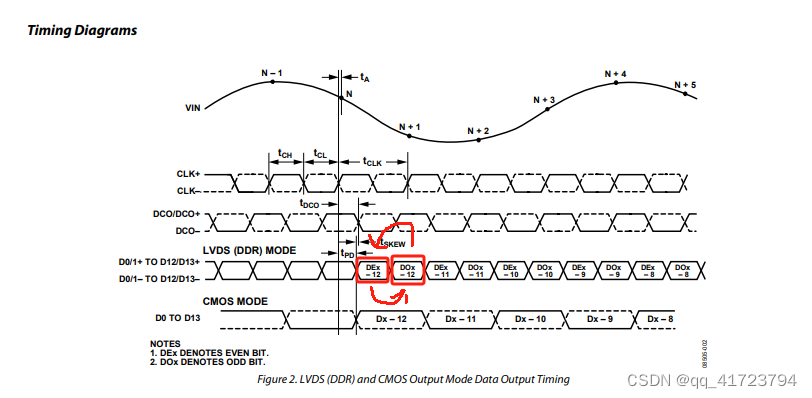

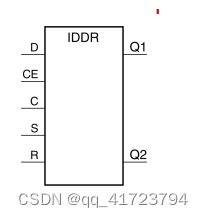

问题原因:奇数位和偶数位弄反了,笔者采用Xilinx IDDR原语设计FPGA和ADC的接口模块。Q1和Q2粗心接错偶数位还是奇数位了。。

不过多赘述,查看IDDR原语教程就说的很明确。

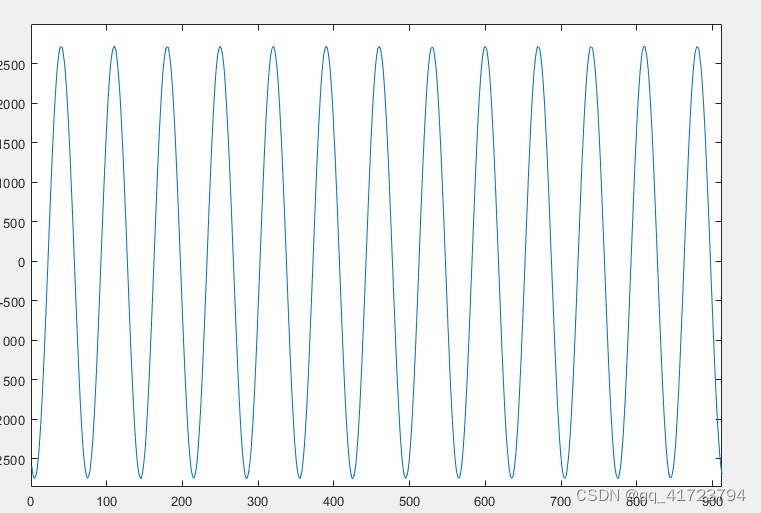

贴上我在matlab里修复过的,经过各种位运算总算修复了,下一步就是直接修复FPGA代码了。

类二:码制问题

波形对半劈开

这个我没图,但是你只要发现你的波形对半劈开了。。。就要考虑这个问题。我用的adc,可以传输补码(Twos Complement )和偏移码(Offset Binary)**将带符号二进制数的补码的符号位取反即得到偏移码 **

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?