复位的用途:ASIC做仿真时,需要强制ASIC进入一个可知态。通常ASIC中的每一个寄存器,不管系统是否需要复位,都应该时可复位的。在某些情况下,对于高速应用中的流水线(串行移位)寄存器,可以去掉复位,从而获得更高的性能。

寄存器的编码风格

每个Verilog过程块应该只模型一种寄存器

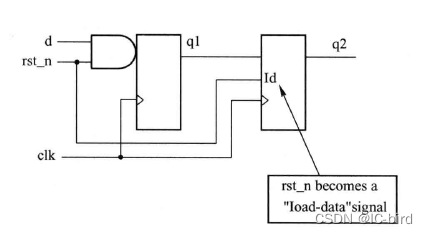

// 一个寄存器用于捕获数据,输出传送到一个跟随寄存器

// 第一部分使用了同步复位,第二部分包含了一个没有使用复位的跟随寄存器

// 因为一个过程块推导出两种寄存器,导致rst_n也被用到了跟随寄存器引脚

// Bad verilog coding style to module dissimilar flip_flops

module badFFstyle(

output reg q2,

input d, clk, rst_n);

reg q1;

always @ (posedge clk)

if(!rst_n) q1 <= 1'b0;

else begin

q1 <= d;

q2 <= q1;

end

endmodule

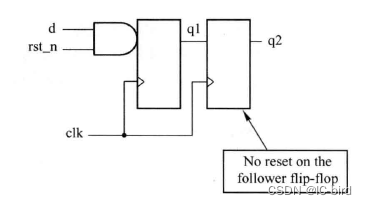

// 正确模型跟随寄存器的方法时用两个Verilog过程块

module goodFFstyle(

output reg q2,

input d, clk, rst_n);

always @ (posedge clk)

if(!rst_n) q1 <= 1'b0;

else q1 <= d;

always @ (posedge clk)

q2 <= q1;

endmodule

同步复位

同步复位前提:只有在时钟有效沿,复位信号才能影响寄存器的状态。复位信号通过把它作为组合逻辑的一部分输入到寄存器的输入端对寄存器起作用。

reset应该在if-else语句的最前面,以便优先考虑。

// 只有当复位信号没有放到敏感列表里时,寄存器才会被模型成同步复位寄存器

module sync_resetFFstyle(

output reg q,

input d, clk, rst_n);

always @ (posedge clk)

if(!rst_n) q <= 1'b0;

else q <= d;

endmodule

// synopsys sync_set_reset "rst_n"

// 用于告诉综合工具指定的信号时同步复位或同步置位,综合工具会把这个信号放到靠近寄存器位置

// hdlin_ff_always_sync_set_reset设为true 那么相当于每个模块加入// synopsys sync_set_reset同步复位优点

同步复位可以保证电路100%同步。通过时钟可以过滤掉复位信号上的小毛刺,但毛刺出现在时钟有效沿会出现亚稳态。

如果复位信号必须有一组内部条件产生,那么使用同步复位可以有效过滤掉逻辑表达式的毛刺。

通过让复位信号持续预定的周期数,在复位缓冲树中使用寄存器,就可以把复位缓冲树的时序限定在一个时钟周期内

同步复位缺点

同步复位可能需要脉冲拓展,以保证复位脉冲足够宽,从而保证在时钟有效沿复位信号的存在。可以使用一个小计数器,以保证度为脉冲保持一定数量的时钟周期

设计者必须仔细考虑仿真存在的问题

同步复位在复位电路时需要时钟正常工作(门控时钟)

异步复位

异步复位寄存器上有一个reset引脚,这个引脚一般是低电平有效,就是当这个引脚时低电平的时候,寄存器进入复位状态

// 复位信号必须放在敏感列表中

// 虽然复位信号实际时电平有效的,但是在模型异步复位寄存器时必须把它设计成前沿有效

// 综合工具要求如果敏感列表中某一个信号是沿敏感,那么所有在敏感列表中的信号都应该是沿敏感的

// 仿真工具没有以上要求

module async_resetFFstyle (

output reg q,

input d, clk, rst_n);

always @ (posedge clk or negedge rst_n)

if(!rst_n) q <= 1'b0;

else q <= d;

endmodule

// 如果复位信号直接由一个外部引脚驱动。一般使用 set_drive 0 命令

// 使用 set_dont_touch_network ,防止综合时修改这个线网

// 使用 set_ideal_net , 创建理想线网,不做任何优化

// set_diable_timing set false_path 获得干净的时序报告优点:

单元库里有异步复位寄存器,保证数据路径干净,对于时序紧张的设计,不能在承受同步复位插入的组合逻辑造成的延时

不管有没有时钟存在,电路都可以复位

不需要使用综合指令,综合工具就可以自动推导出带复位引脚的寄存器

缺点:

不能和基于cycle的仿真器一起工作

DFT器件必须禁止复位同步器出来的复位线网

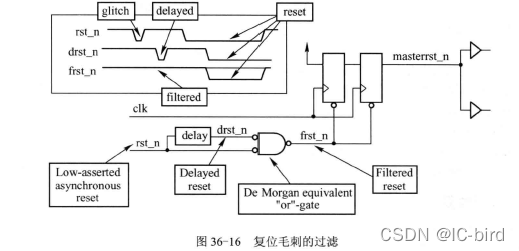

最大的问题时复位的起效和失效都是异步的,起效不是问题,异步复位的释放发生在时钟有效沿附近时,造成亚稳态

噪声容易造成假复位

异步复位问题

复位的释放到能导致芯片进入亚稳态,复位的撤销对不同的寄存器发生在不同的时钟周期

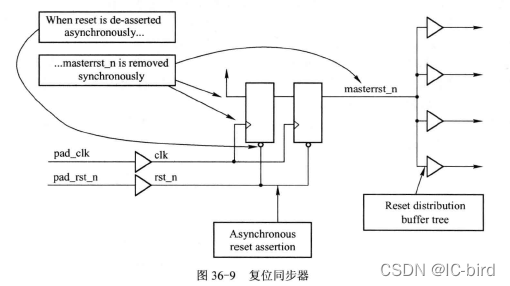

复位同步器

// 需要两级寄存器同步信号,因为复位信号时异步撤销的,在靠近时钟上升沿复位的撤离可能或导致亚稳态

// 第二个寄存器时用来消除亚稳态

// 同步器必须从扫描链中清除掉

module async_resetFFstyle(

output reg rst_n,

input clk, asyncrst_n);

reg rff1;

always @ (posedge clk or negedge asyncrst_n)

if(!asyncrst_n) {rst_n, rff1} <= 2'b0;

else {rst_n, rff1} <= {rff1,1'b1};

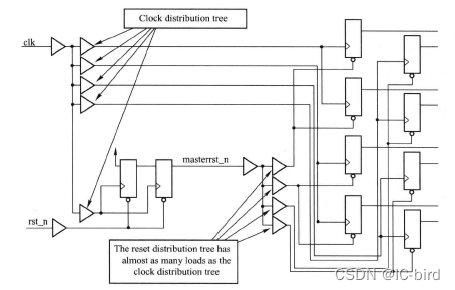

endmodule复位分布树

分布复位之间的偏差(Skew)近似平衡即可,不需要向时钟那么严格、

3360

3360

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?