系列文章目录

芯动力——硬件加速设计方法学习笔记(第一章)概述

芯动力——硬件加速设计方法学习笔记(第二章)高质量VerilogHDL描述方法(1)(常见语法对应硬件结构)

芯动力——硬件加速设计方法学习笔记(第二章)高质量VerilogHDL描述方法(2)(考虑面积、功耗、时延等)

芯动力——硬件加速设计方法学习笔记(第二章)高质量VerilogHDL描述方法(3)(RTL设计指导原则)

文章目录

前言

打卡学习第四天,坚持就是胜利!

2023.4.4

一、时钟

| 时钟频率 | 时钟周期 |

|---|---|

| 1 Hz | 1 s |

| 1 KHz | 1 ms |

| 1 MHz | 1 us |

| 1 GHz | 1 ns |

1、时钟分类

三个因素:时钟源、频率、相位

同步时钟:同源、频率整数比、固定相位差(可以理解为同源时钟路径不同造成的偏移)

异步时钟:任一条件不满足就是异步时钟

-

同一个PLL(锁相环)出来的两个时钟相位和频率是可控的,他们属于同步时钟;不同锁相环出来的两个时钟是异步时钟。

-

数据从慢时钟域到快时钟域:增加逻辑使得只采样一次信号

数据从快时钟域到慢时钟域:数据至少保持一个目标时钟周期,否则慢时钟域会采样不到信号

2、时钟参数

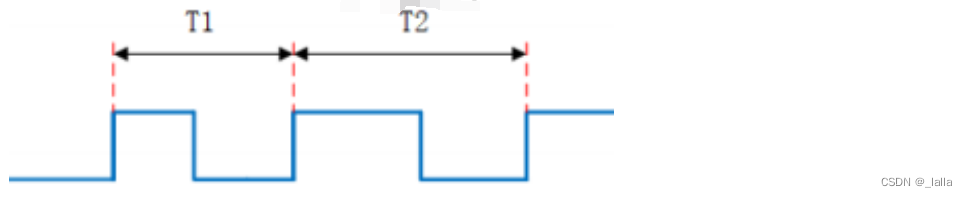

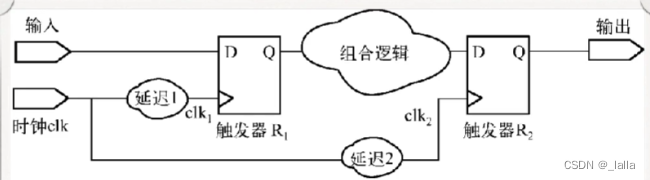

(1)时钟抖动:Jitter,两个时钟周期之间存在差值,时钟频率不确定,平均值为0。

主要受外界干扰引起,与晶振、电源以及温度等相关

clock jitter = T2 - T1

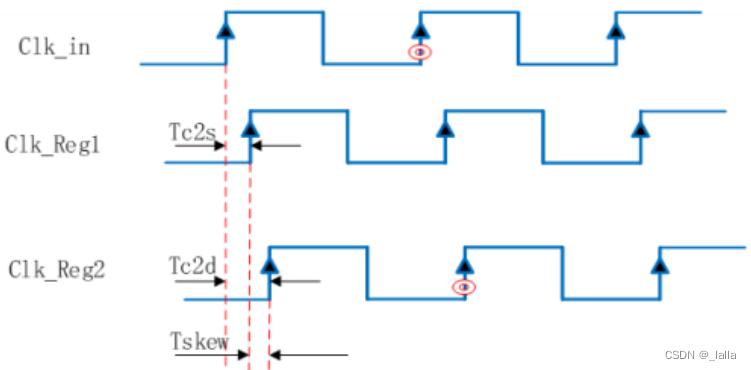

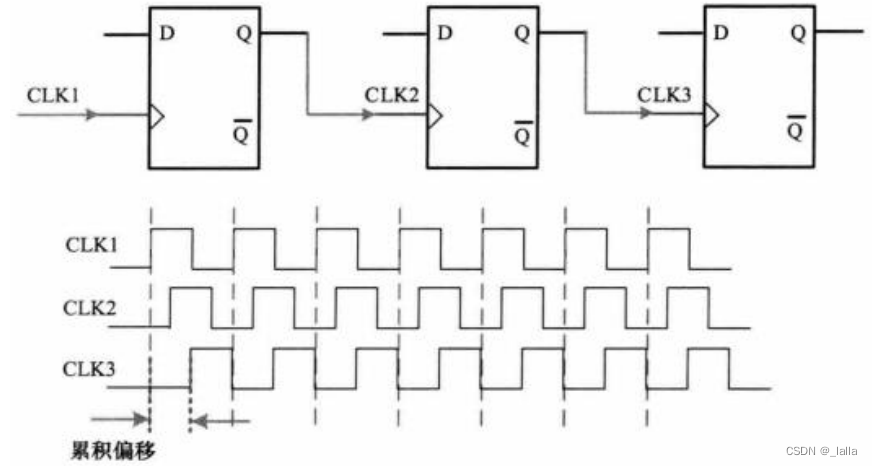

(2)时钟偏移:skew,由于同样的时钟源达到不同寄存器的路径不同,因而延时不同,导致相位不确定。

skew = 最长时钟路径延时 - 最短时钟路径延时

(3)转移时间:Transition,时钟从0到1,1到0的时钟

(4)占空比:duty cycle

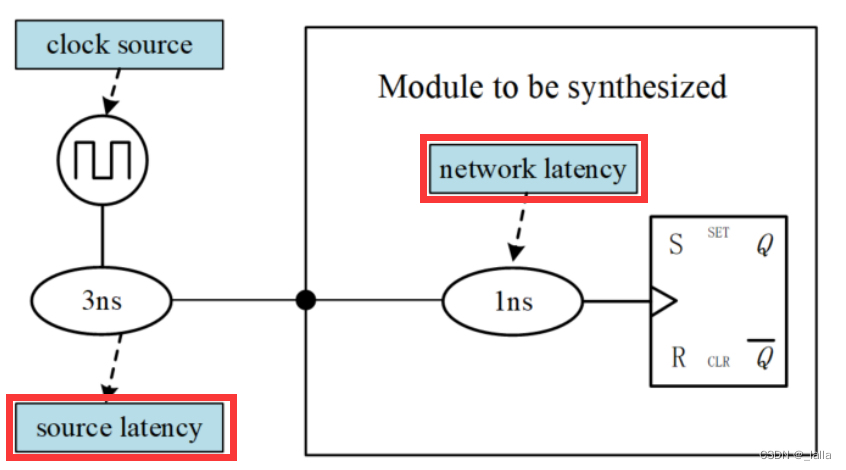

(5)时钟延时:Latency,时钟从时钟源(如晶振、PLL或分频器输出端)出发达到触发器端口的延迟时间

时钟延时 = 时钟源延时source latency + 时钟网络延时 network latency

时钟源延时:时钟信号从时钟源原点达到设计模块时钟定义点的传输时间

时钟网络延时:从设计模块时钟定义点到模块内部触发器时钟端的传输时间,可能就是时钟缓冲器的时间

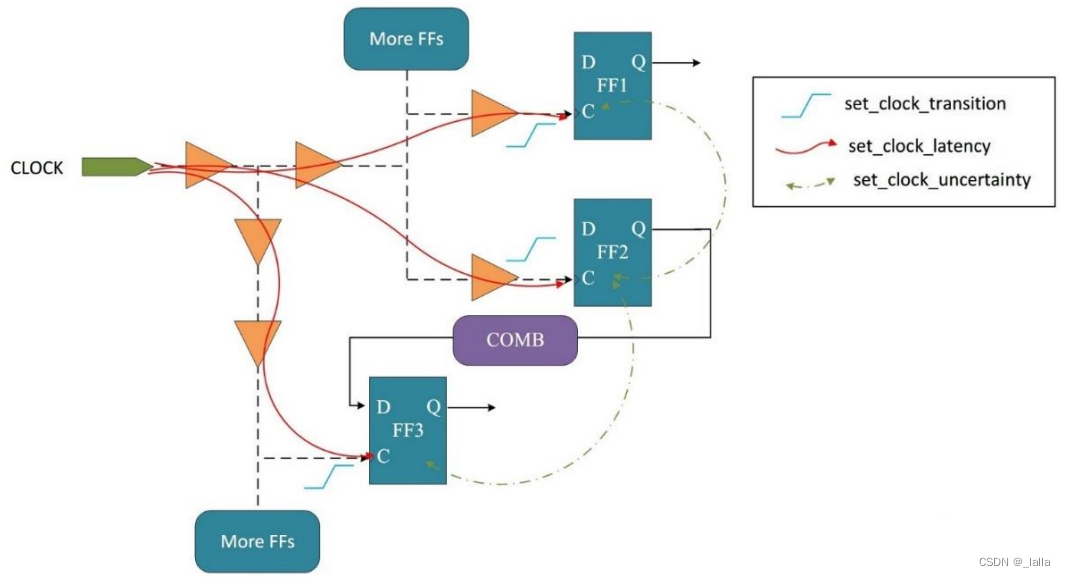

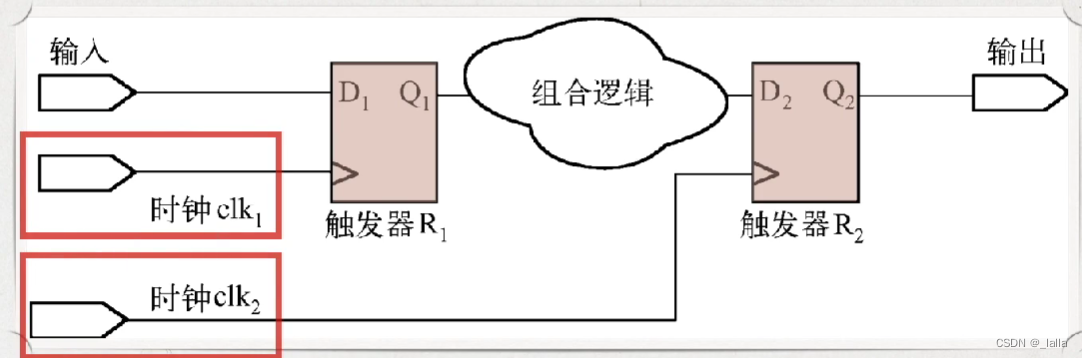

3、时钟树

对时钟进行布线,使得每个寄存器的时钟相位是相同的。 不是减小时钟信号达到触发器的时间,而是缩小各个触发器之间的时间差异。

时钟树:是由多个缓冲单元(buffer cell)搭建的网状结构

clock latency:时钟树的总延时

clock skew:寄存器之间的相位差

绿色虚线表示时间不确定度:包括时钟偏移和时钟抖动

4、时钟设计方案

(1)外部时钟源:RC/LC振荡电路、有源/无源晶体振荡器(石英晶体的压电效应)

(2)内部时钟源:PLL锁相环(稳定且高频的时钟)

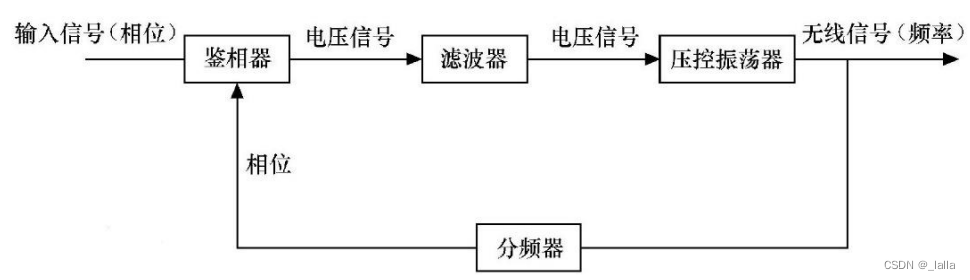

PLL:phase locked loop,反馈控制电路,锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

(3)时钟分频:使用同步计数器或状态机

5、时钟切换电路

低功耗模式下降频,提高计算能力时升频。

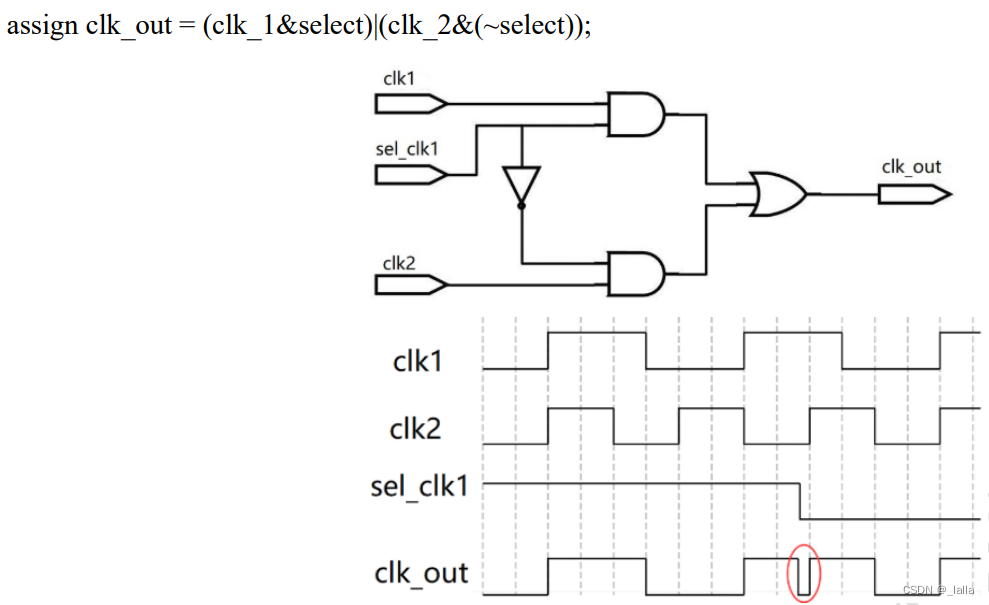

使用组合逻辑电路切换容易产生毛刺。在电平相反时切换,肯定产生毛刺。

建议在同为低电平期间切换,避免毛刺产生。

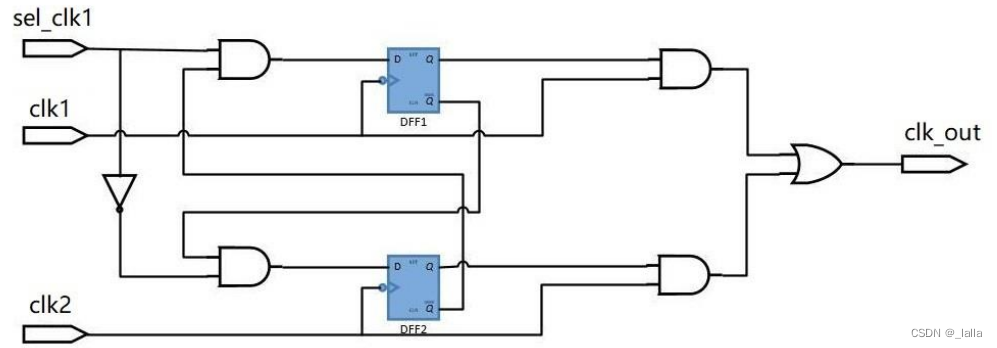

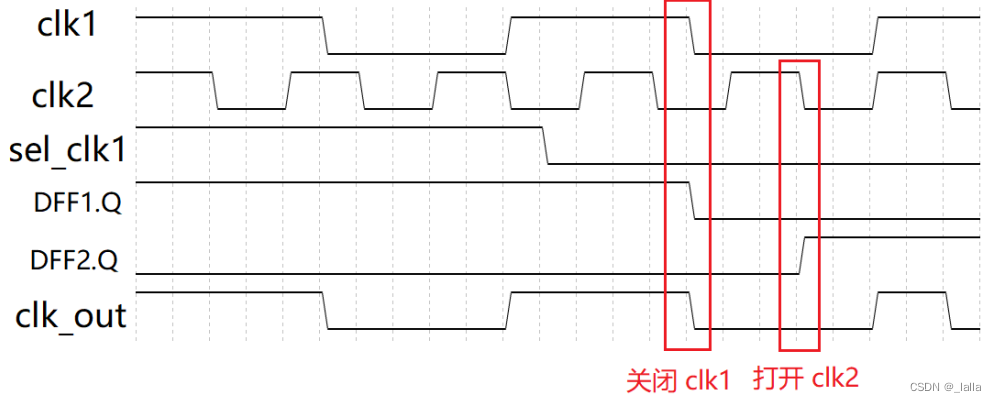

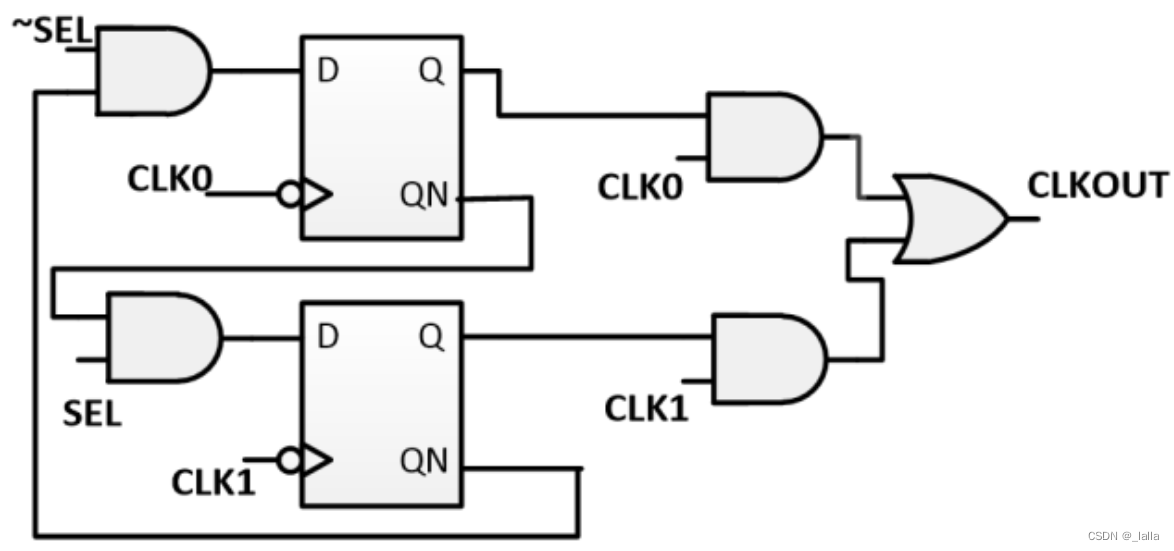

5.1 同步时钟切换电路

glitch-free clock switching

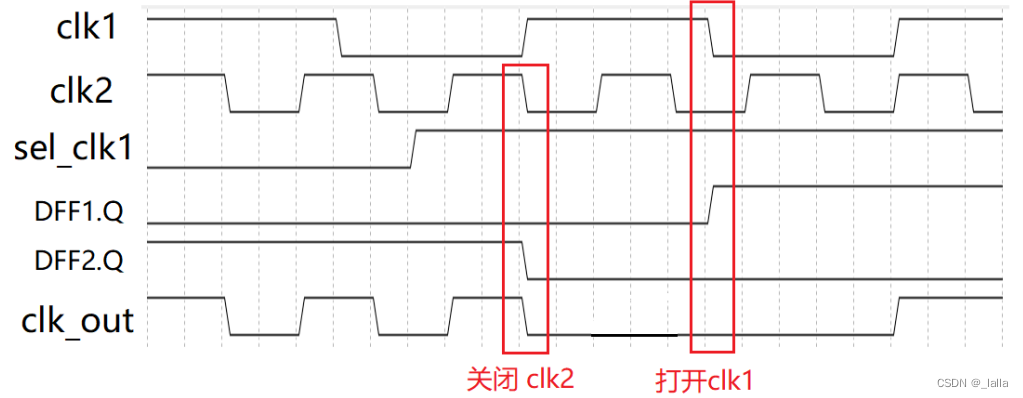

利用时钟下降沿对选择信号进行缓存,同时一个时钟选择信号对另外一个时钟进行反馈,保证任意时刻只有一个时钟有效。

变化过程:首先sel=1,下半部分无效(因为sel取反为0,寄存过去肯定也是0),clk1有效。

当sel由1到0时,首先变化的是DFF1,DFF1的 ~ Q变为1,反馈使得开始寄存~ sel的值,clk2开始有效。

在两个时钟周期切换之间,sel信号都为低电平,输出为0。

先关闭前面时钟,再打开下一个时钟。

verilog代码:

module clock_swithching(

input clk_a,

input clk_b,

input rst_n,

input sel,

output clk_out

);

reg out_a, out_b;

assign clk_out = (out_a & clk_a) | (out_b & clk_b);

//注意是时钟下降沿采样

always@(negedge clk_a or negedge rst_n)begin

if(!rst_n)

out_a <= 0;

else

out_a <= sel & ~out_b;

end

always@(negedge clk_b or negedge rst_n)begin

if(!rst_n)

out_b <= 0;

else

out_b <= ~sel & ~out_a;

end

endmodule

简单的画法:

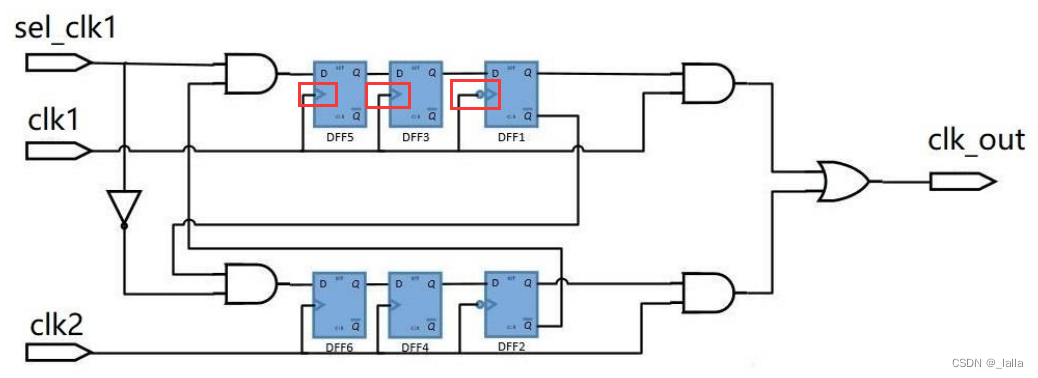

5.2 异步时钟切换电路

如果sel相对于两个时钟是完全异步的,会可能产生亚稳态。

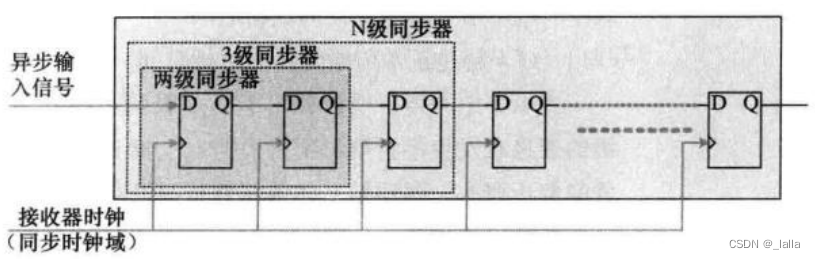

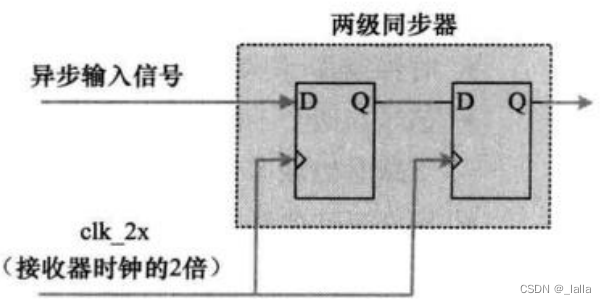

把单个FF换成两级或者三级同步器,减少亚稳态的传播。

//代码是一级同步器的情况

module clock_swithching(

input clk_a,

input clk_b,

input rst_n,

input sel,

output clk_out

);

reg out_a, out_b, out_a_r, out_b_r;

assign clk_out = (out_a & clk_a_r) | (out_b & clk_b_r);

//注意是时钟上升沿同步

always@(posedge clk_a or negedge rst_n)begin

if(!rst_n)

out_a <= 0;

else

out_a <= sel & ~out_b_r;

end

//下降沿采样选择信号

always@(negedge clk_a or negedge rst_n)begin

if(!rst_n)

out_a_r <= 0;

else

out_a_r <= out_a;

end

always@(posedge clk_b or negedge rst_n)begin

if(!rst_n)

out_b <= 0;

else

out_b <= ~sel & ~out_a_r;

end

always@(negedge clk_b or negedge rst_n)begin

if(!rst_n)

out_b_r <= 0;

else

out_b_r <= out_b;

end

endmodule

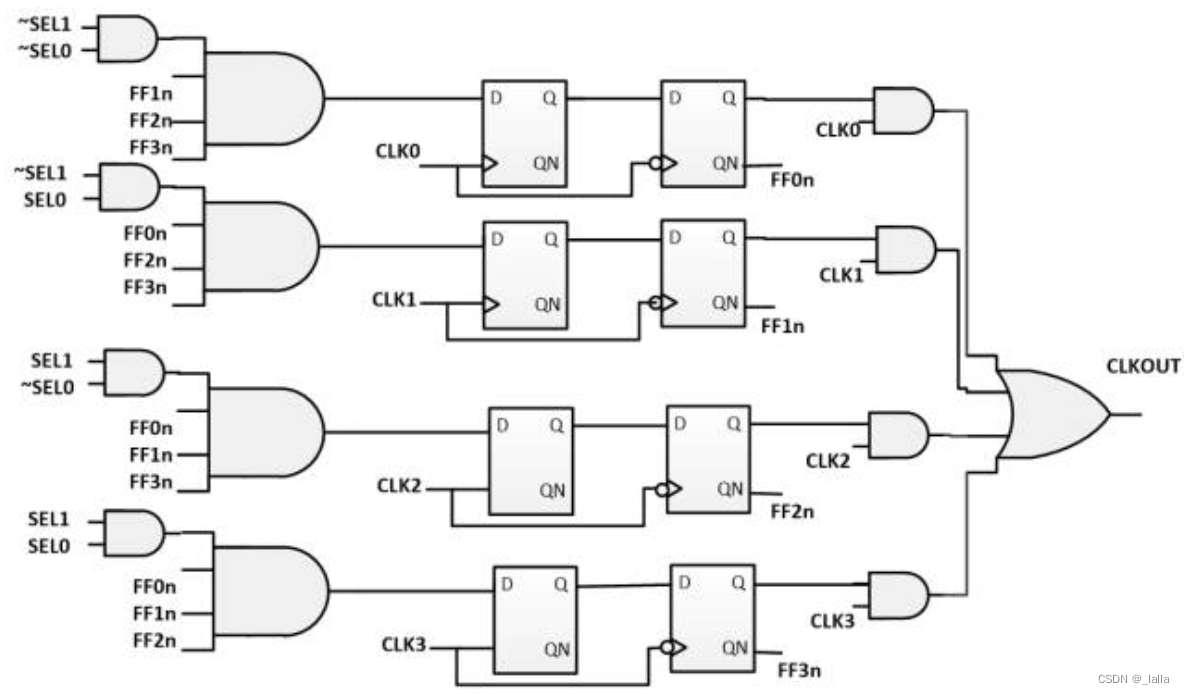

5.3 多路时钟切换

6、行波时钟

定义:由寄存器分频产生的时钟,常用行波计数器对时钟进行幂为2的分频,与其他同步计数器相比,行波计数器使用的门数更少。但是不建议使用,会产生新的时钟域。

7、双边沿时钟

在时钟上升沿和下降沿都传输数据,得到双倍吞吐率。

优势:降低功耗、提高吞吐率

二、同步电路和异步电路

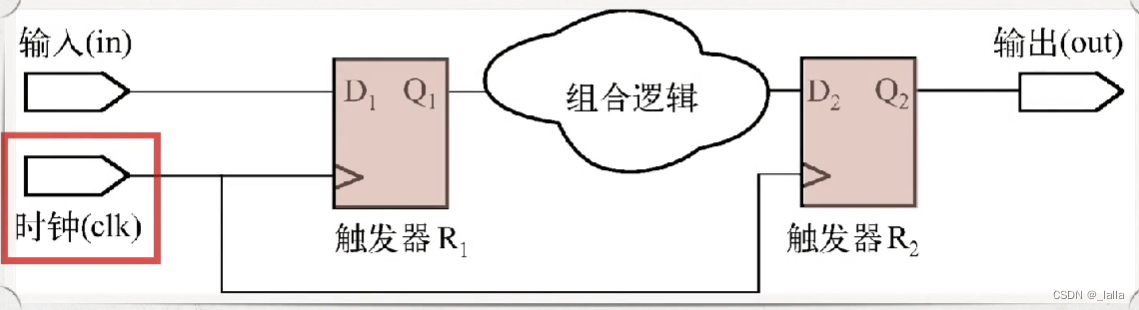

1、同步电路定义

即电路中的所有受时钟控制的单元(触发器、寄存器),全部由一个统一的全局时钟控制

2、同步电路优点和缺点

优点:

- EDA工具可以保证电路的时序收敛,有效避免了电路设计中竞争冒险现象

- 由于触发器在时钟边缘才改变,很大程度上减小了整个电路受到毛刺和噪声的影响

缺点:

- 由于是一个全局时钟,所以需要构建时钟网络/时钟树。

- 触发器距离时钟的远近距离造成了时钟偏移和时钟抖动等

- 同时缓冲器的存在使得芯片面积和功耗增加

3、异步电路定义

区别:电路的数据传输可以在任意时刻发生,电路中没有一个全局或局部的控制时钟

4、异步电路优缺点

优点:

- 没有时钟偏移等问题

- 模块化特性突出,异步电路需要用握手信号进行模块间的通信,模块连接后不会受到内部延时的影响

- 对信号的延迟不敏感

- 有潜在的高性能特性

- 低功耗,异步电路由数据驱动,仅在需要处理数据时消耗能量

- 好的电磁兼容性

缺点:

- 设计复杂

- 缺乏相应的EDA工具的支持

三、同步复位和异步复位

目的:使电路进入一个稳定操作的状态。

时序逻辑需要复位,组合逻辑不需要。

数据信号一般不需要复位,控制信号需要复位。

1、同步复位

复位信号在时钟信号有效沿来时才复位

问题:综合工具可能无法区分复位信号和其他信号

always @ (posedge clk) begin

if (!rst_n)

data_out <= 1'b0;

else

data_out <= data_in;

end

2、异步复位

复位信号优先级很高,有效时就直接复位

建议rst的下降沿,因为上电时信号是低电平,低电平更容易检测

always @ (posedge clk or negedge rst_n)

if (!rst_n)

data_out <= 1'b0;

else

data_out <= data_in;

3、同步复位和异步复位优缺点比较

| 同步复位 | 异步复位 |

|---|---|

| 有利于时序分析和仿真 | 大多数目标库内有异步复位端口,节约逻辑资源 |

| 过滤掉复位毛刺 | 设计相对简单 |

| 电路100%同步,消除了亚稳态的影响 | 信号容易识别 |

| 缺点 | 缺点 |

| 大多数目标库内没有同步复位端口,因而会消耗更多的逻辑资源 | 复位信号容易受到毛刺影响 |

| 复位信号的有效时长必须大于时钟周期,才能被采样 | 如果在时钟沿附近释放,可能会造成亚稳态 |

| 复位信号和其他信号难以识别,需要指定 | 抗干扰能力差 |

4、异步复位同步释放

synchronized asynchronous reset

目的:防止异步复位信号 release 释放时出现亚稳态现象

复位信号来临的时候不受时钟信号的同步,复位信号释放的时候受到时钟信号的同步。

为了防止亚稳态的出现,将rst_n信号用DFF向后延一周期,外部复位信号不会在出现释放时与clk信号竞争,整个系统将与全局时钟clk信号同步

复位电路会消耗更多的硬件逻辑和面积资源,增加系统设计的复杂性

module areset_srelease(

input rst_n,

input clk,

input din,

output reg dout

);

reg q1,q2;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

q1 <= 1'b0; //异步复位

q2 <= 1'b0;

end

else begin

q1 <= 1'b1; //同步释放

q2 <= q1; //同步打拍

end

end

//用q2来做异步复位

always@(posegde clk or negedge q2)begin

if(!q2)

q3 <= 1'b0;

else

q3 <= data_in;

end

endmodule

复位释放的时候:第一个触发器存在亚稳态,第二个为0

第二个周期:第一个触发器已经稳定,第二个可能为0或者1

第三个周期:第二个触发器稳定肯定为1

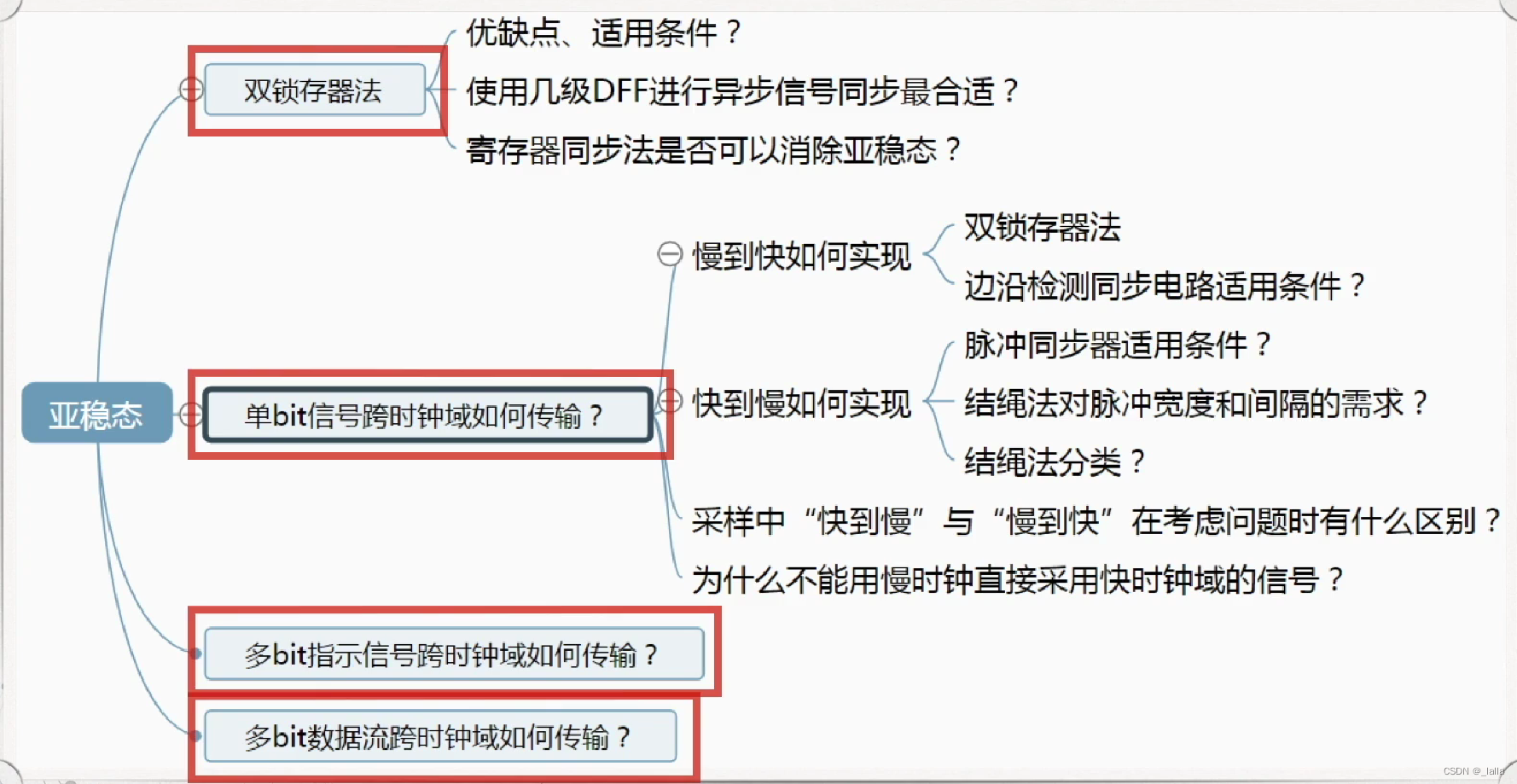

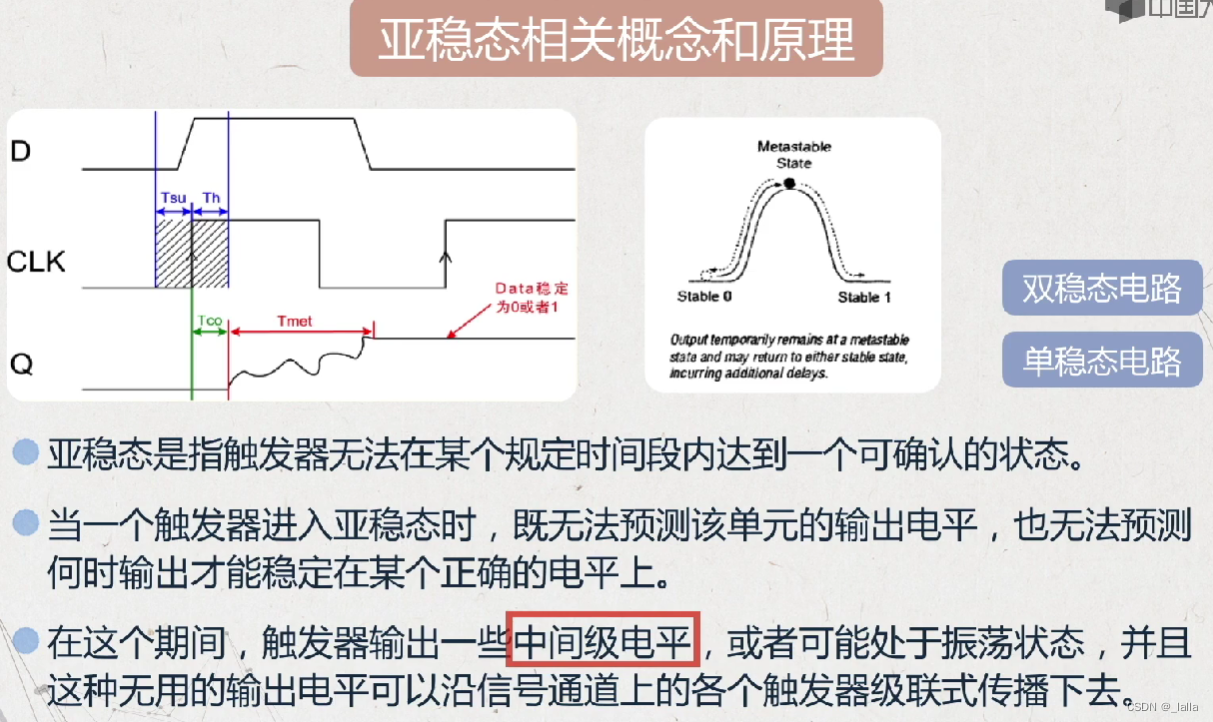

四、亚稳态

1、亚稳态定义

产生原因: 触发器在规定时间内无法达到一个确定状态,违背了建立时间和保持时间。

发生场景:

- 异步信号

- 跨时钟域工作

- 建立时间和保持时间为负值

- 时钟偏移、时钟信号质量不好

- 组合延迟使触发器数据输入在亚稳态窗口发生改变

并非所有不满足建立时间和保持时间的输入变化都会产生亚稳态,这还取决于工艺技术和环境条件,触发器会在1-2个clk内返回稳态。

亚稳态不能从根本上进行消除。

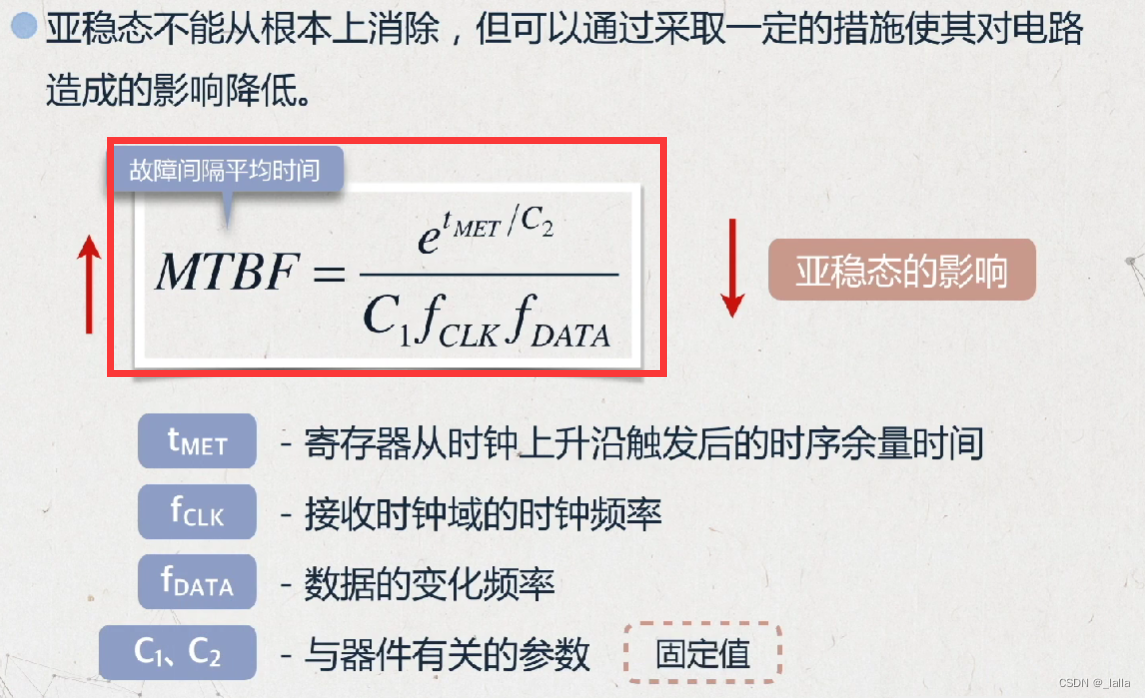

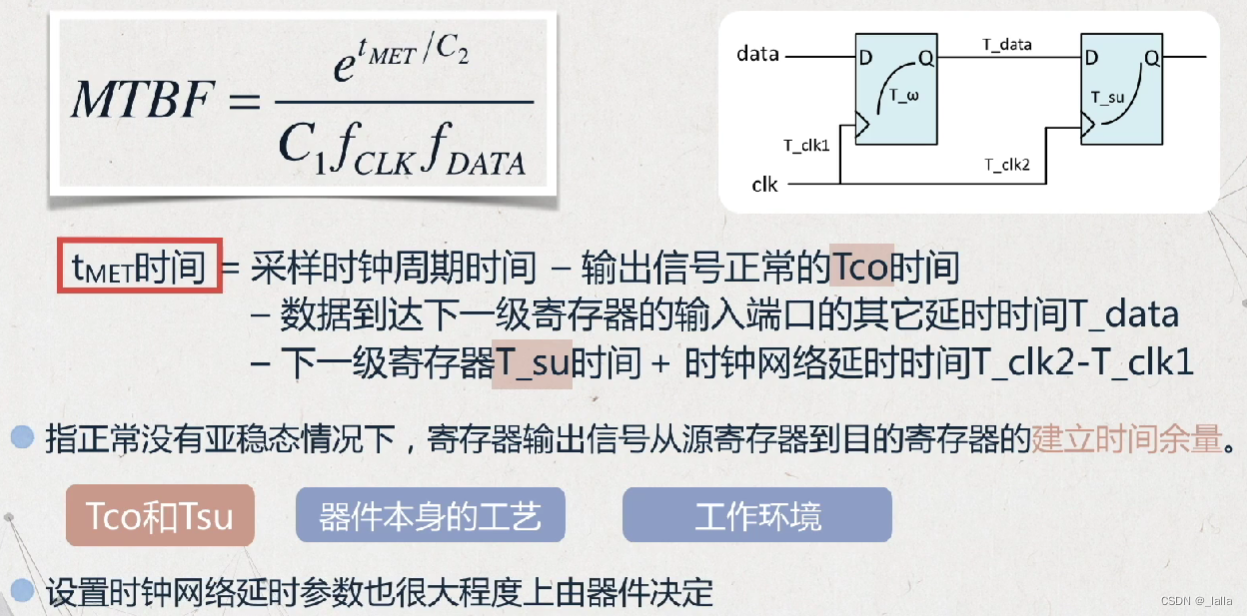

2、亚稳态参数:故障间隔平均时间MTBF

故障间隔平均时间MTBF(Mean Time Between Failure):衡量一个产品(尤其是电器产品)的可靠性指标

3、避免亚稳态方法

(1)使用多级同步器(但会增加电路的延时)

(2)使用时钟倍频电路的多级同步器

多级同步器的缺陷就是需要花较长的时间去响应输入,因此通过提高时钟频率来减少响应时间

(3)复位信号要做到异步复位同步释放

(4)改善时钟质量,用边沿变化较快的信号

(5)降低系统时钟频率,也就是降低采样频率

(6)引入同步机制,防止亚稳态的传播,如同步器、fifo

(7)使用采样更快的触发器,使得亚稳态窗口减小

五、简答题

1、CDC跨时钟域检查的工具

可以使用EDA工具;业界三大EDA公司Synopsys, Cadence, Mentor都有各自的CDC工具:Synopsys Spyglass CDC, Cadence Conformal Constraint Designer, Mentor Questa,其中以Synopsys公司的Spyglass CDC最为常用,市场占有率最高。

2、同步复位也会产生亚稳态吗?

当复位信号的撤销时间在建立时间和保持时间以内时,也会产生亚稳态。

概率=(set-time + hold-time)/周期

频率越高,发送亚稳态的概率越大,因此要减小亚稳态发送的概率,要减小工作频率或者set-time 和hold-time(更好的FPGA工艺)

517

517

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?