Cadence快速画原理图封装库

背景:当我们碰到管脚数很多的器件,一个个手敲定义,太慢了。Cadence就有一个很方便强大的功能,可以结合excel进行对其管脚参数定义进行编辑。(快的地方:芯片手册中管脚定义复制粘贴到excel)

一、新建一个原理图封装

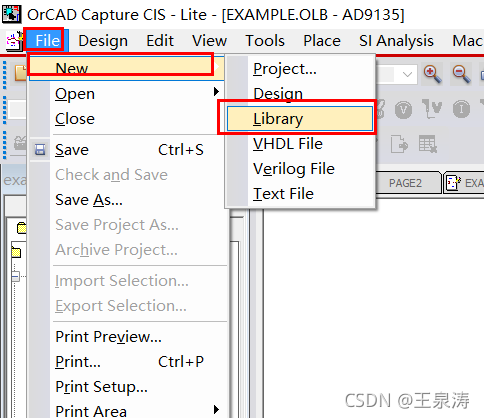

进入cadence的组件OrCAD,【File】——>【New】——>【Library】

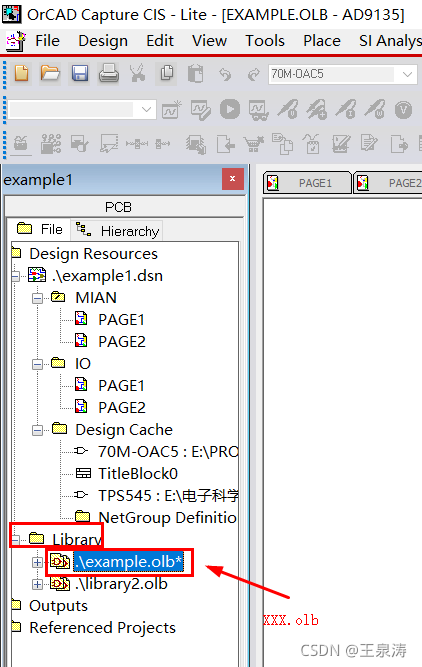

可以看到会生成一个XXX.olb的文件

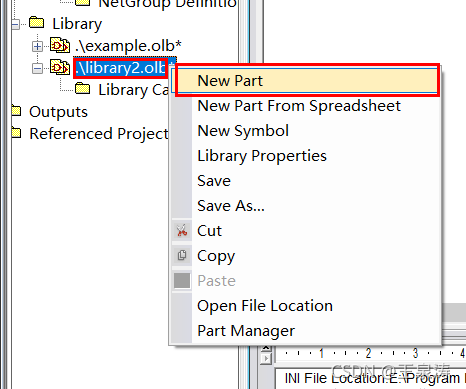

选中此文件,鼠标右击,看到【New Part】,点击

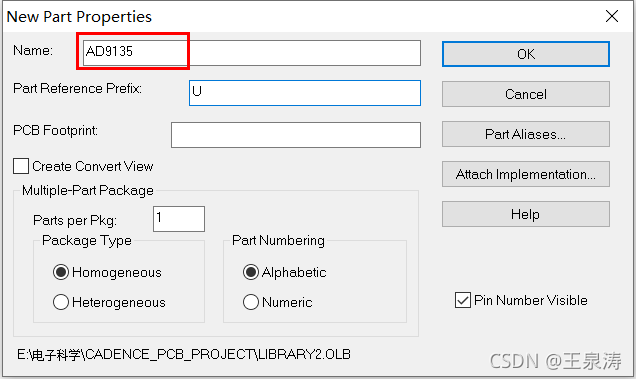

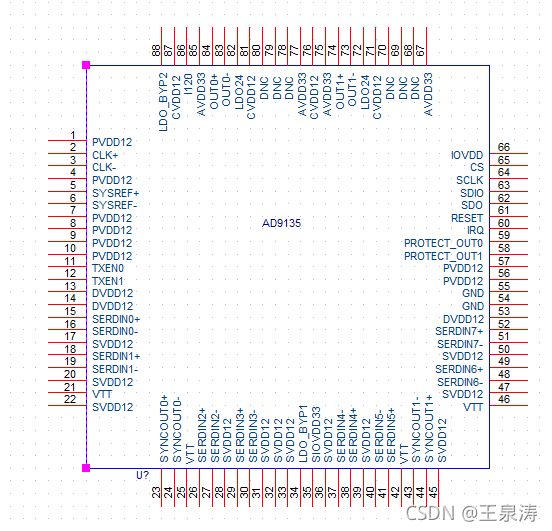

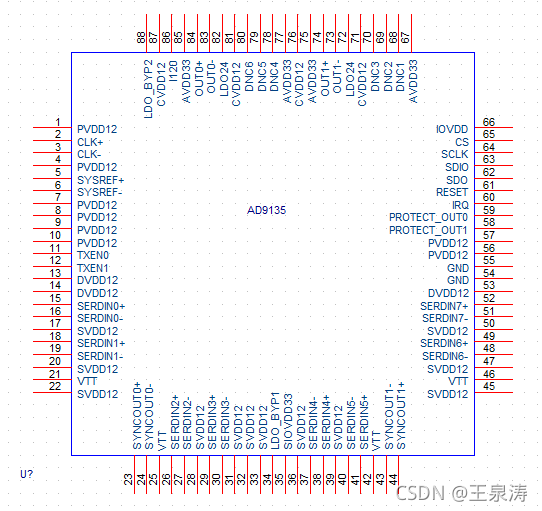

此教程以ADI的AD9135芯片为例,那填写元器件名称“AD9135”

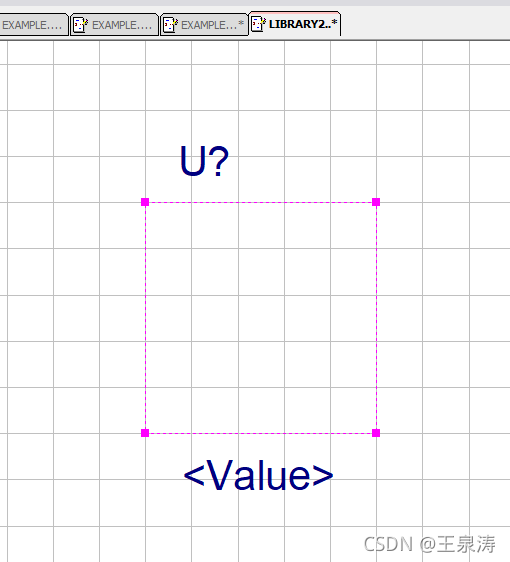

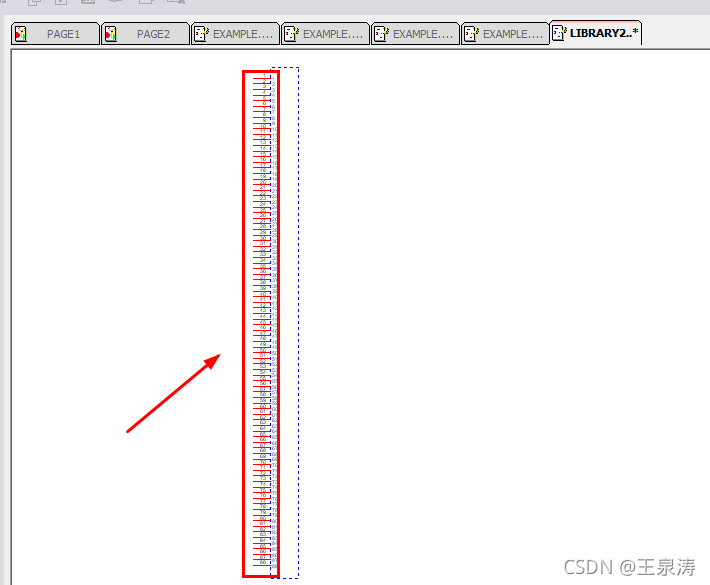

会生成一个紫色的框框

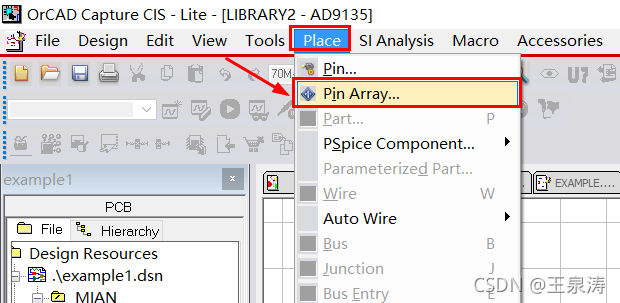

二、阵列放置管脚

【Place】——>【Pin Array】

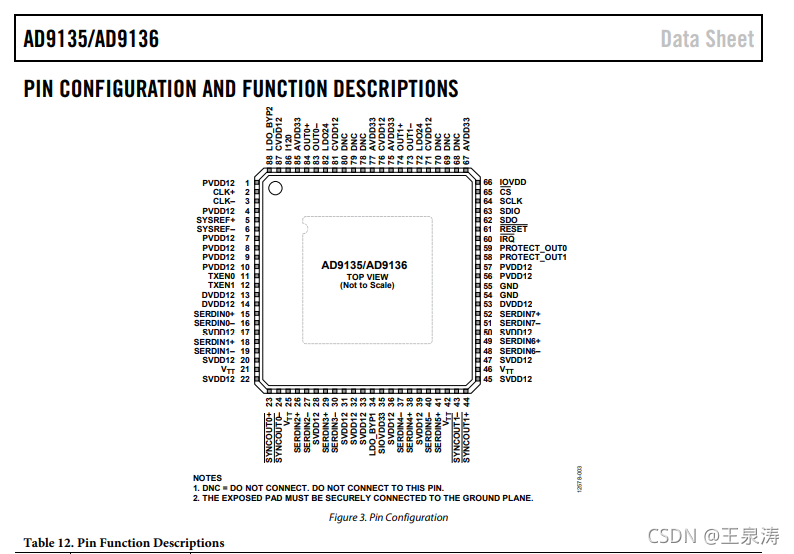

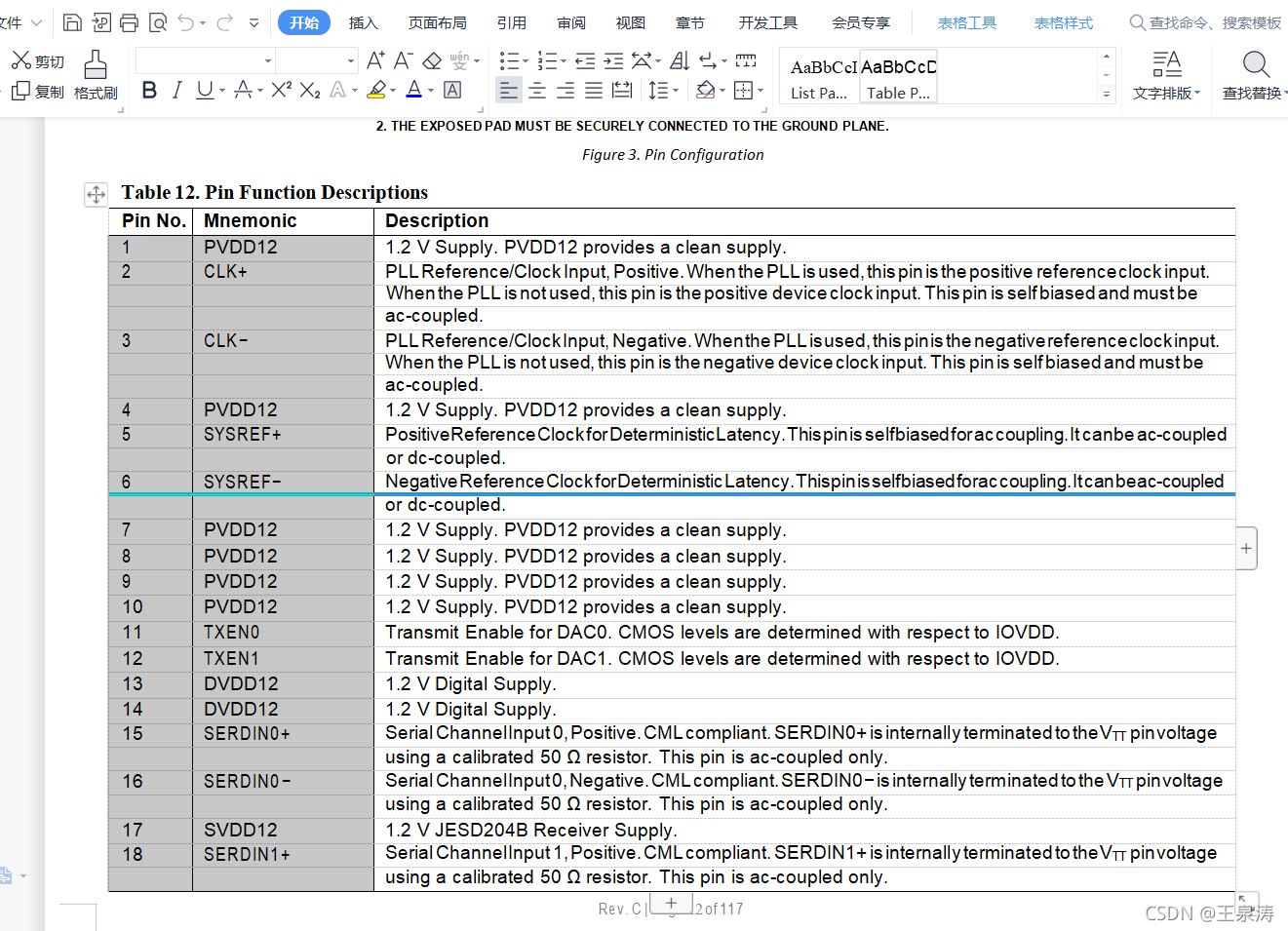

此教程以AD9135为例,那我们参见它的datasheet

http://datasheet.eeworld.com.cn/part/AD9135-EBZ,Analog_Devices_Inc.,21344352.html

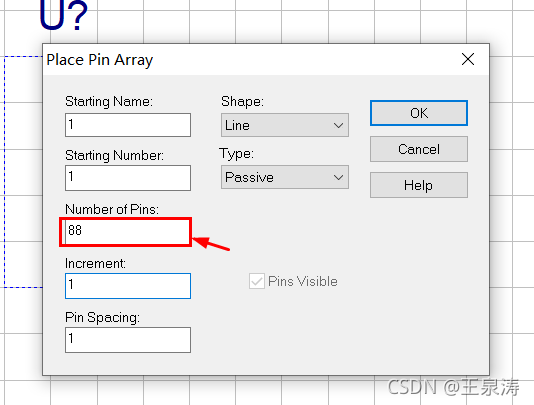

是一个88pin的芯片,引脚数量填写88,开始名字、数量填写1

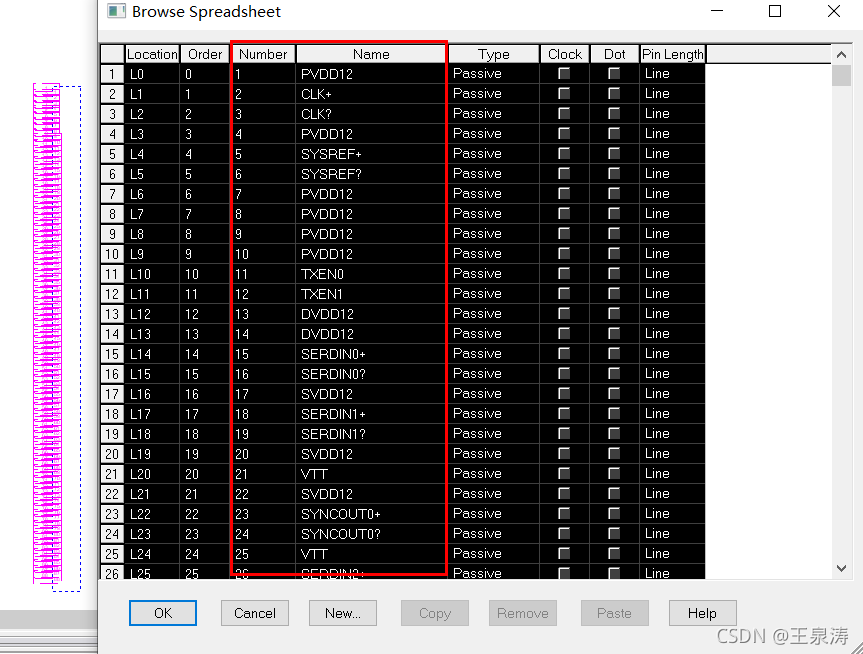

三、结合表格excel编辑管脚属性

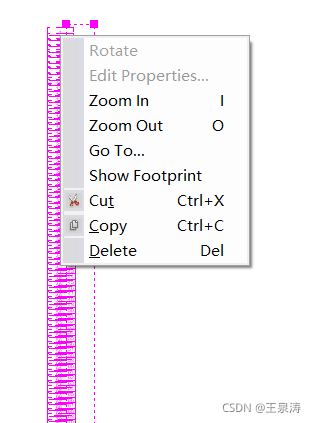

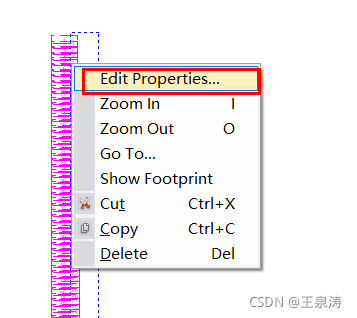

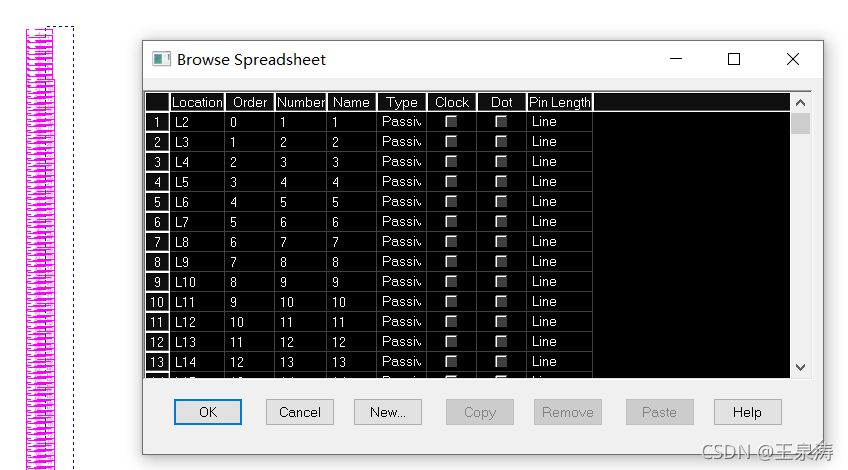

框选管脚准备编辑其属性,【Edit Properties】是暗的,没法操作(因为框选了器件轮廓框)

可以了。

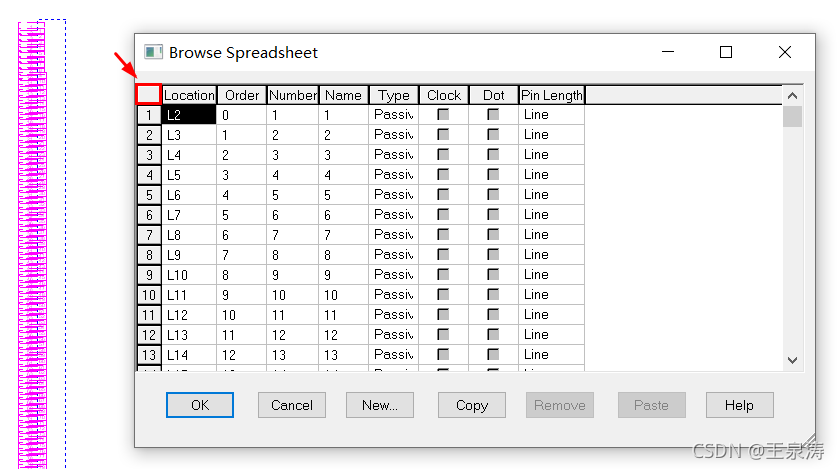

点击表格的左上角(箭头所指),进行全选操作

由于【Copy】是暗的,那就(CTRL+INSERT)快捷键进行复制操作

剩下关键一步就是将datasheet中的copy到excel,再从excel 复制粘贴到器件参数表中

运用pdf转word工具,在此使用solidconverter v10

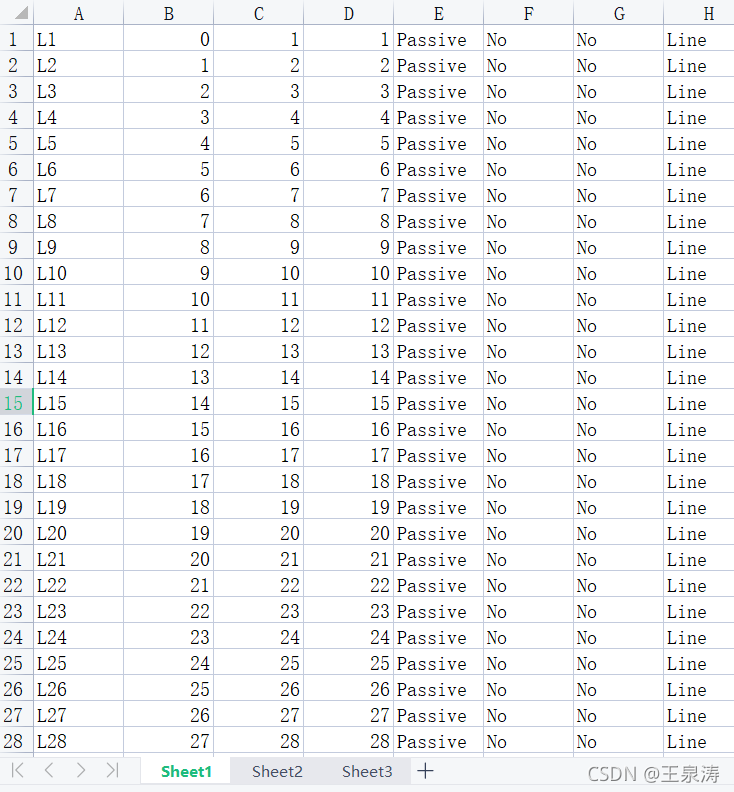

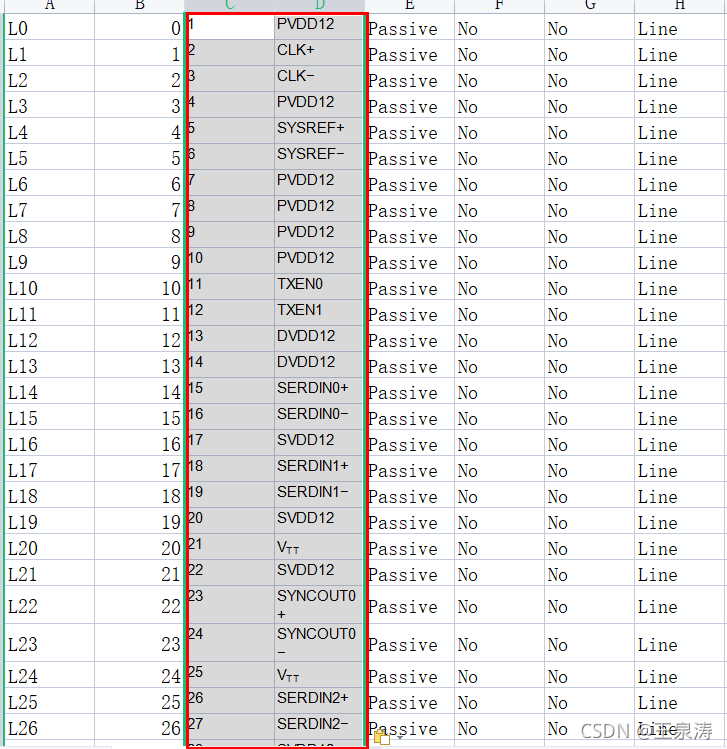

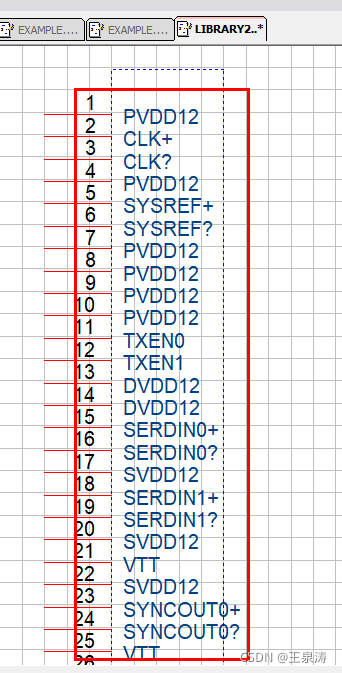

将管脚定义复制到excel中,进行核对整理排序,替换原来的第2、3列

在excel中框选中全部内容复制后,进入OrCAD器件封装编辑界面

【SHIFT】+【INSERT】快捷键,进行在参数表里粘贴

点击【OK】后,可以看到器件管脚名称已更新

四、进行修改和分布

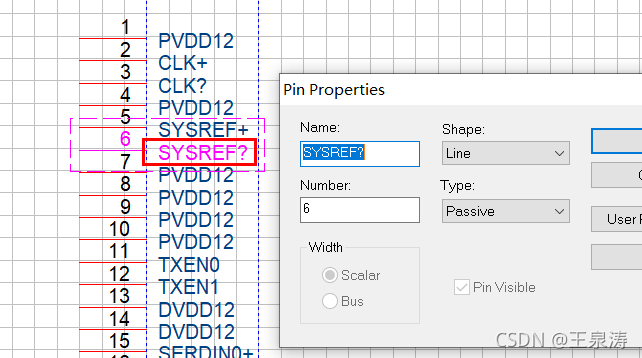

将里面识别的不正常字符,进行修改,如“?”,双击管脚弹出其属性进行修改名称

只能一个个修改了。(在属性表格里改快些)

excel复制到OrCAD器件属性表格“-”全部被识别成了“?”,不知道为啥会这样

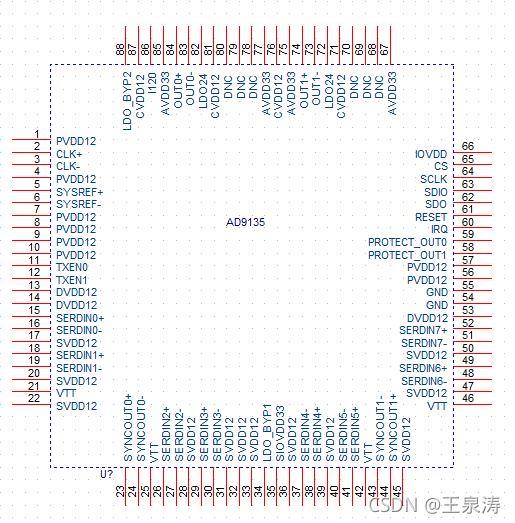

接下来,四周分布,每周边放置22个pin脚

管脚移动的操作,让人很不适应。移动没出现,复制粘贴为啥出现脚序反了???

最后四周在虚线框上补上实线,就是完整的原理图封装了。

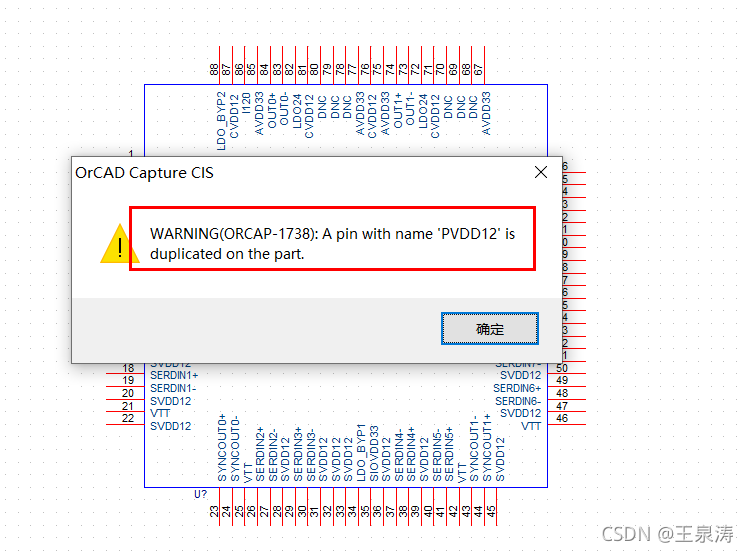

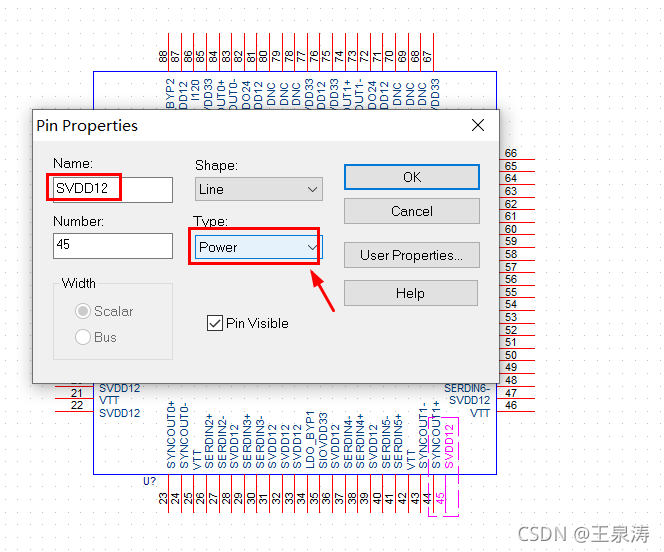

保存出现了错误:PVDD12出现了副本

需要改其管脚功能属性为电源,其他管脚报此错误,类似操作

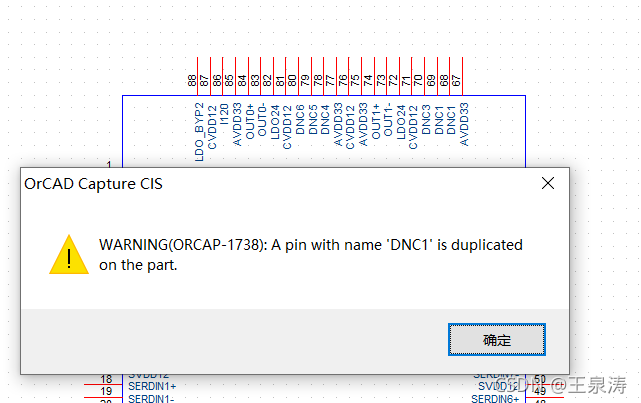

DNC1出现重复,改名字即可。

最后,保存时,直到不再弹出警告,才算完成!

cadence画封装,规则还是很严谨。。

操作存在疑问:

1、当器件名称字符跑到管脚位置上出现重叠放置时,选中字符就很难选的上?

2、88个管脚四周分布,采用剪切粘贴操作22个管脚到边框,周边管脚序反了,为什么?(如:正常脚序23 至44,反了:44至23)

本文介绍了如何使用Cadence结合Excel快速创建和编辑原理图封装库。通过新建封装,利用PinArray阵列放置管脚,然后借助Excel整理芯片管脚参数,再复制到器件属性表中批量更新管脚名称。遇到问题如特殊字符识别错误和管脚顺序错误时,需要手动修正。此外,还分享了器件名称重叠选择困难和管脚分布调整的技巧。

本文介绍了如何使用Cadence结合Excel快速创建和编辑原理图封装库。通过新建封装,利用PinArray阵列放置管脚,然后借助Excel整理芯片管脚参数,再复制到器件属性表中批量更新管脚名称。遇到问题如特殊字符识别错误和管脚顺序错误时,需要手动修正。此外,还分享了器件名称重叠选择困难和管脚分布调整的技巧。

3038

3038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?