解读一个四路组相联cache代码

在《计算机组成原理,软硬件接口》中,第五章便是cache的学习。本人初学cache,难免有疏漏之处,源代码github地址:https://github.com/airin711/Verilog-caches

1、四路组相联cache主要特征如下:

- 使用写分配写回;

- 块大小为十六字(64字节或1024位);

- 缓冲内包含2^14个块;

- 25位地址;

- cache每个块包含有效位和脏位。

- Cache块索引为14位;

- 块内偏移为4位;

- 标签大小为25-14-2=9位;

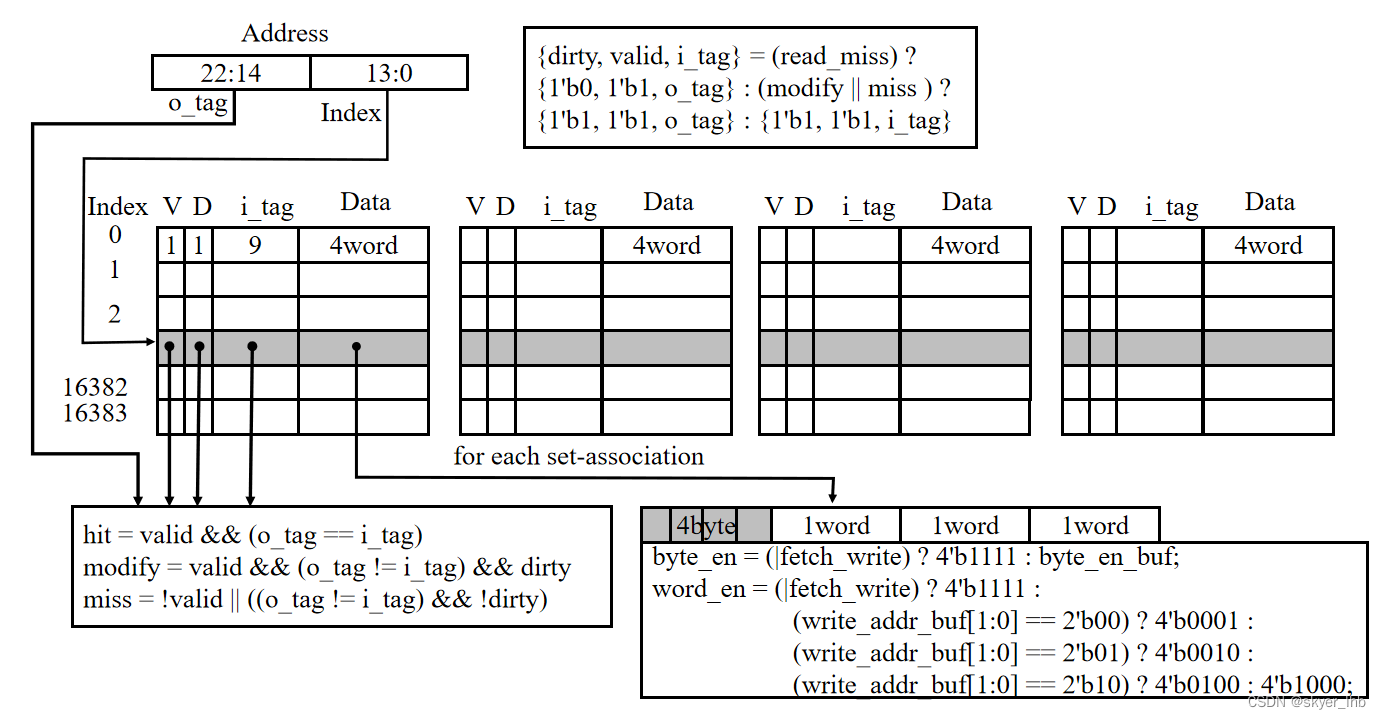

其原理图如下,包含命中、修改和失效的判断方法;脏位、有效位和标签的更新方法;字节、比特的选择方法(数据流仅画了一组):

2、控制信号

处理器与cache之间的控制信号:

| 信号 | 位数 | 作用 |

|---|---|---|

| i_p_addr | 25 | 地址输入 |

| i_p_byte_en | 4 | 比特选择 |

| i_p_writedata | 32 | 写数据 |

| i_p_read | 1 | 读信号 |

| i_p_write | 1 | 写信号 |

| o_p_readdata | 32 | 读数据 |

| o_p_readdata_valid | 1 | 读数据有效位 |

| o_p_waitrequest | 1 | 等待信号 |

存储器与cache之间的控制信号:

| 信号 | 位数 | 作用 |

|---|---|---|

| o_m_addr | 26 | 地址输出 |

| o_m_byte_en | 4 | 比特选择 |

| o_m_writedata | 128 | 写数据 |

| o_m_read | 1 | 读信号 |

| o_m_write | 1 | 写信号 |

| i_m_readdata | 128 | 读数据 |

| i_m_readdata_valid | 1 | 读数据有效位 |

| i_m_waitrequest | 1 | 等待信号 |

3、在组相联cache中查找所需数据块:

在同一组内的每个cache块的标签都需要比较,判断是否与处理器访问的数据块地址匹配。索引位用来选择访问数据所在的组,该组内所有数据块的标签都需要比较。组相联cache相对于直接映射而已,在于需要更多的比较器,以及由于比较器和选择带来的延迟。

4、失效时的替换方法:

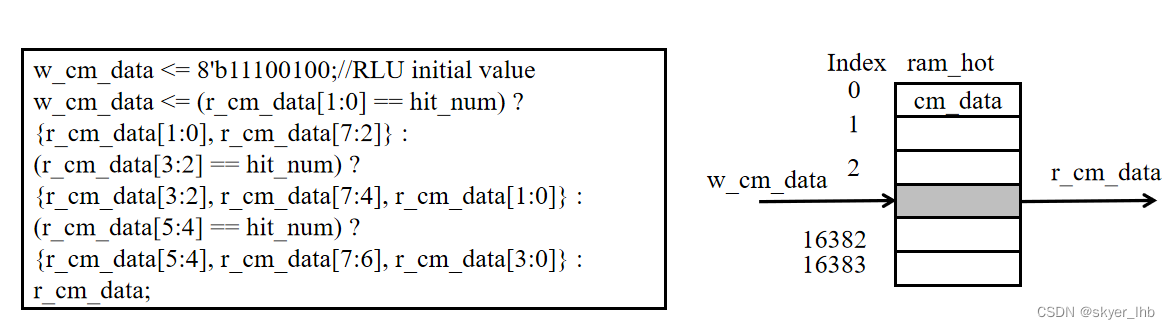

该组相联cache采用最近最少使用(RLU)方法替换数据块。

最近最少使用替换规则:对四路组相联来说,采用额外的存储单元ram_hot,每组有2bit的独热码。若第i组被访问过,则将表示第i组的独热码放在最前面。独热码的初始值及更新规则如下:

5、状态机简介

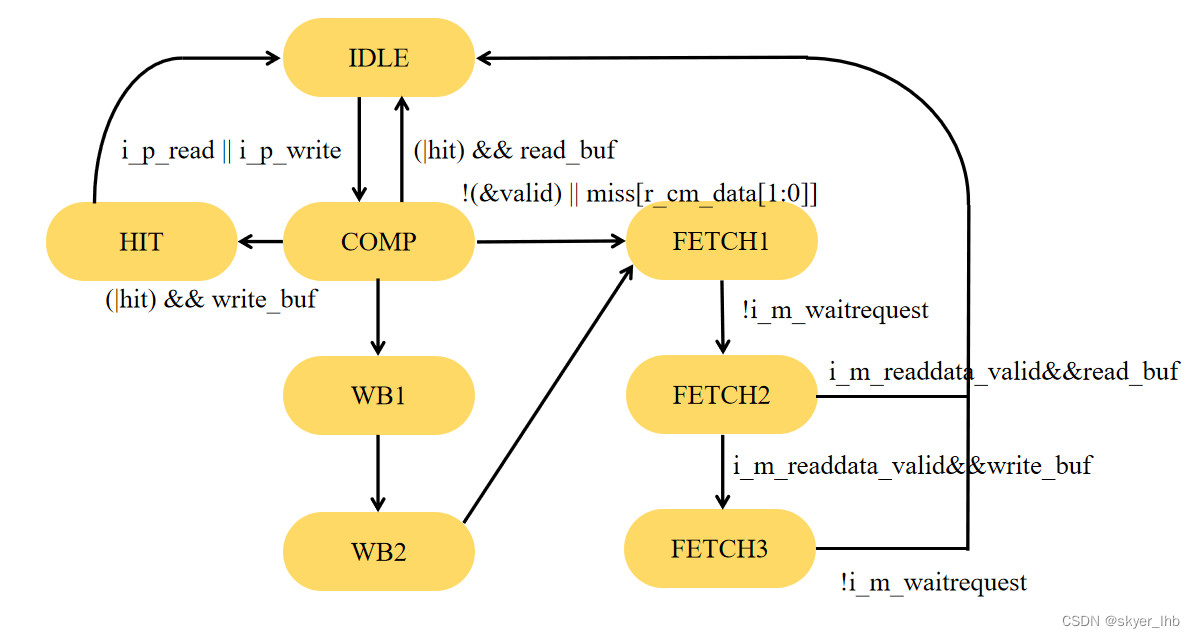

该有效状态机大体可分成三部分:

①、标签比较COMP:该状态检测读或写是命中还是失效。若命中,如果是加载指令就从选择的字中读取数据,如果是存储指令就将数据写入选择的字中,并设置脏位为1;若失效,先更新cache标签,之后如果当前脏位为1,则转跳到写回状态,如果为0,则转跳到分配状态。

②、写返回(WB1、WB2):该状态使用有标签和cache索引组成的地址将128位的块写回存储器。等待存储器写操作完成后,有限状态机跳转到分配状态。

当发生写回时,判断最近最少使用的哪一项对应哪个数据块,将其写回。

if(r_cm_data[1:0] == 2'b00) fetch_write <= 4'b0001;

else if(r_cm_data[1:0] == 2'b01) fetch_write <= 4'b0010;

else if(r_cm_data[1:0] == 2'b10) fetch_write <= 4'b0100;

else if(r_cm_data[1:0] == 2'b11) fetch_write <= 4'b1000;

o_m_addr <= (fetch_write[0]) ? {wb_addr0, 3'b000} :

(fetch_write[1]) ? {wb_addr1, 3'b000} :

(fetch_write[2]) ? {wb_addr2, 3'b000} : {wb_addr3, 3'b000};

o_m_writedata <= (fetch_write[0]) ? readdata0 :

(fetch_write[1]) ? readdata1 :

(fetch_write[2]) ? readdata2 : readdata3;

③、分配(FETCH1、FETCH2、FETCH3):从存储器中取出一个新块直接返回给处理器;

5208

5208

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?