FPGA学习日志

坚持每天写总结 2021.2.18

前言

准备参加比赛,需要学习riscv的相关知识,于是找了《手把手教你设计CPU——RISC-V处理器篇》以及一些开源的riscv核(蜂鸟E203、tinyriscv等)

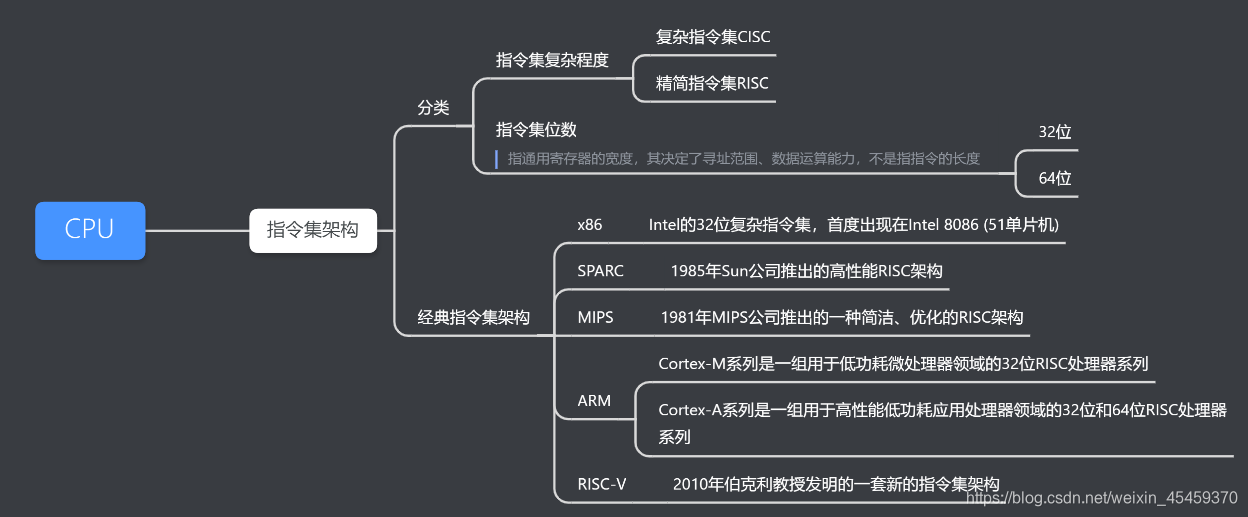

一、RISC-V是什么?

以下是我的理解,具体的定义要自己百度了

riscv是一种指令集,跟arm是同类。每一种指令集都有其特点,实现指令集的硬件结构多种多样,无论使用了哪一种硬件实现方式,只要实现了riscv指令,都属于riscv架构

二、学习RISC-V的探索过程

1.《手把手教你设计CPU——RISC-V处理器篇》

-

这本书说的是蜂鸟E200的RISCV核,先说了CPU的基本知识,再介绍了RISCV的知识,然后开始介绍蜂鸟E200,接着就开始逐步分析Cpu的架构,真的手把手教。

-

只是我觉得有点晦涩,适合沉下心来逐步学习,只是我现在处于选题调查阶段,需要尽快弄清楚这个蜂鸟E200移植的可能性,在github下载了源代码之后,发现不看懂配置文件的话,好像有点不可能,在说,我也有点不会用github。。

-

话说回来,这本书我一定要啃下来

2.liangkangnan的博客

能发现这篇博文,真是我的幸运,我是打心底里佩服这位大神,他是半路出家利用空做的空余时间完成了他的tinyriscv,真的让我这个微电子专业的大学生汗颜。respect!

-

硬件篇详细介绍了cpu每一个模块的设计思路和代码,因为是初学者的代码,所以能让我们这些萌新也能看得懂,我目前阶段是探索可行性,所以囫囵吞枣,拿来就用。

-

美中不足的是他的外设没有详细的设计介绍

-

软件篇的话,我还不太了解,我也不知道应该怎么用这个cpu,这个待了解

我下载了他的源码,在vivado通过了编译,但在quartus和PDS都出现了报错

- quartus的报错原因有两个

- ram和rom的错误

错误原因:应该是quartus提示,使用自己代码编写ram的效率不高

解决方案:使用quartus的ip库生成的ram作为rom和ram - 芯片资源不足,具体为logic element不够用

错误原因:uart_debug模块的状态机过于复杂,需要大量的选择器,又因为EP4CE10F17C8的operator中的选择器数量有限,不够的选择器由logic element来组成,所以就会消耗大量的LE

解决方案:

比赛时用的芯片资源够用,不用担心,但如果想用EP4CE10F17C8来初步实现的话,就要考虑状态合并、资源复用等代码优化了(目前应该还没有这个能力,不过第一次把资源用超标,也是一次不错的经验)

- PDS的报错

错误信息

Start sdm2adm.

F: sdmArrayElemLHS should not be here.

pds_shell crashes.

call stack dump:

00000001402b10ae

00000001402b15ed

00000001402b15dc

0000000140a8a5d5

0000000140a8c3ed

0000000140a90251

0000000140a8fbce

0000000140ab4fba

00000001403d00b3

00000001403f03fc

000000014009cac4

00000001400a0fee

00000001400a0b79

00007ffa93ee01c4

00007ffa93edeeb7

00007ffa93eb8767

00007ffa93eb8829

00007ffa93eba6d8

00007ffa93f02e02

00007ffb1b42e858

00007ffb1b42e299

00007ffa93f026c5

00007ffa93eb4b7b

00007ffa93eb776e

00000001400a40f8

00000001409a8084

00007ffb1b817034

00007ffb1c2dd241

00000001400a3ff0

E: Flow-0189: Internal error occured.

报错原因:报错部位出现在uart_debug模块中,目前还不知道具体的原因,我怀疑是(明明quartus能通过编译的说)

解决方法:未知

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?