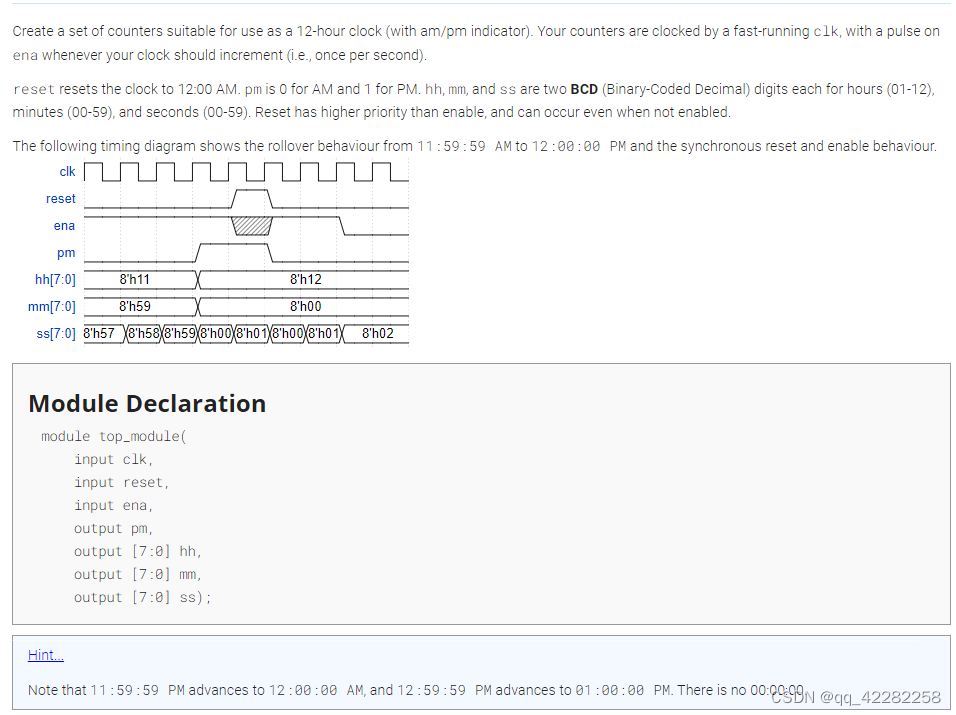

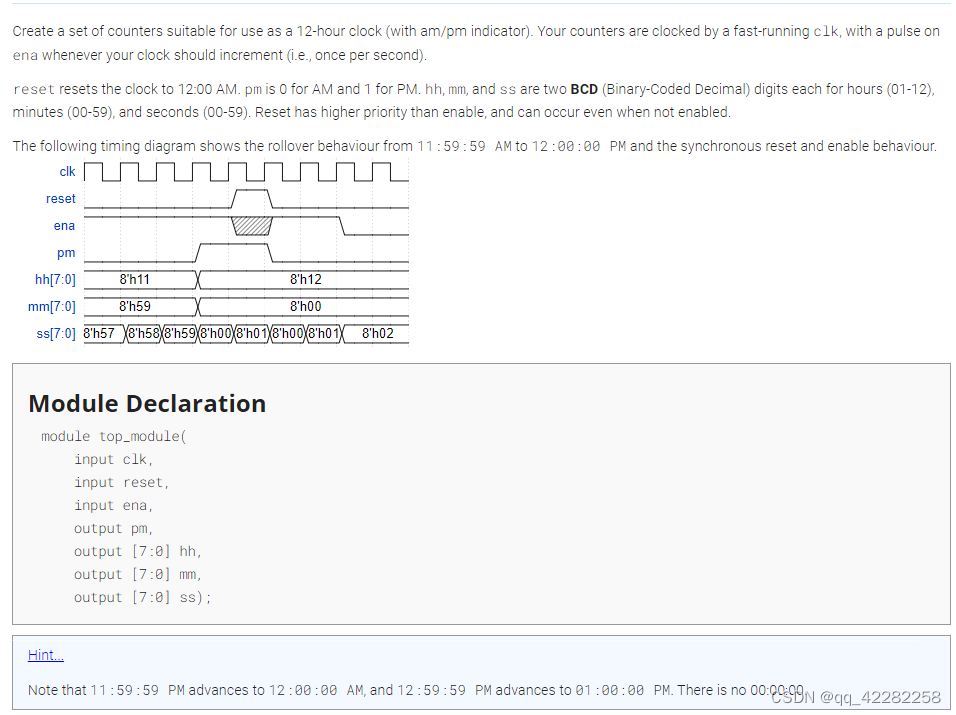

1原题复现

2.代码

module top_module(

input clk,

input reset,

input ena,

output pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss);

reg [3:0] ss_gewei=0;

reg [3:0] ss_shiwei=0;

reg [3:0] mm_gewei=0;

reg [3:0] mm_shiwei=0;

reg [3:0] hh_gewei =0;

reg [3:0] hh_shiwei =0;

always@(posedge clk)begin

if(reset)begin

ss_shiwei<=4'd0;

ss_gewei<=4'd0;

end

else if(ena)begin

if(ss_gewei==4'h9)begin

ss_gewei<=0;

if(ss_shiwei==4'h5)begin

ss_shiwei<=0;

end

else begin

ss_shiwei<= ss_shiwei+1;

end

end

else ss_gewei<=ss_gewei+1;

end

end

assign ss = {ss_shiwei,ss_gewei};

always@(posedge clk)begin

if(reset)begin

mm_shiwei<=4'd0;

mm_gewei<=4'd0;

end

else if(ss_shiwei == 4'h5 && ss_gewei == 4'h9 && ena==1'b1)begin

if(mm_gewei==4'h9)begin

mm_gewei<=0;

if(mm_shiwei==4'h5)begin

mm_shiwei<=0;

end

else begin

mm_shiwei<= mm_shiwei+1;

end

end

else mm_gewei<=mm_gewei+1;

end

end

assign mm = {mm_shiwei,mm_gewei};

always@(posedge clk)begin

if(reset)begin

hh_shiwei<=4'd1;

hh_gewei<=4'd2;

pm<=0;

end

else if(ss_shiwei == 4'h5 && ss_gewei == 4'h9 && ena==1'b1 && mm_shiwei == 4'h5 && mm_gewei == 4'h9)begin

if(hh_shiwei==4'h0)begin

if(hh_gewei ==4'h9)begin

hh_gewei<=0;

hh_shiwei <= 1'b1;

end

else begin

hh_gewei <= hh_gewei+1;

end

end

else if(hh_shiwei==4'h1)begin

if(hh_gewei ==4'h1)begin

hh_gewei <=4'h2;

pm <= ~pm;

end

if(hh_gewei == 4'h2)begin

hh_gewei <=1'b1;

hh_shiwei <=1'b0;

end

else hh_gewei <= hh_gewei +1;

end

end

end

assign hh = {hh_shiwei,hh_gewei};

endmodule

859

859

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?