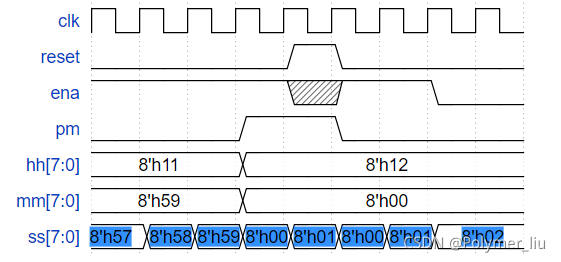

创建一组适合用作 12 小时制的计数器(带有 am/pm 指示器)。 您的计数器由快速运行的 clk 计时,每当您的时钟应增加(即每秒一次)时,就会在 ena 上发出脉冲。reset 将时钟重置为 12:00 AM。 pm 是 0 代表上午,1 代表下午。 hh、mm 和 ss 是两个 BC(二进制编码的十进制)数字,每个数字表示小时 (01-12)、分钟 (00-59) 和秒 (00-59)。 复位的优先级高于使能,即使未使能也可能发生。以下时序图显示了从上午 11:59:59 到下午 12:00:00 的翻转行为以及同步复位和启用行为。

题目解析:构建12小时进制计数器,首先厘清 分、秒、时之间的进位关系

60秒进位分,同时秒归为0

60分进位时,同时分归为0

12时59分59秒达成计数器置为1时00分00秒

其次选择设计方式,我选择的是层次化建模:

首先构造10进制计数器,然后经由10进制构成100进制计数器

创建一组适合用作 12 小时制的计数器(带有 am/pm 指示器)。 您的计数器由快速运行的 clk 计时,每当您的时钟应增加(即每秒一次)时,就会在 ena 上发出脉冲。reset 将时钟重置为 12:00 AM。 pm 是 0 代表上午,1 代表下午。 hh、mm 和 ss 是两个 BC(二进制编码的十进制)数字,每个数字表示小时 (01-12)、分钟 (00-59) 和秒 (00-59)。 复位的优先级高于使能,即使未使能也可能发生。以下时序图显示了从上午 11:59:59 到下午 1...

创建一组适合用作 12 小时制的计数器(带有 am/pm 指示器)。 您的计数器由快速运行的 clk 计时,每当您的时钟应增加(即每秒一次)时,就会在 ena 上发出脉冲。reset 将时钟重置为 12:00 AM。 pm 是 0 代表上午,1 代表下午。 hh、mm 和 ss 是两个 BC(二进制编码的十进制)数字,每个数字表示小时 (01-12)、分钟 (00-59) 和秒 (00-59)。 复位的优先级高于使能,即使未使能也可能发生。以下时序图显示了从上午 11:59:59 到下午 1...

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

317

317

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?