写在前面:

个人留个笔记,如果有必要请联系qq(见csdn账号),我会删除

顺便一提,每学期的题目会有小改动,直接抄被发现直接挂科

顺顺便一提,今年有叫做了全部作业和设计结果挂科不服的,老师直接点出来抄就没反驳了,谁知道抄没呢,嘻嘻

任务要求:

完成如下三种同步器电路的设计、功能仿真与时序仿真验证。

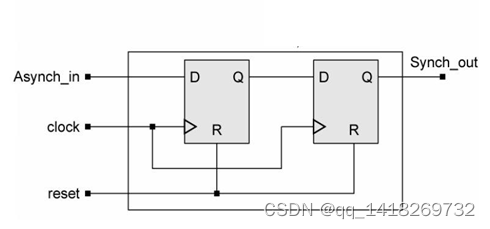

一、第一种同步器

原电路图:

设计代码:

设计代码:

D.v文件

module D(

clk,d_in,rst,q

);

input clk,d_in,rst;

output q;

reg q;

always@(posedge clk or posedge rst)

begin

if (rst==1'b1)

q<= 0;

else q<=d_in;

end

endmodule

D_logic_1.v

module D_logic_1(

asynch_in,clk,reset,synch_out

);

input asynch_in,clk,reset;

output synch_out;

wire D1_out;

D U0(.clk(clk),.d_in(asynch_in),.rst(reset),.q(D1_out));

D U1(.clk(clk),.d_in(D1_out),.rst(reset),.q(synch_out));

Endmodule

仿真代码

module tb_D_logic_1();

reg asynch_in,clk,reset;

wire synch_out;

D_logic_1 U1(.asynch_in(asynch_in),.clk(clk),.reset(reset),.synch_out(synch_out));

initial begin

clk = 1;

#5

reset <= 1;

#20

reset <= 0;

forever begin

#13

asynch_in <= 1;

#21

asynch_in <= 0;

#17

asynch_in <= 1;

end

end

always #10 clk = ~clk;

endmodule

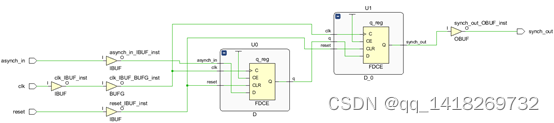

综合结果

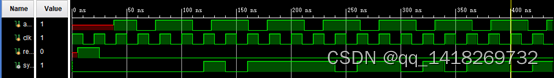

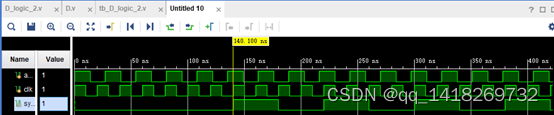

功能仿真结果

功能仿真结果

可以从第一个信号看到,此同步器实现了将输入波形延迟了两个时钟再输出,第一个输出表示,此时时钟高电平,但输入信号为低,在之前两个高电平提升态时是高电平,此输出高电平为彼时采样的延时。

可以从第一个信号看到,此同步器实现了将输入波形延迟了两个时钟再输出,第一个输出表示,此时时钟高电平,但输入信号为低,在之前两个高电平提升态时是高电平,此输出高电平为彼时采样的延时。

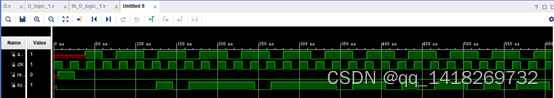

时序仿真结果

分析:

很明显时序仿真的输出信号不和clk对齐,因为时序仿真比功能仿真考虑更多期间影响,总体上输出还是一致,只是输出时延更多一些。

二、第二种同步器

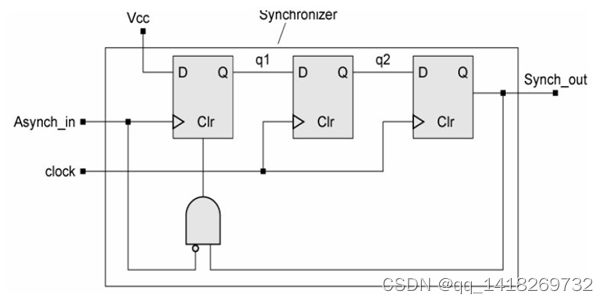

原电路图:

设计代码:

D.v文件

module D(

clk,d_in,rst,q

);

input clk,d_in,rst;

output q;

reg q;

always@(posedge clk or posedge rst)

begin

if (rst==1'b1)

q<= 0;

else q<=d_in;

end

endmodule

D_logic_2.V

module tb_D_logic_2();

reg asynch_in,clk;

wire synch_out;

D_logic_2 U1(

asynch_in,clk,synch_out);

initial begin

clk = 1;

asynch_in = 1;

forever begin

#14

asynch_in = 0;

#13

asynch_in = 1;

end

end

always #10 clk=~clk;

endmodule

仿真文件

module tb_D_logic_2();

reg asynch_in,clk;

wire synch_out;

D_logic_2 U1(asynch_in,clk,synch_out);

initial begin

clk = 1;

asynch_in = 1;

forever begin

#14

asynch_in = 0;

#13

asynch_in = 1;

end

end

always #10 clk=~clk;

endmodule

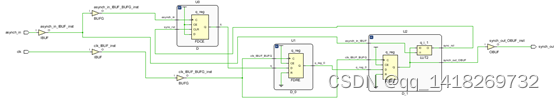

综合结果

功能仿真结果

可以看到相比之前的电路,这个电路的输出高电平长度更稳定,同时延时也更大。

时序仿真结果

分析:

很明显时序仿真的输出信号不和clk对齐,因为时序仿真比功能仿真考虑更多期间影响,总体上输出还是一致,只是输出时延更多一些。

三、第三种同步器

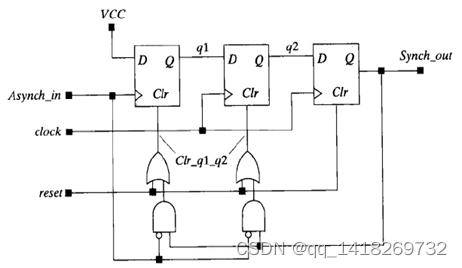

原电路图:

设计代码:

D.v文件

module D(

clk,d_in,rst,q

);

input clk,d_in,rst;

output q;

reg q;

always@(posedge clk or posedge rst)

begin

if (rst==1'b1)

q<= 0;

else q<=d_in;

end

endmodule

D_logic_3.V

module D_logic_3(rst,asynch_in,clk,synch_out);

input rst,asynch_in,clk;

output synch_out;

wire clr_q1_q2 = (!asynch_in && synch_out)|| rst;

wire q1,q2,synch_out;

D U0(.clk(asynch_in),.d_in(1),.rst(clr_q1_q2),.q(q1));

D U1(.clk(clk),.d_in(q1),.rst(clr_q1_q2),.q(q2));

D U2(.clk(clk),.d_in(q2),.rst(rst),.q(synch_out));

Endmodule

仿真代码

module test_logic_3();

reg asynch_in,clock,reset;

wire synch_out;

D_logic_3 U1(.rst(reset),.asynch_in(asynch_in),.clk(clock),.synch_out(synch_out));

initial begin

asynch_in = 1'b0;

clock = 1'b0;

reset = 1'b0;

// 人为生成毛刺

forever

begin

forever begin

#12 asynch_in = 1;

#17 asynch_in = 0;

end

end

end

initial begin

forever begin

#100 reset = 1;

#150 reset = 0;

end

end

always #10 clock = ~clock;

endmodule

综合结果

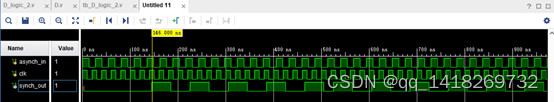

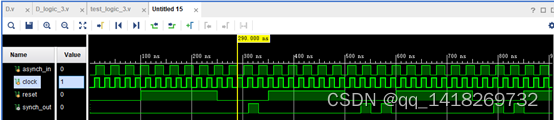

功能仿真结果

可以看到输出采样于前一个时钟时采样的输入,输出时间为两个时钟且稳定

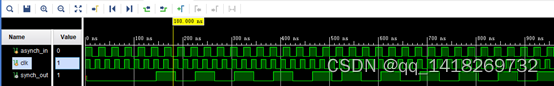

时序仿真结果

分析:

很明显时序仿真的输出信号不和clk对齐,因为时序仿真比功能仿真考虑更多期间影响,总体上输出还是一致,只是输出时延更多一些。

564

564

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?