DesignWare低功耗流水线浮点乘法器介绍

在AI处理器中,乘累加是其中最主要的操作,在各种量化方案中,需要将最终的量化整型结果转化为实际的浮点结果,这就需要使用浮点乘法器。低功耗的浮点乘法器运算一般需要多个时钟周期完成一次运算,但采用流水线的方式便可在第一个计算结果完成后的每个时钟周期得到相应的计算结果,能够极大的提升数据运算的速度。

在ASIC的设计中,DC中的DesignWare提供了低功耗的流水线浮点乘法器的IP,接下来将对IP的使用进行说明。

流水线浮点乘法器对应的文件为:DW_lp_piped_fp_mult.v,该IP的特点如下:

- 精度格式可针对单精度、双精度或用户定义的自定义格式进行参数化;

- 有选择地提供IEEE 754标准的异常数硬件结构;

- 完全兼容IEEE 754标准,具有适当的参数集;

- 根据需要启动流水线,从而节省功耗;

- 根据输入数据模式节省功耗;

- 通过参数来控制流水线的级数;

- 控制流接口直接与FIFO相连接;

- 控制流接口到另一个受管理的流水线;

- 气泡去除后,后续FIFO的深度按流水线深度延长;

- 参数大小的识别器跟踪数据操作;

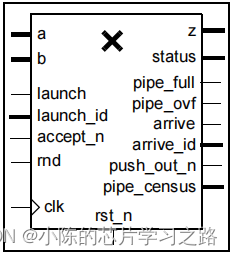

DW_lp_piped_fp_mult顶层电路框图如下所示:

DW_lp_piped_fp_mult 是一个浮点运算器,它将两个浮点操作数相乘:a 乘以 b 以产生浮点积 z。输入 rnd 为 3 位舍入模式(如引脚说明表所示),输出status为 8 位状态标志。浮点运算由流水线控制器DW_lp_pipe_mgr有条件地管理,具体取决于no_pm参数。该组件配置了用户可选择的逻辑级数,允许DC优化寄存器级之间的逻辑,以降低功耗和面积。DC能够利用设计中提供的使能信号来优化整个乘法运算中的组合逻辑。当 no_pm = 0 时,流水线控制器可以根据跟踪流水线操作进度的 launch 请求来管理流水线的注册阶段的启用。仅在需要运算时才启用流水线,可降低动态功耗,并通过时钟门控插入(这需要 Synopsys Power Compiler)进一步增强。Launch请求可以附带一个launch_id,该可用作标记,以识别从流水线中退出的操作结果。输出的pipe_census信号监视流水线中的操作数的数量,如果没有流水线控制器(no_pm = 1),DW_lp_piped_fp_mult仍然可以启用寄存器重新定时功能,并提供用于跟踪每个已启动事务的标识句柄。只有通过设置no_pm = 0,利用流水线控制机制(DW_lp_pipe_mgr)才能获得完全节能。

DW_lp_piped_fp_mult提供插入时钟门控元件并包含操作数隔离单元以最大限度地降低功耗的功能,并且仅适用于 DC 版本 C-2009.06 及更高版本。。

引脚说明

| 信号名称 | 位宽 | 方向 | 信号描述 |

|---|---|---|---|

| clk | 1 | IN | 时钟信号 |

| rst_n | 1 | IN | 异步复位信号,若参数rst_mode=0,则该信号无效 |

| a | sig_width+exp_width+1 | IN | 输入乘数a |

| b | sig_width+exp_width+1 | IN | 输入乘数b |

| rnd | 3 | IN | 舍入模式 |

| launch | 1 | IN | 控制是否开始乘法运算 |

| launch_id | 1 | IN | 判断当前的乘法运算是属于哪一个launch |

| accept_n | 1 | IN | 当前输出结果是否被读取信号,低有效 |

| z | sig_width+exp_width+1 | OUT | 输出结果z=a×b |

| status | 8 | OUT | z的状态标志信号 |

| pipe_full | 1 | OUT | 输出浮点乘法器中的流水线是否为满信号 |

| pipe_ovf | 1 | OUT | 流水线溢出的状态标志信号 |

| arrive | 1 | OUT | 输出结果z的有效信号 |

| arrive_id | id_width | OUT | 来自launch_id,标志当前的arrive |

| push_out_n | 1 | OUT | 将结果压入输出FIFO的压使能信号,低有效 |

| pipe_census | M | OUT | 当前流水线中流水线寄存器被占用的数量,M=ceil(log2(in_reg+stages+out_reg)),ceil表示向上取整 |

参数说明

| 参数名称 | 值 | 描述 |

|---|---|---|

| sig_width | 2-253,默认为23 | a,b,z的尾数位宽 |

| exp_width | 3-31,默认为8 | a,b,z的阶码位宽 |

| ieee_compliance | 0或1,默认为0 | 是否兼容IEEE754标准,0:不支持 IEEE 754 NaNs和异常值;NaNs被认为是无穷大,异常值被认为是零;1:完全兼容 IEEE 754 标准,包括支持 NaNs 和异常值 |

| op_iso_mode | 0-4,默认为0 | 操作数隔离模式(控制数据通路门控,减小功耗),0:使用DW_lp_op_iso_mode综合变量;1:无时钟门控;2:时钟门控为与门;3:时钟门控为或门;4:首选与门为作为门控;仅当组件边界的操作数上没有输入寄存器时,才会插入数据路径门控。插入后,数据路径门控电路紧跟在元件的输入端口之后 |

| id_width | 1-1024,默认为1 | launch_id 和 arrive_id 的位宽大小 |

| in_reg | 0或1,默认为0 | 数据输入端是否包含输入寄存器,0:不包含;1:包含 |

| stages | 1-1022,默认为2 | 流水线的级数 |

| out_reg | 0或1,默认为0 | 数据输出端是否包含输出寄存器,0:不包含;1:包含 |

| no_pm | 0或1,默认为1 | 是否使用流水线控制器,0:使用;1:不使用 |

| rst_mode | 0或1,默认为0 | 复位模式,0:异步复位;1:同步复位 |

DW_lp_op_iso_mode综合变量仅在DC中可用。DW_lp_op_iso_mode设置数据路径门控的全局样式。要使用全局样式,请将op_iso_mode设置为“0”,请注意,如果 op_iso_mode 参数设置为“0”,并且DW_lp_op_iso_mode未设置或设置为 0“,则不会为此组件插入数据路径门控。

舍入模式

舍入是将被视为无限精确的数字映射到有限精度的FP格式的过程。对于整数,舍入表明生成二进制点右侧没有数据输出;对于浮点数,舍入意味着有效位数降低到二进制点右侧的f位精度。在这两种情况下,长精度结果首先被截断(丢弃最低有效位(LSB))以获得所需的位数。此有效数是一个 FP 数的一部分,该数字近似于无限精度结果。还有一个FP数字更大(在幅度上),它是通过增加截断的有效数并进行调整以使有效数归一化而获得的。因此,舍入方法定义了如何决定使用这两个数字之一作为无限精度结果的有效近似值。在舍入过程中也会考虑结果的符号。

在此阶段,浮点数表示中使用的指数值没有界,这意味着舍入过程仅关注有效数值。这也意味着近似数字可能超出可表示数字的范围,这被视为例外,必须单独处理。

浮点分量支持舍入模式的动态选择,该模式由rnd来确定,如下表所示(F1和F2均无限精确于F,F1<F2)。

| rnd | 舍入模式 | 别名 | 描述 |

|---|---|---|---|

| 000 | IEEE round to nearest(even) | even | 四舍五入到最接近的 FP 。如果 F1 和 F2 同样接近,请选择有效数为偶数的那个(LSB = 0 )。 |

| 001 | IEEE round to zero | zero | 若F≥ 0,选择F1,否则选择F2;即选择最接近0的值 |

| 010 | IEEE round to positive infinity | +∞ | 选择F2,即选择最接近正无限大的值 |

| 011 | IEEE round to negative infinity | -∞ | 选择F1,即选择最接近负无限大的值 |

| 100 | round to nearest up | up | 四舍五入到最接近的 FP 。如果 F1 和 F2 同样接近,若F≥ 0,选择F2;否则选择F1 |

| 101 | round away from zero | away | 若F≥ 0,选择F2;否则选择F1;即选择远离0的值 |

| 110 | 保留 | ||

| 111 | 保留 |

在所有舍入模式下,如果从 F 的无穷精确有效数中丢弃的 LSB 为零,则 F1 或 F2 与 F 完全匹配,并且没有舍入。当被丢弃的LSB不为零时,无限精确的有效数严格位于两个可表示的有效数之间,因此舍入的数字是不精确的。舍入浮点数 (F_rnd) 根据舍入模式和 F 的值/符号确定为 F1 或 F2。可能是F_rnd的指数太大(溢出)或太小(下溢),无法以给定格式表示为 FP 值,这些情况称为例外,即产生了越界,如下图所示:

输出状态标志

| Status | Flag | 描述 |

|---|---|---|

| 0 | Zero | 浮点输出结果为0 |

| 1 | infinity | 浮点输出结果为无穷大 |

| 2 | Invalid | 浮点输出结果无效,当输入为NaN(ieee_compliance=1)时,该值同样可设为1,表无穷大 |

| 3 | Tiny | 具有无界指数的舍入浮点数的量级小于最小归一化数,并且它不是精确的零 |

| 4 | Huge | 具有无界指数的舍入浮点数的量级大于最大归一化 |

| 5 | Inexact | 整数或浮点输出不等于无限精确的结果 |

| 6 | HugeInt | 舍入后的整数结果的量级大于具有相同符号的最大可表示二进制补码整数 |

| 7 | CompSpecific | 此标志具有针对某些 DW 组件指定的含义,如果未在组件数据表中描述,则不使用此标志,其值为 0 |

959

959

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?