FPGA与VHDL语言学习2

目录

1. 7位2进制计数器程序,要求计算器从0开始计数,计数到59(十进制的59,看到的是二进制数)后归零,重新循环计数

2. 2位十进制计数器程序,要求计数器从00开始计数,计数到53(十进制的53,看到的是十进制数53)后归零,重新循环计数,进行仿真测试

3. 2位十进制计数器程序,要求计数器从00开始计数,计数到83后归零,重新循环计数,进行仿真测试

4. 半整数与奇数分频器设计

1、参考PPT第五章第二节的4位2进制计数器程序,设计一个7位2进制计数器程序,要求计算器从0开始计数,计数到59(十进制的59,看到的是二进制数)后归零,重新循环计数,进行仿真测试。把计数器程序及仿真测试图通过作业系统上交,并说明仿真测试结果正确的理由。

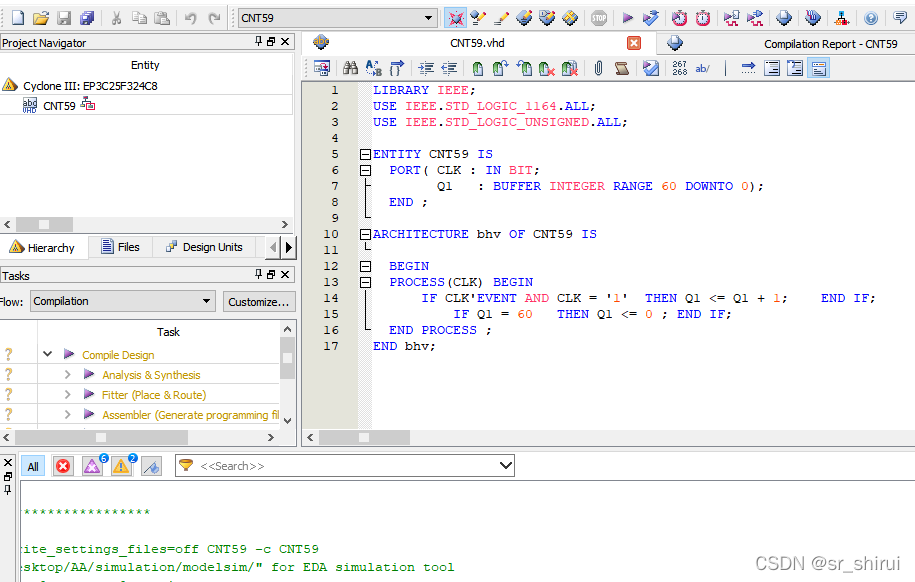

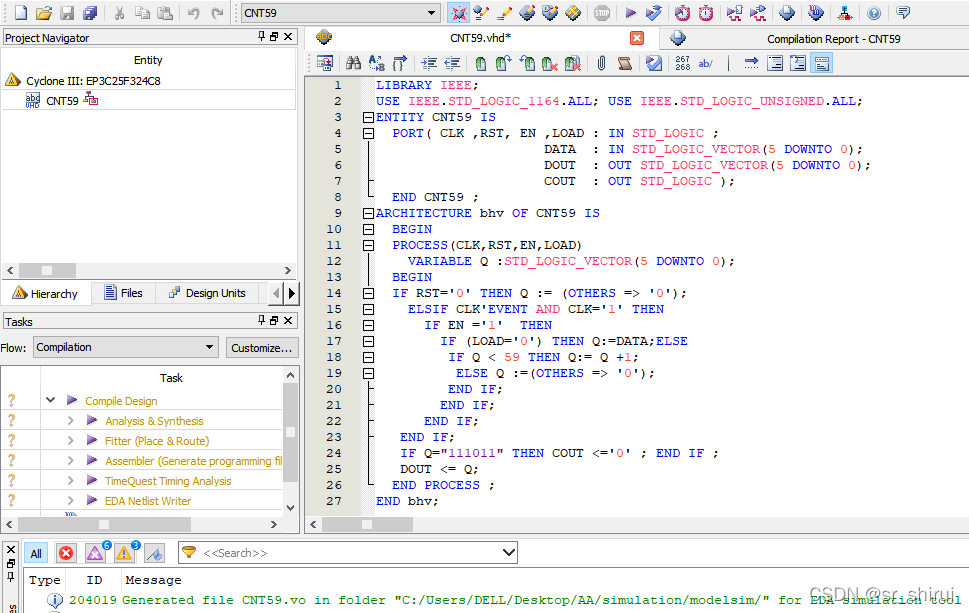

(1)十进制0-59 加法计数器的VHDL设计

加法计数器中RANGE限定了取数范围为590,在综合器编译时自动处理成六位二进制矢量。在计数器表达式中Q,=Q+1可见,Q应该具有两种端口模式特性,同时他的输入特性应该是反馈方式,因此定义Q的端口模式为buffer。最后判断当Q累加为60时,将Q置零,这样Q即显示为059的累加器。

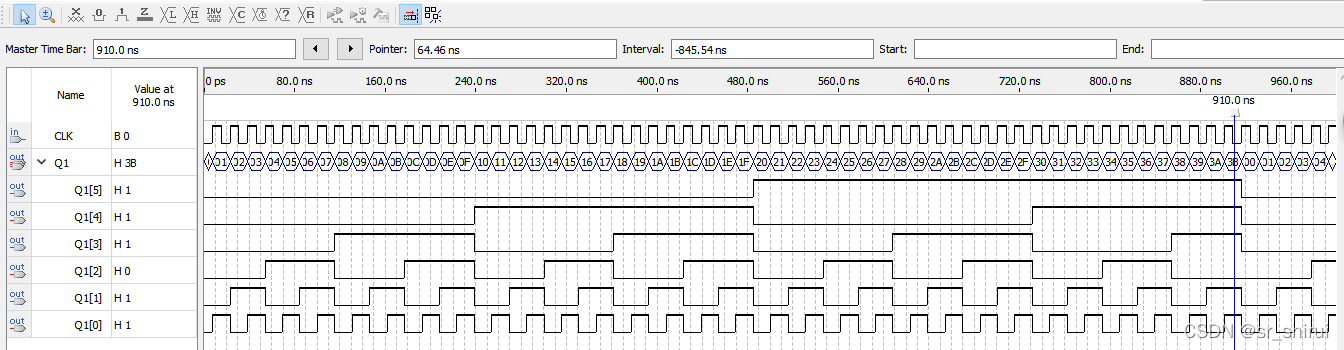

在如下的仿真图中,在第910ns时,Q1=3B(H)=111011(B)=59(D),在下一时刻Q1即为0,加法计数器计数成功。

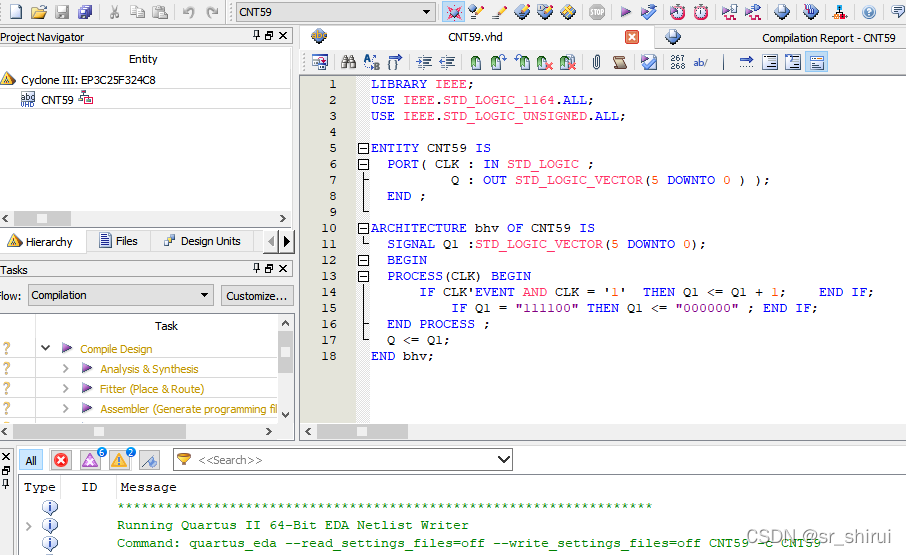

(2)十进制0-59 更常用的计数器的VHDL设计

在(2)中,与(1)不同的是电路的所有端口的数据类型都定义为标准逻辑位或位矢量,且定义了中间节点信号。这样的好处是比较容易与其他电路模拟接口。其中,在判断时,当Q1=111100(B)=60(D)时,Q1 <= “000000” 使其置零。

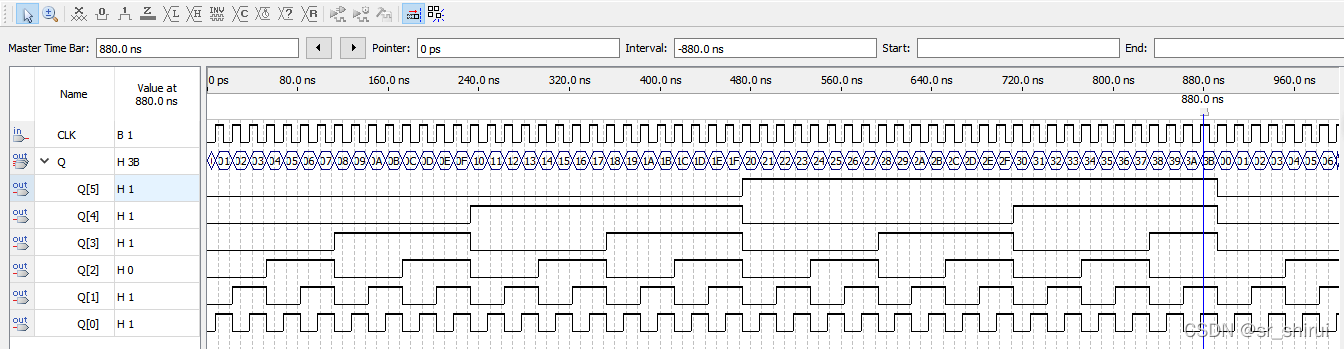

其仿真波形图与(1)相同,在第880ns时,Q1=3B(H)=111011(B)=59(D),在下一时刻Q1即为0,这种更常用的计数器计数成功。

(3)十进制0-59 实用计数器的VHDL设计

在本计数器中一个带有异步复位和同步加载功能的0~59(D)加法计数器。

其中程序功能分别为:时钟信号CLK,复位信号RST,时钟使能信号EN,加载信号LOAD,输出进位信号COUT。

程序思想:当RST低电平时计数寄存器清零,测试时钟上升沿,计数器高电平使能,允许计数。与之控制低电平,允许加载。计数小于59,继续累加,否则计数清零。当计数为59时,进位输出为1,否则进位输出0。最后将寄存器的值输出端口。

其仿真图与下一种描述相同。

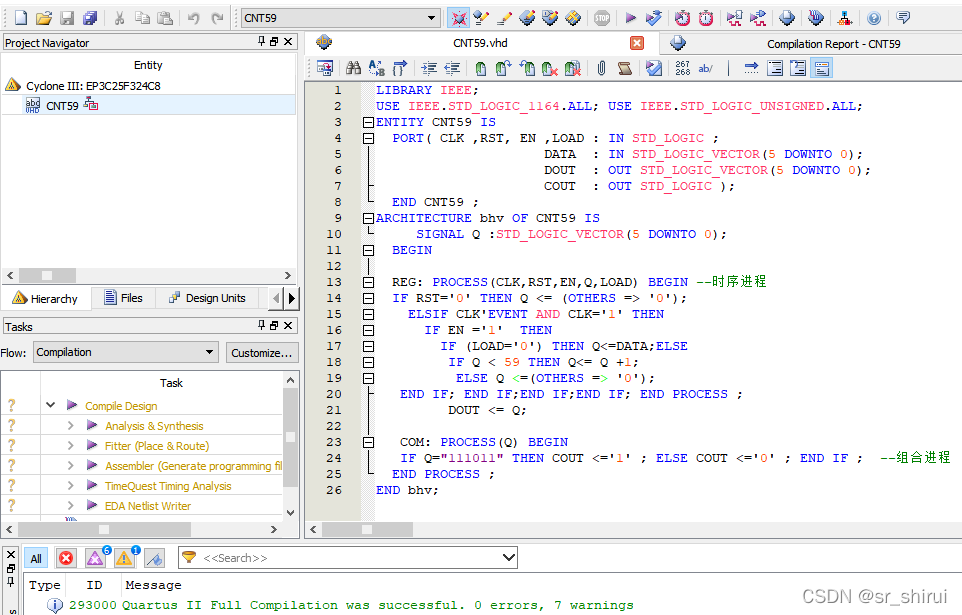

(4)十进制0-59 实用计数器的VHDL设计 (另一种方式描述)

在(3)的语句中含有两个独立的IF语句,第一个IF语句产生了计数器序列电路,第二个IF语句产生一个纯组合逻辑的多路选择器。

实际上,从程序的结构上讲,更一般更常用的表述是,将这两个独立的IF语句分别用两个独立的进程语句来表达,一个为时序进程,另一个为组合进程。

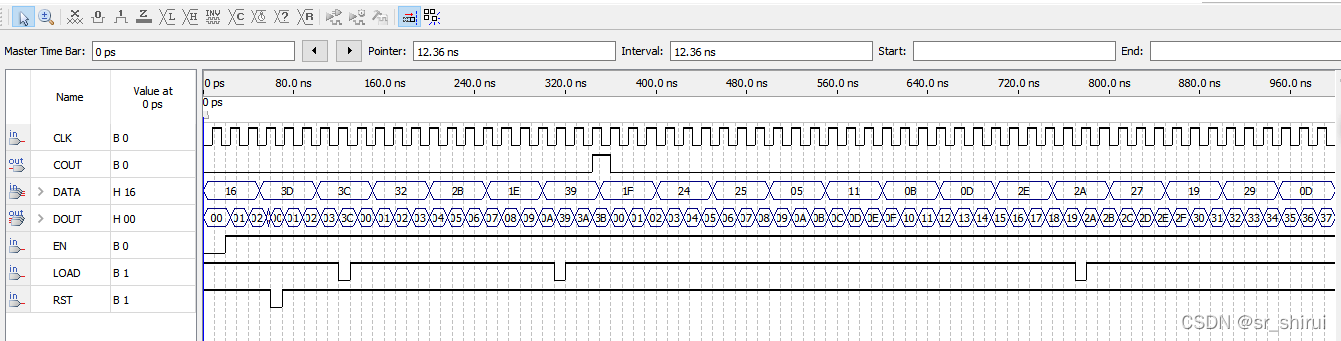

为方便观察将DATA和DOUT设置为16进制。

输出进位COUT在约为350ns时为1,其他时刻为0,这是由于在350ns时DOUT=3B(H)=59(D)

当时钟使能EN为1时,DOUT开始计数。

当重置RST由0变为1后,DOUT重新从0开始计数。

当LOAD有一个下降沿时,将输入DATA中的数据加载到输出DOUT中,再一次为基础向后计数。

再约为350ns后DOUT=3B(H)=59(D),计数器重新从0来计数。

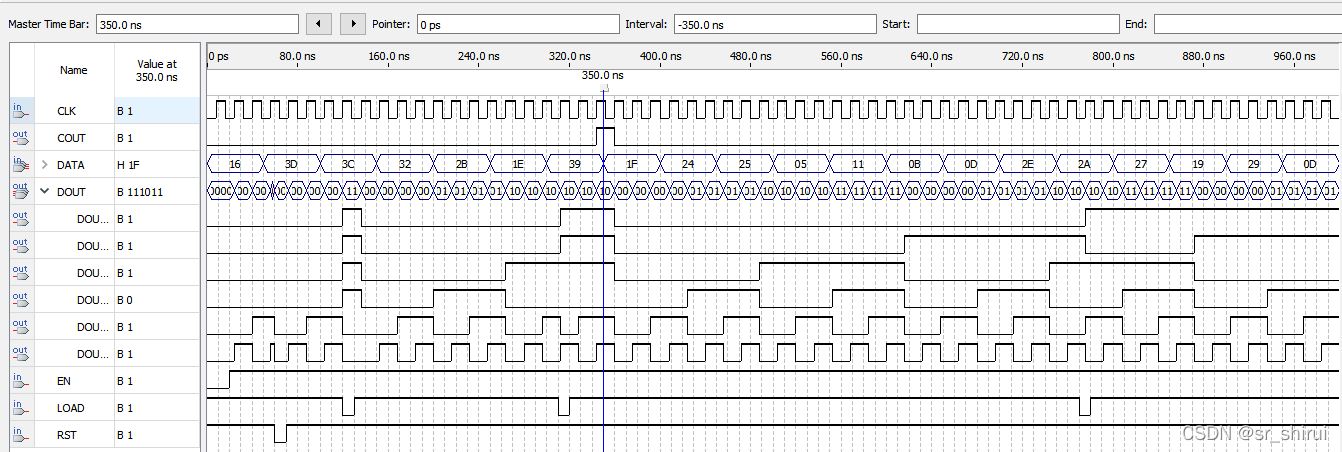

再下图中可以更清晰地看到在第350ns时情况,DOUT为111011(B)=59(D),输出进位COUT=1。

1、参考PPT第五章第二节的1位实用十进制计数器程序,设计一个2位十进制计数器程序,要求计数器从00开始计数,计数到53(十进制的53,看到的是十进制数53)后归零,重新循环计数,进行仿真测试。把计数器程序及仿真测试图通过作业系统上交,并说明仿真测试结果正确的理由。

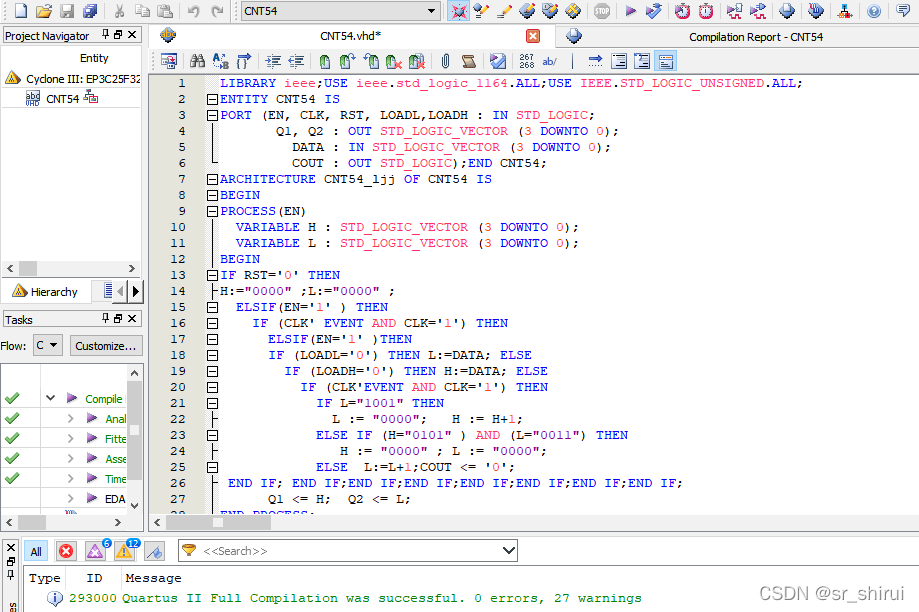

(1)二位 十进制计数器CNT54 (从0计数至53)

在本计数器中一个带有异步复位和同步加载功能的0~53(D)加法计数器。

其中程序功能分别为:高位H与Q1,低位L与Q2,时钟信号CLK,复位信号RST,时钟使能信号EN,输出进位信号COUT,高位加载信号LOADH,低位加载信号LOADL。(DATA是四位二进制随机数)

程序思想:当RST低电平时计数寄存器清零,测试时钟上升沿,计数器高电平使能,允许计数。与之控制低电平,允许加载。当低位L大于9时,低位L计数清零并向高位H进一。当计数为53时,高位与低位都清零,进位输出为1,否则进位输出0。最后将寄存器的值输出端口。

为方便观察将DATA和Q1,Q2设置为Unsigned Decimal(无符号十进制)。

依次检测下列条件:

1)【CLK是输入时间脉冲信号】

2)【当时钟使能EN=1时,Q1Q2开始计数,若EN=0,则Q1Q2保持原数据】

如:前20ns,EN=0,Q1Q2数据不变。

3)【当重置RST由1变为0后,Q1 Q2重新从0开始计数】

如:在第390ns,RST=0,Q1 Q2从0开始计数。

4)【当LOADH有一个下降沿时,将输入DATA中的数据加载到输出Q1中,再以此为基础向后计数】

如:在第110ns时,LOADH=0,则在下一时刻Q1=DATA=4。

5)【Q1 Q2=53(D)后,输出进位COUT=1,计数器重新从0计数】

如:在第200ns时,Q1 Q2=53(D),则在第210ns,进位COUT=1,并计数器从0开始计数。

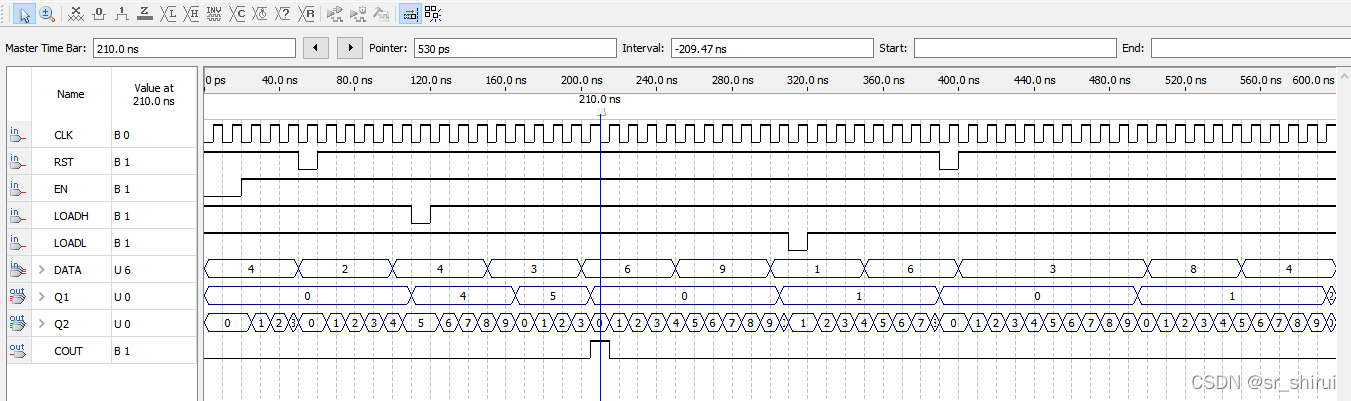

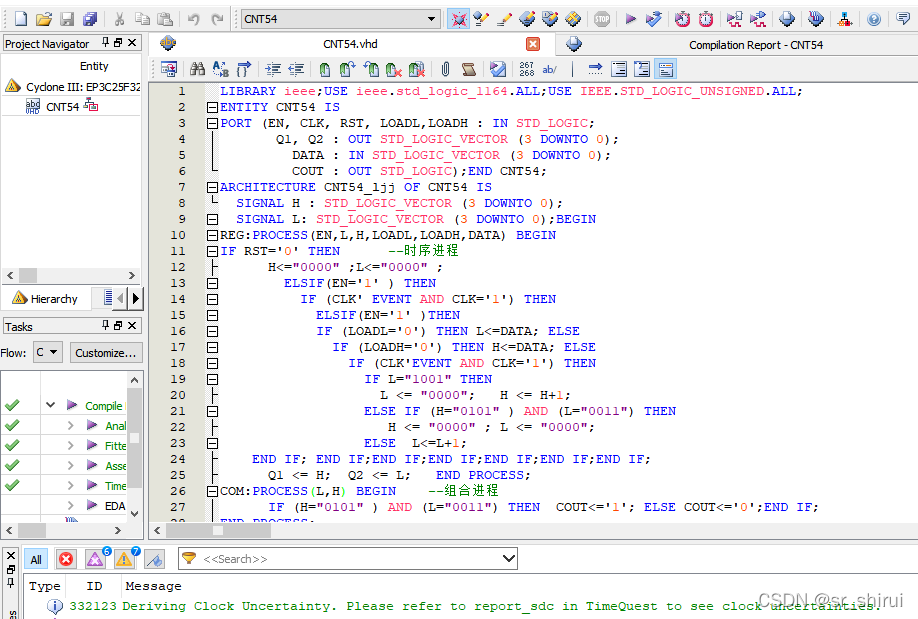

(2)两位 十进制计数器CNT54 的VHDL设计 (另一种方式VHDL描述)

在(1)的语句中含有两个独立的IF语句,第一个IF语句产生了计数器序列电路,第二个IF语句产生一个纯组合逻辑的多路选择器。

实际上,从程序的结构上讲,更一般更常用的表述是,将这两个独立的IF语句分别用两个独立的进程语句来表达,一个为时序进程,另一个为组合进程。

其仿真波形图同上

代码附录:

LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT54 IS

PORT (EN, CLK, RST, LOADL,LOADH : IN STD_LOGIC;

Q1, Q2 : OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

DATA : IN STD_LOGIC_VECTOR (3 DOWNTO 0);

COUT : OUT STD_LOGIC);END CNT54;

ARCHITECTURE CNT54_ljj OF CNT54 IS

BEGIN

PROCESS(EN)

VARIABLE H : STD_LOGIC_VECTOR (3 DOWNTO 0);

VARIABLE L : STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

IF RST='0' THEN

H:="0000" ;L:="0000" ;

ELSIF(EN='1' ) THEN

IF (CLK' EVENT AND CLK='1') THEN

ELSIF(EN='1' )THEN

IF (LOADL='0') THEN L:=DATA; ELSE

IF (LOADH='0') THEN H:=DATA; ELSE

IF (CLK'EVENT AND CLK='1') THEN

IF L="1001" THEN

L := "0000"; H := H+1;

ELSE IF (H="0101" ) AND (L="0011") THEN

H := "0000" ; L := "0000";

ELSE L:=L+1;COUT <= '0';

END IF; END IF;END IF;END IF;END IF;END IF;END IF;END IF;

Q1 <= H; Q2 <= L;

END PROCESS;

END CNT54_ljj;

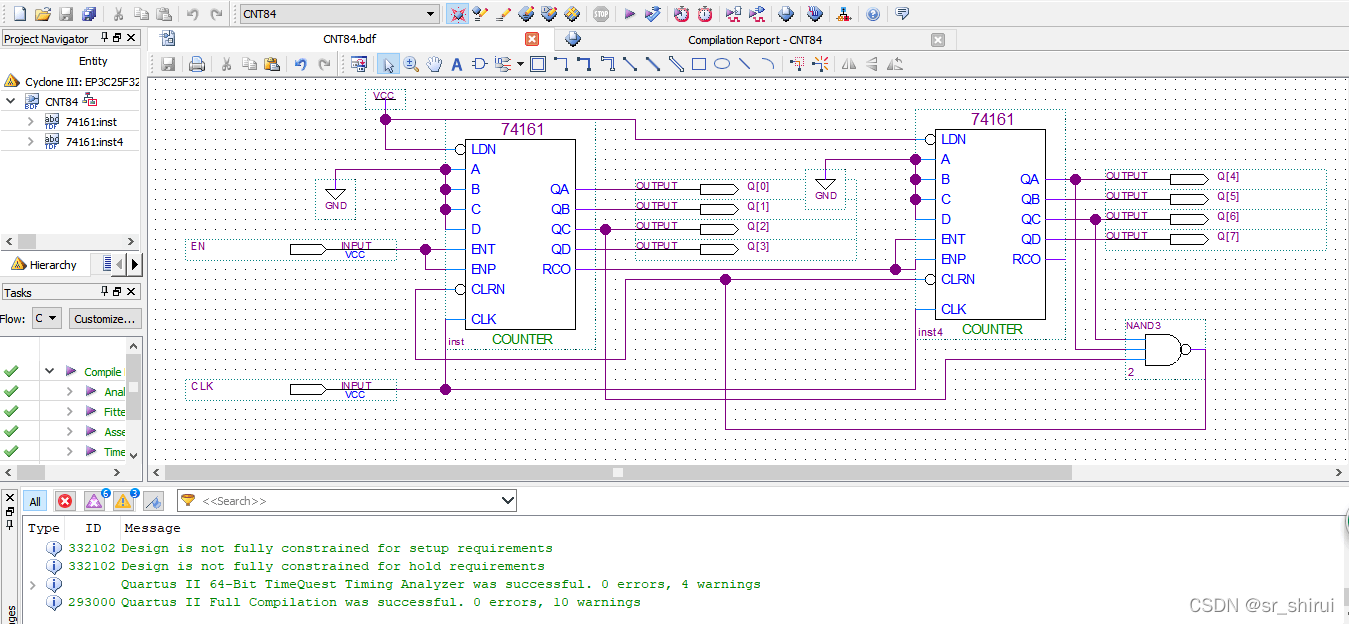

1、参考以前学习过的数字电路课程,用数字电路计数器芯片(如74LS161,162,90等),用电路图形式(计数器元件可以从系统中选择)设计一个2位十进制计数器程序,要求计数器从00开始计数,计数到83后归零,重新循环计数,进行仿真测试。把计数器设计图形及仿真测试图通过作业系统上交,并说明仿真测试结果正确的理由。

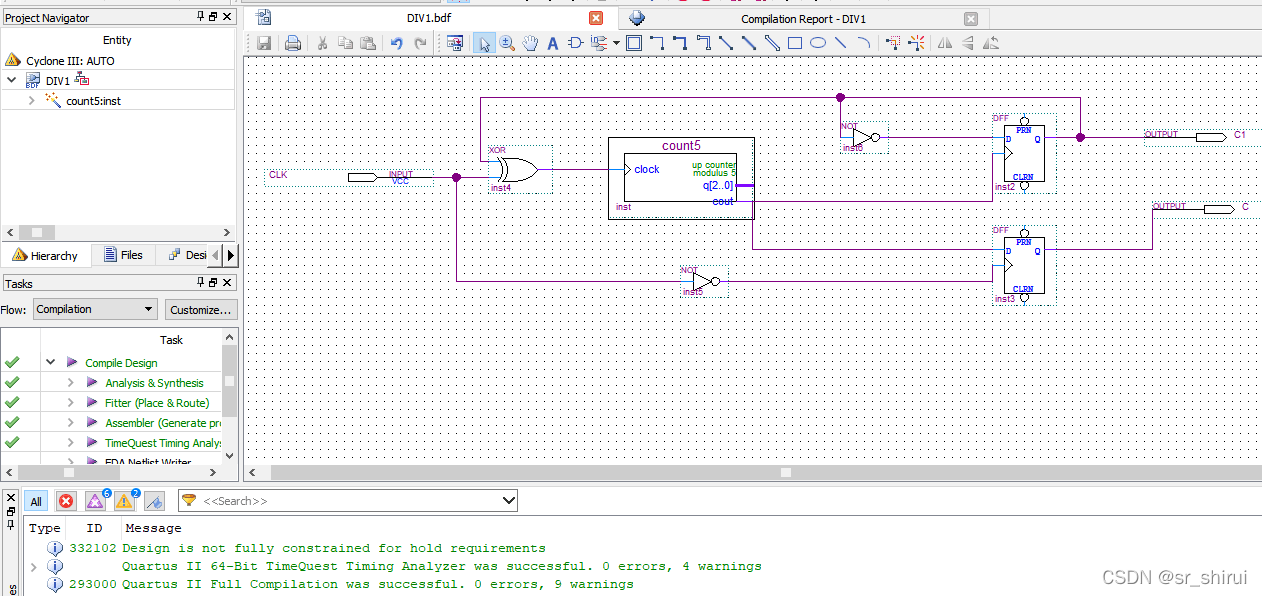

1、设计电路原理图

设计含有时钟使能及进位扩展输出的两位十进制计数器。可以用JK/D触发器、双十进制计数器74LS390或者十进制计数器74LS160和其他一些辅助元件来完成。

(1)硬件设计思想:

24<84<28,因此在设计中要用到两片74161芯片。这是一个CNT84,计数至84(0101 0100)时,下一时刻当从0开始计数;即当Q6 Q4 Q2都为1时,将0下载进计数器中;因此使用3与非门连接Q6 Q4 Q2,输出端连CLRN即可清零。

(2)引脚功能:

输入有异步清零控制端CLRN、工作使能控制端ENP、ENT和时钟输入端CLK,输出有BCD码计数值输出端Q3~Q0,进位输出端RCO。

(3)步骤:

新建BDF文件,保存工程。将所需要的元器件和引脚拖入区域内并完成连接,如图所示

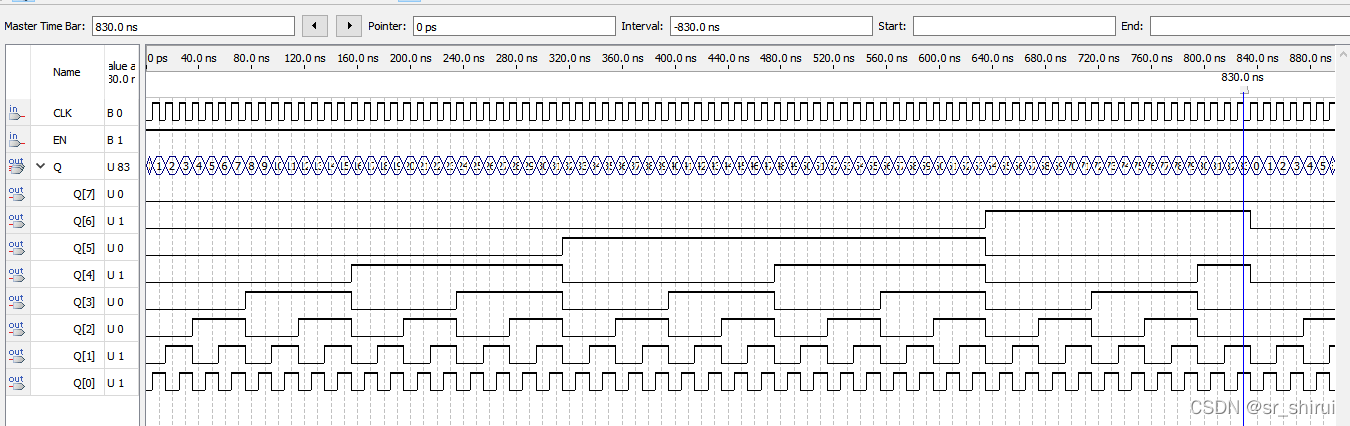

2.仿真图验证

建立VWF文件,仿真后得到结果如下图,

计数器从零开始按自然顺序计数,在第830ns时,Q为83(unsigned Dec),然后下一时刻Q为0重新按顺序计数,证明设计正确。

其中EN为使能管脚,CLK为输入时钟信号。

4.参考PPT第五章的实验与设计,对其中的5-3(半整数与奇数分频器设计),这里包含图5-23 、例5-20、图5-25相对应的电路图及程序。对不同的分频器进行仿真测试,如果修改M3(模3)的计数器变成M5或M7,会得到怎样的结果,把仿真测试结果通过作业系统上交,说明电路及程序的功能。

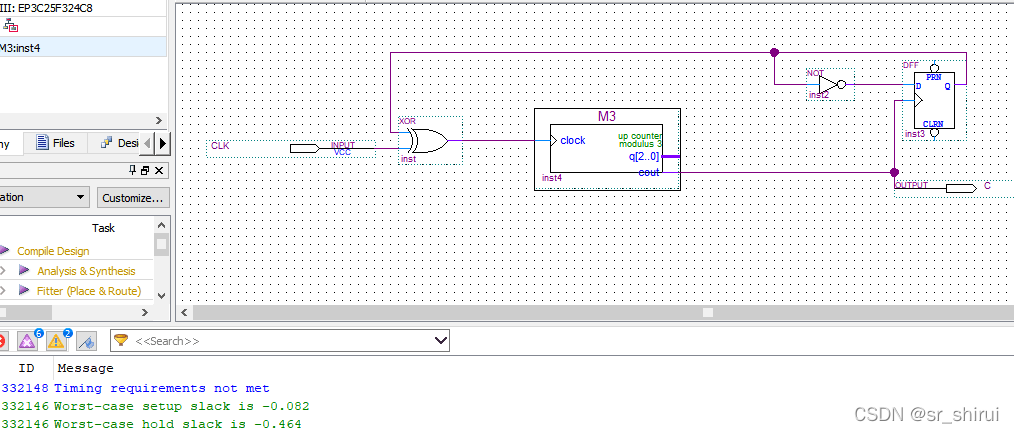

(1)如图所示的电路是一个占空比为50%的任意奇数次分频电路。其中的count5是一个模5计数器,它可以设置为任意模计数器,实现整个电路任意次奇数分频功能,且占空比均为50%。

注意:其中,模3模5等的计数器设计可以通过VHDL来进行底层电路模块设计,也可以通过LPM设计模块。

在本实验中,模3计数器通过LPM设计,再导入到元件库中,以供分频电路使用。

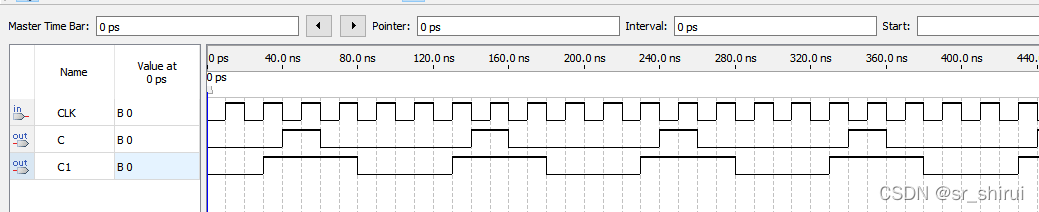

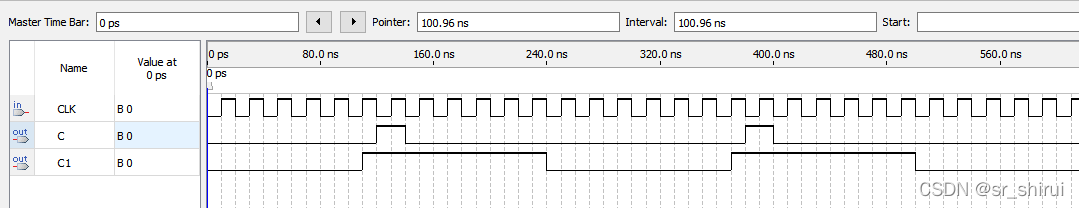

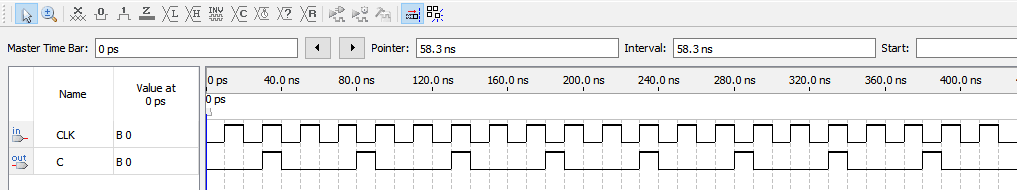

A. 下图是将电路中的计数器换成 模3计数器(M3) 后的仿真图。C1的输出呈现50%占空比5分频信号。

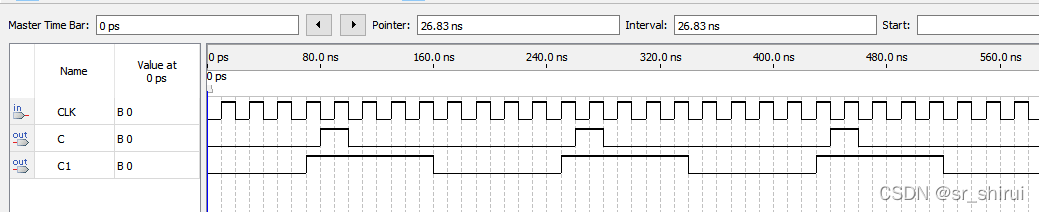

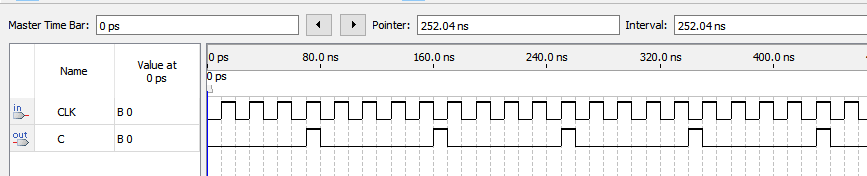

B. 下图是将电路中的计数器换成 模5计数器(M5) 后的仿真图。C1的输出呈现50%占空比9分频信号。

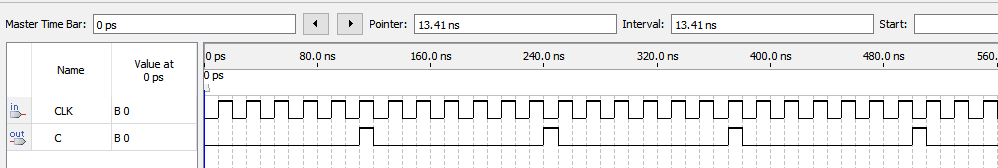

C. 下图是将电路中的计数器换成 模7计数器(M7) 后的仿真图。C1的输出呈现50%占空比13分频信号。

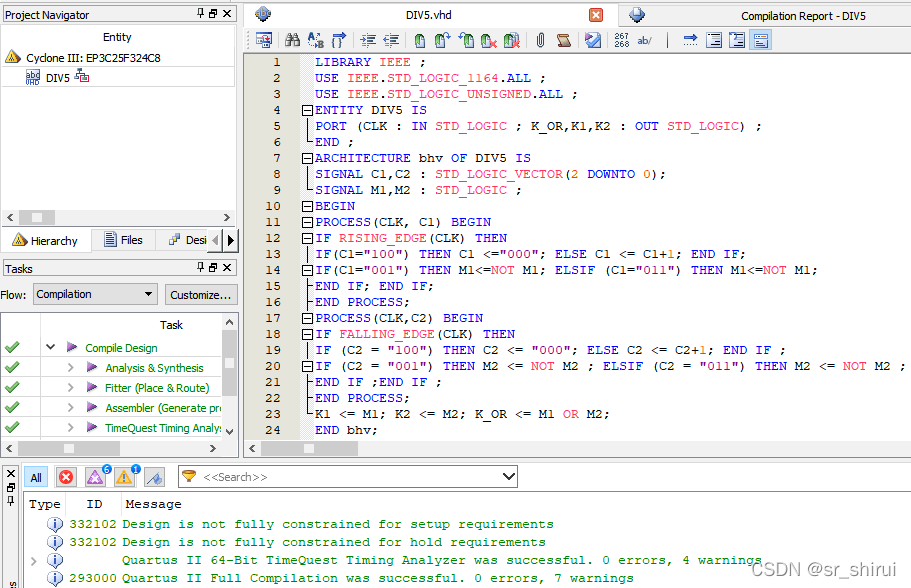

(2)另一种设计50%占空比任意奇数分频的设计思路是使用VHDL语言。下图是50%占空比5分频的VHDL程序。

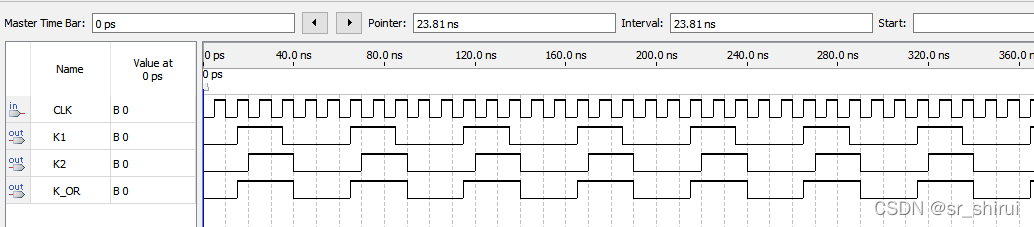

下图是50%占空比5分频的VHDL设计程序的仿真图。输出K_OR实现了该程序功能。

(3)使用数字系统常用常需要另一种分频电路,即半整数分频。只要对电路稍加改变就可以得到任意半整数分频电路,对如下图所是的电路只要改变M3(模3计数器)模块的技术数值,即可改变此电路所需要的半整数分频结构。

A. 如下图是上图的仿真波形,输出C显示2.5分频

B. 下图是将电路图中计数器模块改为 模5计数器 后的仿真波形,输出C显示4.5分频

C. 下图是将电路图中计数器模块改为 模7计数器 后的仿真波形,输出C显示6.5分频

本文详细介绍了使用VHDL设计不同类型的计数器,包括7位2进制计数器、2位十进制计数器以及2位十进制实用计数器,涉及复位、加载、进位等功能。通过仿真测试验证了计数器在达到预设数值后能够正确复位并循环计数。此外,还探讨了半整数与奇数分频器的设计,展示了如何通过调整模数实现不同分频效果。

本文详细介绍了使用VHDL设计不同类型的计数器,包括7位2进制计数器、2位十进制计数器以及2位十进制实用计数器,涉及复位、加载、进位等功能。通过仿真测试验证了计数器在达到预设数值后能够正确复位并循环计数。此外,还探讨了半整数与奇数分频器的设计,展示了如何通过调整模数实现不同分频效果。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?