我们经常会在各个介绍时序电路或锁存器的文章和书中看到综合后的电路中最好不要包含锁存器?那这是为什么呢

我们从以下几方面来看:

1.电路稳定性方面

锁存器对毛刺敏感,会使电路变得不稳定;

2.时序方面

不利用进行时序分析,静态时序分析器通常会做出与锁存器透明有关的错误假设;锁存器本身的时序也是模糊的,例如,在分析含D锁存器的电路时,工具无法确定你是想在时钟前沿还是在时钟后沿将数据传输到输出端

3.资源消耗方面

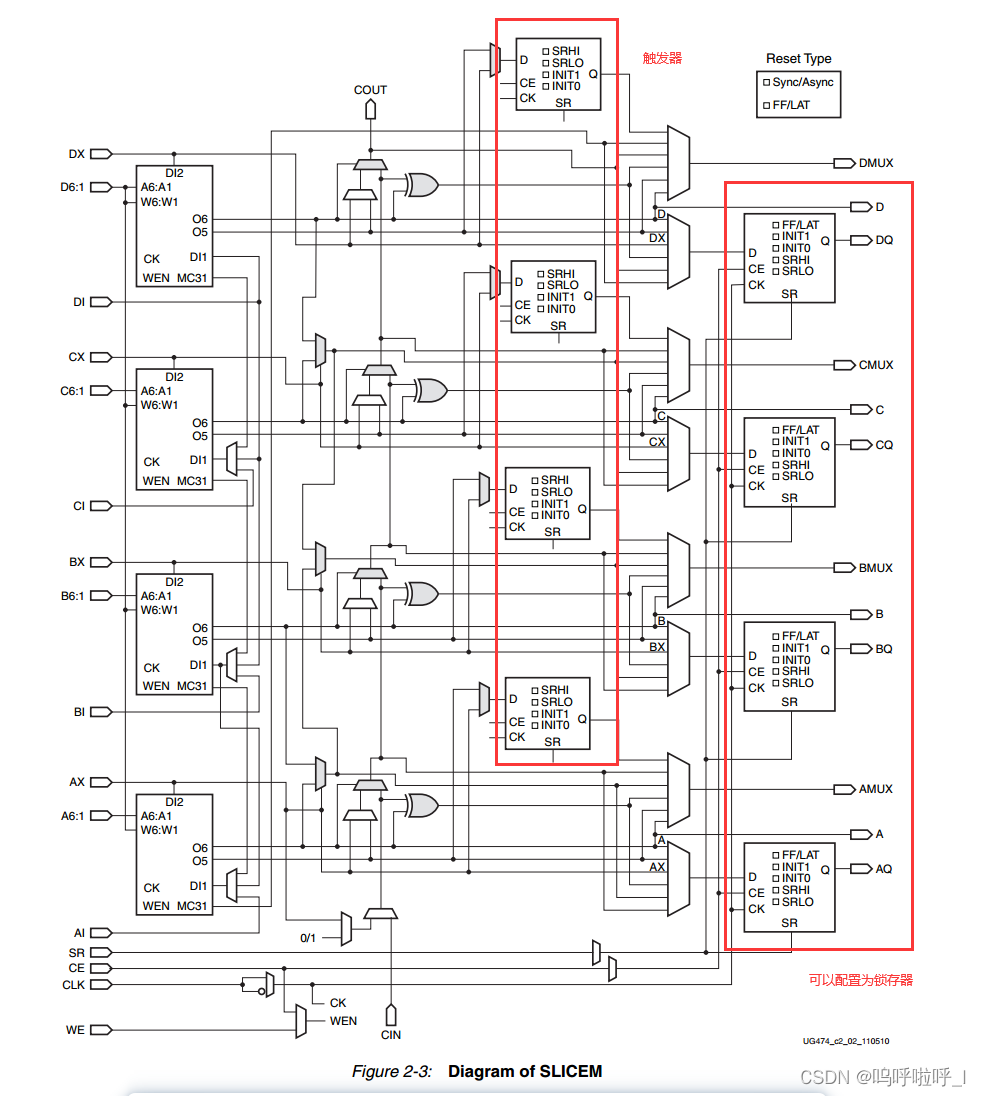

在Xinlinx FPGA中,我们以SLICEM举例,每个SLICEM包含8个触发器,其中有四个可以配置为锁存器;但是如果这四个被配置为锁存器那另外四个触发器将不能使用,会造成资源的浪费。

参考文章:

本文讨论了在时序电路设计中避免使用锁存器的原因,包括对电路稳定性的影响、时序分析中的问题以及在资源消耗上的浪费,以XilinxFPGA中的SLICEM为例进行了说明。

本文讨论了在时序电路设计中避免使用锁存器的原因,包括对电路稳定性的影响、时序分析中的问题以及在资源消耗上的浪费,以XilinxFPGA中的SLICEM为例进行了说明。

3181

3181

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?