在说明建立时间和保持时间为何为负的情况下,首先可以看看建立时间Tsu和保持时间Th的由来,可参考如下两篇文章:

建立时间和保持时间理解_为什么要满足建立时间和保持时间-CSDN博客

ic基础|时序篇:浅谈负的建立时间和保持时间成因_触发器建立时间负的-CSDN博客

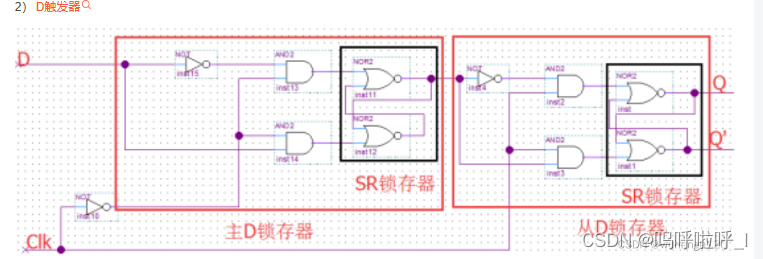

D触发器的结构如图所示,在时钟上升沿,对于触发器来讲,主锁存器此时已经锁存数据D,并且从锁存器开始准备锁存数据。 由于主锁存器锁数据也是需要时间的,即在clk上升沿之前,clk=0的时候,主锁存器就开始锁存数据了(数据从D到主锁存器的输出需要时间),所以要有建立时间(即clk上升沿之前数据保持稳定的时间);

在clk 从0~1 上升沿变化时,此时AND2 门的输入需要t1时间才会变成1,即需要t1时间才会开始锁存数据D;

如果在上升沿时,数据突然变化(即不满足保持时间要求),那么此时如果D需要在t2时间传到与门AND2处,如果t2 < t1, 那么主锁存器锁存的数据将是数据D变化后的值;所以,clk上升沿后数据需要保持一段时间;

建立时间为负

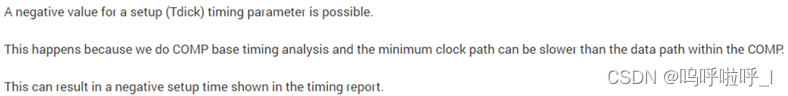

建立时间为负是可能的。上图中的意思大致是这种情况发生在最小的时钟路径可能会比数据路径慢。

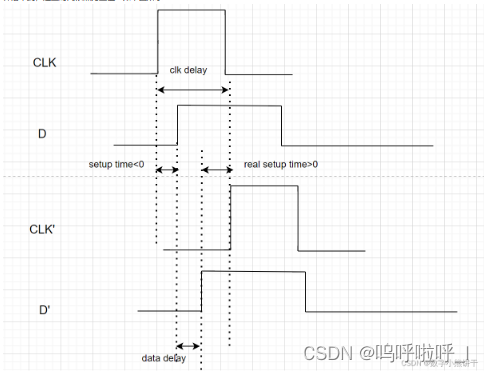

结合D触发器结构图及上述建立时间产生的原因,当触发器内部时钟路径的延迟相对于数据路径较大时,时钟从源点传递到主D锁存器的与门时需要花费很长的时间,而数据从D端口传递到主锁存器的输出需要的时间要小于这部分时间,即使数据相对源节点的clk上升沿晚一会出发,依然可以先于作用在主D锁存器与门的clk’到达,并且稳定输出在主D锁存器的输出。

可以参考下面这篇文章:

ic基础|时序篇:浅谈负的建立时间和保持时间成因_触发器建立时间负的-CSDN博客

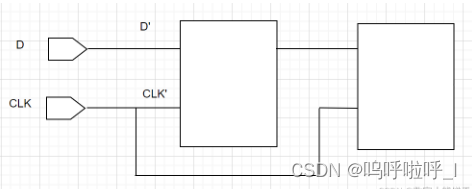

将图中的D’认为是主D锁存器的输出,可以发现D’先于clk’到达,就是上述介绍的情况,可以对应着理解。

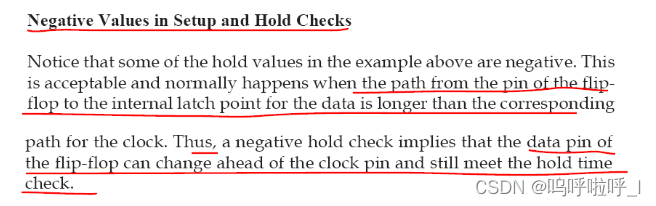

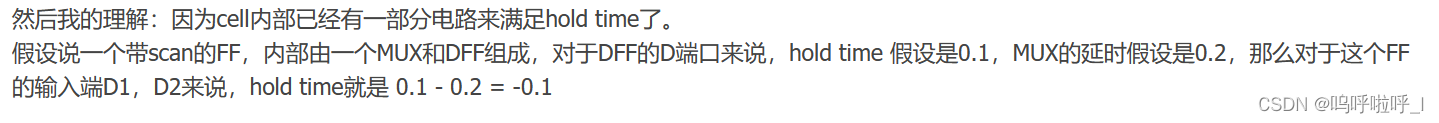

保持时间为负

对于保持时间为负,我们对应着上图理解,由于数据路径延时相较于时钟路径延时导致很大,即使数据比时钟早输入,但依然会比时钟沿晚到,在真正的所存点依然能够满足保持时间要求。

从二者为负的原因可知,setup和hold不能同时为负值,而且二者之和必须为正。

参考

然后也看到一个个人认为比较正确的,对于hold up为负为何数据路径时延相对较大的解释,链接如下:

保持时间为负 - 后端讨论区 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

9658

9658

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?