DDS信号发生器原理

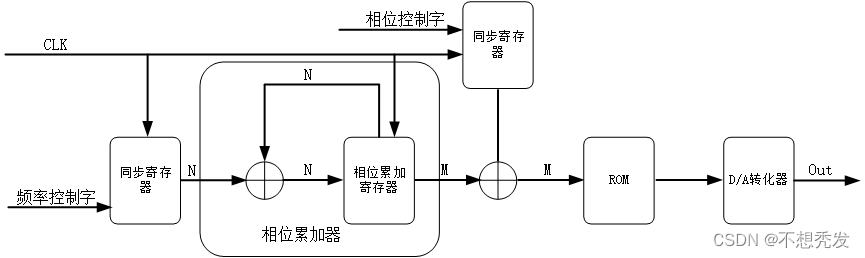

rom读取地址=频率控制字+相位累加器+相位控制字。DDS数字电路原理如图:

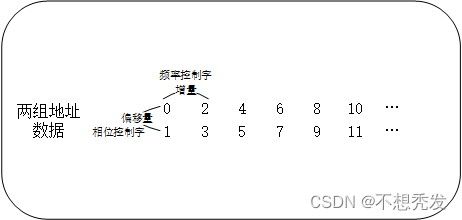

频率控制字改变rom地址增量,相位控制字改变rom地址偏移量。两者关系如图:

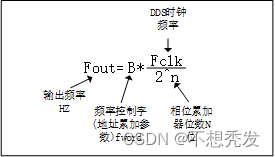

信号发生器输出信号频率与DDS时钟频率关系如下。

注

相位控制字寄存器位宽与rom位宽保持一致。

这里相位累加器位数为 N 位(N 的取值范围实际应用中一般为 24~32),相当于把正弦信号在相位上的精度定义为 N 位,所以其分辨率为1/2^n。

N越大信号输出频率精度越高,输出频率下限值越低。

相位控制字改变信号初相位置。

代码示例

module dds_test(

input clk ,

input rst_n ,

input [31:0] f_word ,

input [11:0] p_word ,

output [15:0] data_out //rom输出位宽

);

reg [31:0] r_f_word ; //频率控制字寄存器

reg [11:0] r_p_word ; //相位控制字寄存器 位宽与rom位宽保持一致

reg [31:0] acc ; //相位累加寄存器

reg [7:0] address_rom ; //rom地址寄存器 假设rom地址位宽为8位

//同步寄存器

always @(posedge clk or negedge rst_n)

if(!rst_n)

r_f_word <= 32'b0 ;

else

r_f_word <= f_word ;

always @(posedge clk or negedge rst_n)

if(!rst_n)

r_p_word <= 12'b0 ;

else

r_p_word <= p_word ;

always @(posedge clk or negedge rst_n)

if(!rst_n)

acc <= 32'b0;

else

acc <= acc + r_f_word ;

always @(posedge clk or negedge rst_n)

if(!rst_n)

address_rom <= 12'b0;

else

address_rom <= acc[31:24] + r_p_word;

//rom列化

dist_mem_gen_0 dist_mem_gen_0_inst (

.a(address_rom), // input wire [7 : 0] a

.spo(data_out) // output wire [15 : 0] spo

);

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?