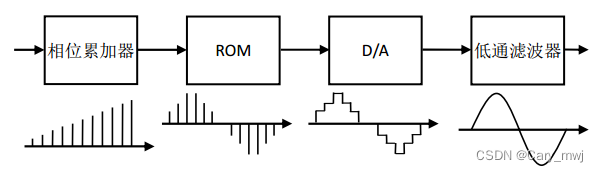

一、DDS原理

DDS即直接数字合成频率,由相位累加器、波形数字表、相位调制器组成。

二、 频率输出公式

其中是FPGA系统时钟,

是正弦信号的相位精度(生成一个周期点数为

的正弦信号,得到最小的相位间隔为

),

是频率控制字。

当等于1时,

,

,其中

为FPGA系统时钟的周期,

为输出信号的周期。此时该公式理解为FPGA生成频率为

的正弦信号的一个周期所需要花费的时间为

。(FPGA每个系统时钟周期向波形数字表中查询一个值,共

个值,每隔1个值取一次)。

当大于1时,

,

。此时该公式理解为FPGA生成频率为

的正弦信号的一个周期所需要花费的时间为

。(FPGA每个系统时钟周期向波形数字表中查询一个值,共

个值,每隔

个值取一次)。

1442

1442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?