导读

本文主要包括三部分内容:MicroBlaze MCS IP 核的总体介绍、MicroBlaze MCS IP 核的配置页、MicroBlaze MCS IP 核的实际使用(包括在 Vivado 工程下实例化和 SDK 中开发调试)。

目录

一 MicroBlaze Micro Controller System(3.0)IP 介绍

二、使用 MicroBlaze Micro Controller System(3.0)IP

1.1 从 IP Catalog 中引入 MicroBlaze MCS IP

1.2 MicroBlaze MCS IP 常用的属性配置:

2 在 Xilinx SDK 中进行 MicroBlaze MCS 嵌入式软件的开发与调试

一 MicroBlaze Micro Controller System(3.0)IP 介绍

1 总体描述

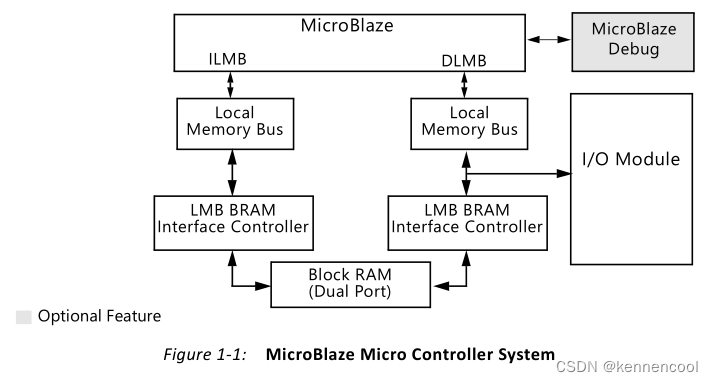

MicroBlaze Micro Controller System(MCS)核心是一个用于控制器应用的完整处理器系统。它是高度集成的,包括 MicroBlaze 处理器、用于程序和数据存储的本地存储器以及实现一组标准外围设备的紧密耦合 I/O 模块。其中:

- MicroBlaze Processor:MicroBlaze Processor 是 IP 核的主要处理器单元。它是一个高度可定制的处理器,用户可以根据应用的需要进行配置和定制。MicroBlaze 支持多种选项,包括指令和数据缓存,乘法和除法指令,浮点单元等。用户可以根据应用的性能和资源要求来选择适当的配置。

- Local Memory:Local Memory 是 MicroBlaze 核心附带的存储器单元,用于存储指令和数据。

- I/O Module:输入/输出模块允许 MicroBlaze 与外部设备和外设进行通信。它提供了一系列接口和控制器,以支持各种输入和输出接口协议,如 UART(通用异步收发传输)、SPI(串行外围设备接口)、GPIO(通用输入/输出)等,从而实现完整的处理系统功能。

- Debug:Debug 模块是 MicroBlaze 的一个重要组成部分,它提供了对处理器的调试和故障排除功能。通过调试模块,用户可以在程序运行时观察寄存器状态、监控程序执行、设置断点以及进行其他调试操作。

2 各部分介绍

2.1 MicroBlaze Processor

MicroBlaze Processor 是一个基于 Harvard 架构的 32 位 RISC 处理器。Harvard 架构意味着指令和数据存储器是分开的,这有助于提高内存访问的并行性和性能。

MicroBlaze Processor 支持常见的整数和浮点数的算术运算(加减乘除)、逻辑运算、位级运算、比较运算、布尔运算。

注:MicroBlaze 核心是一个 32 位的处理器,这意味着它最多一次处理 32 位(4 字节)的数据。在 MicroBlaze 处理器上编写的嵌入式软件中,整数类型(如int、long 等)的最大位数是32位,而不是64位。

2.2 Local Memory

Local Memory(本地存储器)是指位于 MicroBlaze 处理器核心内部的一块用于存储数据和指令的存储器。它相对于外部存储器(如 DDR RAM)更为快速和低延迟,因为它位于处理器核心的内部,可以直接访问。

Local Memory 主要有两种类型:

- 指令存储器(Instruction Memory):用于存储处理器的指令。当 MicroBlaze 执行指令时,它会从指令存储器中获取指令,并按照指令执行相应的操作。指令存储器通常是只读的,因为在运行时不会改变指令。

- 数据存储器(Data Memory):用于存储处理器的数据。MicroBlaze 在执行程序时,需要使用数据存储器来读取和写入数据。数据存储器可以是可读写的,因为程序可能需要在运行时修改数据。

2.3 I/O Module

I/O Module 的作用是提供与外部设备进行通信的接口,允许 MicroBlaze 处理器核心与外部世界进行数据交换。

I/O Module 可以实现多种不同类型的外设接口,其中常见接口包括:

- GPIO(通用输入/输出):GPIO 是最常见的 I/O 接口之一。它允许 MicroBlaze 处理器核心与外部设备进行通信,通过设置输出管脚的电平或读取输入管脚的电平来传递数字信号。

- UART(通用异步接收/发送器):UART 是一种常用的串行通信协议,用于与其他串行设备(如计算机、传感器、通信模块等)进行数据通信。

- SPI(串行外设接口):SPI 是一种常用的串行通信协议,通常用于连接外部存储器、传感器和其他外设。

- I2C(I2C 总线):I2C 是一种常用的串行通信协议,适用于连接多个外部设备,如传感器和扩展模块。

- PWM(脉冲宽度调制):PWM 可以用来生成脉冲信号,常用于控制电机、灯光和其他需要精确调节的设备。

2.4 Debug

Debug(调试)是其中一个主要组成部分,它提供了调试和性能分析支持,帮助开发人员更好地理解和调试 MicroBlaze 处理器核心的运行。

Debug 功能的实现方式:MicroBlaze 处理器核心提供 JTAG(Joint Test Action Group)调试接口,Xilinx SDK 就是使用 JTAG 接口与 MicroBlaze 处理器建立通信以进行调试。通过 JTAG 接口,Xilinx SDK 可以对正在运行的软件进行读写寄存器、设置断点、查看内存内容和其他调试操作。

注:MicroBlaze MCS IP 核通常会默认包含一个 JTAG 调试接口,这使得可以通过 JTAG 接口连接到调试工具(如 Xilinx SDK 或第三方调试器)来进行调试。即使在 Verilog 代码中没有明确指定 JTAG 接口,Xilinx Vivado 在生成 Bitstream 时会将该接口添加到 MicroBlaze MCS IP 核中,从而允许通过 Xilinx SDK 来调试 MicroBlaze MCS IP 核中的软件。

二、使用 MicroBlaze Micro Controller System(3.0)IP

1 在 Vivado 工程中实例化 IP

1.1 从 IP Catalog 中引入 MicroBlaze MCS IP

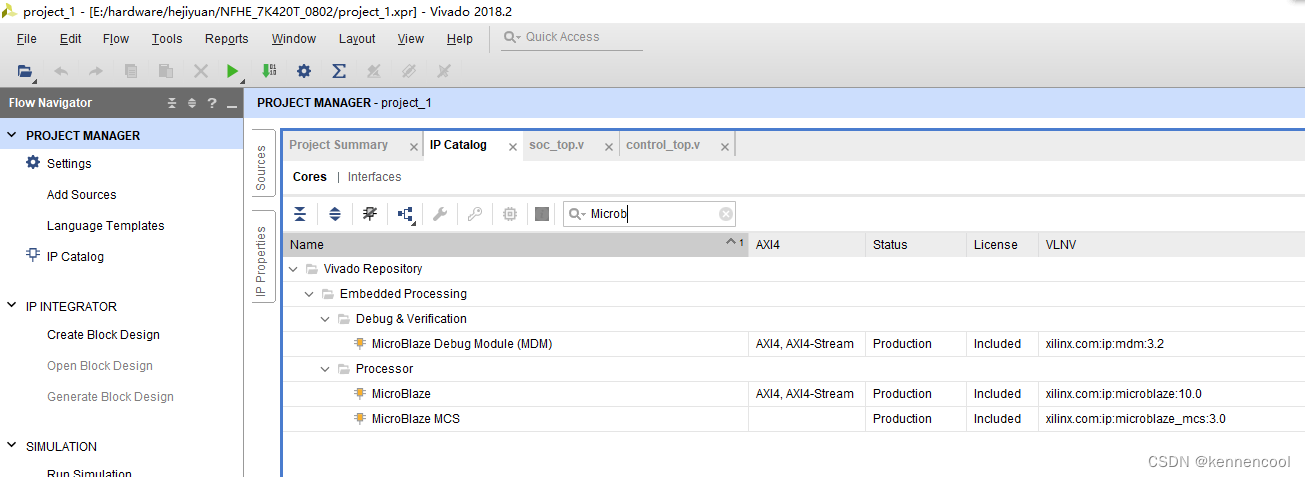

打开 Vivado 2018.2,在左侧 Flow Navigator -> PROJECT MANAGER 下点击 IP Catalog,输入“Microb”:

e

e

检索到了三个 IP,分别是:

- MicroBlaze Debug Module (MDM):一个单独的调试模块,由于 MicroBlaze MCS 中自带 Debug 部分,因此不需要使用到该 IP。

- MicroBlaze:是嵌入式处理器,可以根据特定的应用需求选择指令集、硬件加速器和其他配置,这种灵活性可以高效地利用FPGA资源。故可以作为硬件加速器、控制器和处理引擎,用于嵌入式系统的各种应用,包括通信、图像处理、数据处理等。

- MicroBlaze MCS:是一个预配置的处理器系统,包含了 MicroBlaze 处理器核、局部存储器、I/O 模块和 Debug 模块等部分,形成一个完整的嵌入式控制器系统。适用于快速构建简单的嵌入式系统,无需进行复杂的配置,适合初级用户或快速开发应用。

这里我们选择 MicroBlaze MCS 进行快速开发,双击 MicroBlaze MCS 进行 IP 配置。

1.2 MicroBlaze MCS IP 常用的属性配置:

MCS

- Input Clock Frequency (MHz):定义输入时钟频率,和外部模块输入到该 IP 的 CLK 一致。

- Memory Size:定义本地内存大小,用于存储 MicroBlaze 处理器软件程序指令和数据。如果设置太小,可能无法正常运行软件程序。

- Select MicroBlaze Optimization:如果选用 AREA,生成的 MicroBlaze 处理器将被最小化,使用一个 3 级流水线,不包含乘法器、除法器等硬件加速器;如果选用 PERFORMANCE,生成的 MicroBlaze 处理器将具有较高的性能。它使用一个 5 级流水线,并且包含一些额外的执行单元,如 barrel shifter(位移器)、multiplier(乘法器)、divider(除法器)和 pattern comparator(模式比较器)。

- Enable I/O Bus:MicroBlaze 将具有一个 I/O 总线端口,允许与外部设备进行通信。这样,您可以通过 I/O 总线接口连接外部设备,实现与 MicroBlaze 的数据交换和通信。

- Enable Debug Support:选用 DEBUG ONLY 可以支持诸如 Xilinx SDK 对嵌入式程序进行调试。

该页配置对应的模块实例化代码:

microblaze_mcs_1 your_instance_name (

.Clk(Clk), // input wire Clk

.Reset(Reset), // input wire Reset

.IO_addr_strobe(IO_addr_strobe), // output wire IO_addr_strobe

.IO_address(IO_address), // output wire [31 : 0] IO_address

.IO_byte_enable(IO_byte_enable), // output wire [3 : 0] IO_byte_enable

.IO_read_data(IO_read_data), // input wire [31 : 0] IO_read_data

.IO_read_strobe(IO_read_strobe), // output wire IO_read_strobe

.IO_ready(IO_ready), // input wire IO_ready

.IO_write_data(IO_write_data), // output wire [31 : 0] IO_write_data

.IO_write_strobe(IO_write_strobe) // output wire IO_write_strobe

);UART

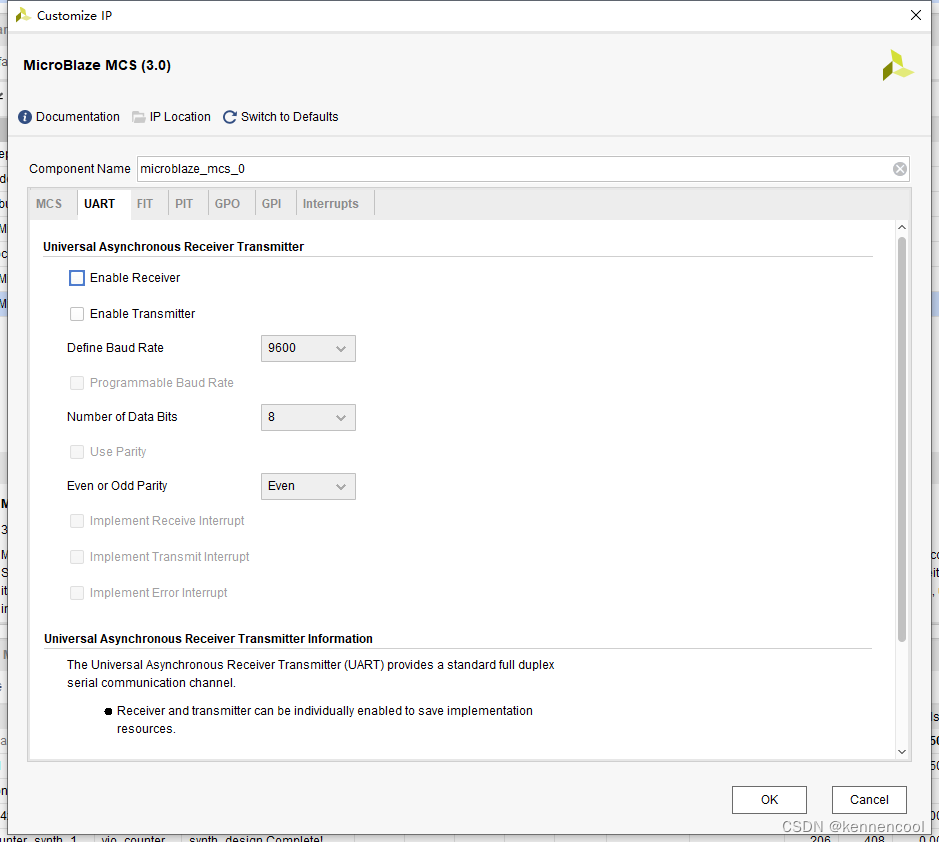

UART 配置的是实现与外部设备或通信接口进行串行通信。UART(通用异步收发传输器)是一种常见的串行通信协议,它允许将数据以逐位的方式在设备之间传输。通过配置 UART,MicroBlaze MCS 可以与其他支持 UART 协议的设备进行数据传输。

这里不做配置。

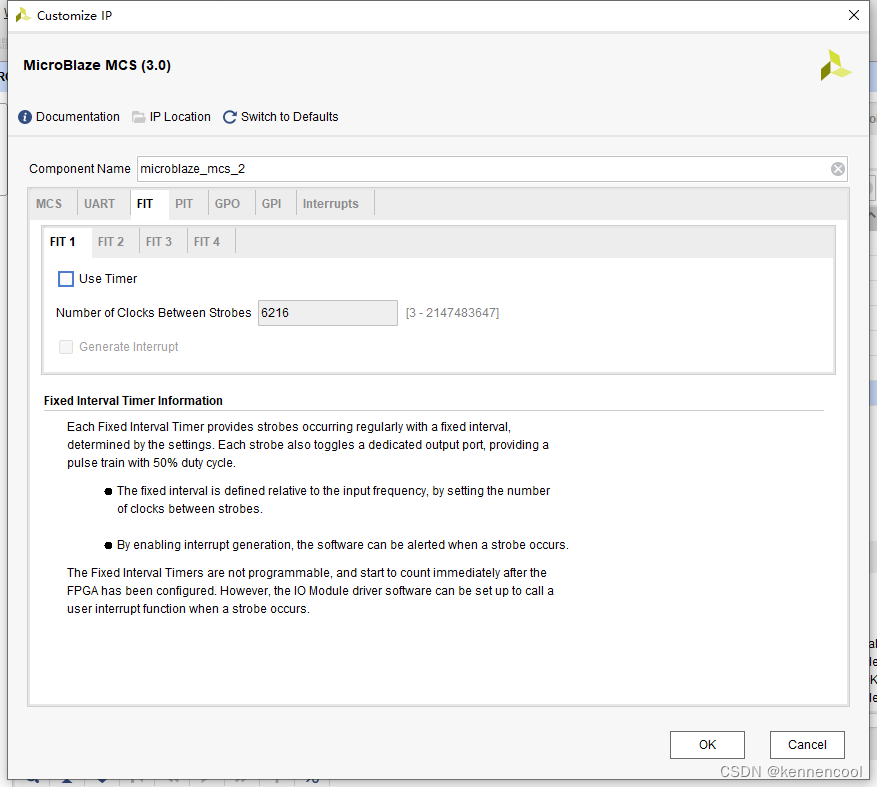

FIT

FIT 可以在特定的时间间隔触发中断,用于实现周期性的任务和时间管理。适用于许多场景:

- 实时任务调度:在实时控制系统中,某些任务需要按照固定的时间间隔进行执行,FIT 提供了一种简单的方法来实现这种周期性调度。

- 数据采集和传输:在数据采集和传输应用中,FIT 可以用来定时触发数据采集或传输的操作。

- 周期性通信:在通信系统中,FIT可以用于定时触发通信操作。例如,定时发送数据包、周期性接收数据等。

- 时间管理:FIT 可以用于时间管理和时间戳记录。例如,可以使用 FIT 定时器来记录事件发生的时间戳,或者用 FIT 来实现简单的实时时钟功能。

- 节能和功耗管理:在一些低功耗应用中,可以使用 FIT 来实现周期性的休眠和唤醒操作,从而节约系统能量消耗。

这里不做配置。

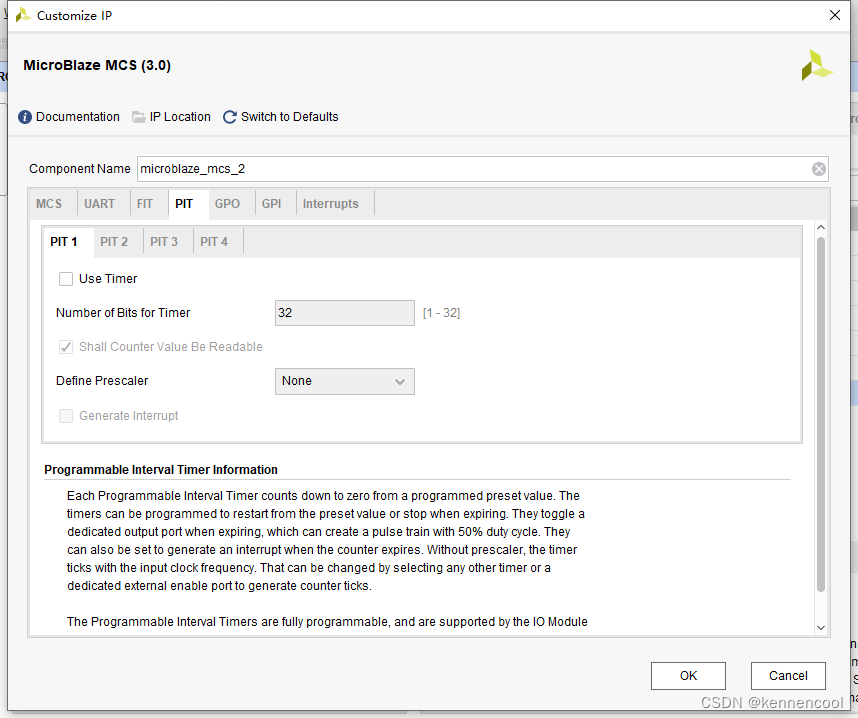

PIT

PIT(Programmable Interval Timer)可以通过设置定时器的周期来产生周期性的中断信号。可以自由设置定时器的计数周期实现不同的定时需求,可以认为是更灵活版本的 FIT。定时器的计数周期和使能信号均在 SDK 的嵌入式软件中根据需要进行设置。

这里不做配置。

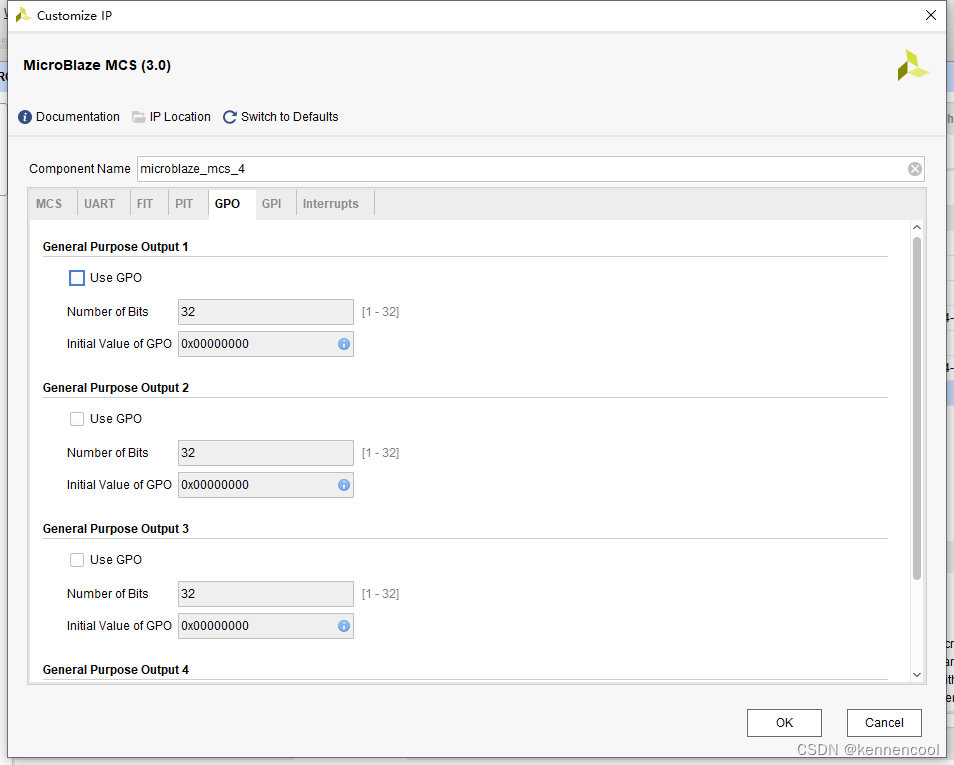

GPO

GPO 一般用于控制外部设备的状态或触发某些特定的操作。如果应用场景只需要简单的输出控制,GPO 输出更为简单直接。如果需要更多的灵活性和复杂的输出控制,GPIO 输出会更加适合。在 SDK 中,可以设置相应的 GPO 寄存器来控制 GPO 的状态,从而控制连接到 GPO 引脚的外部设备。

这里不做配置。

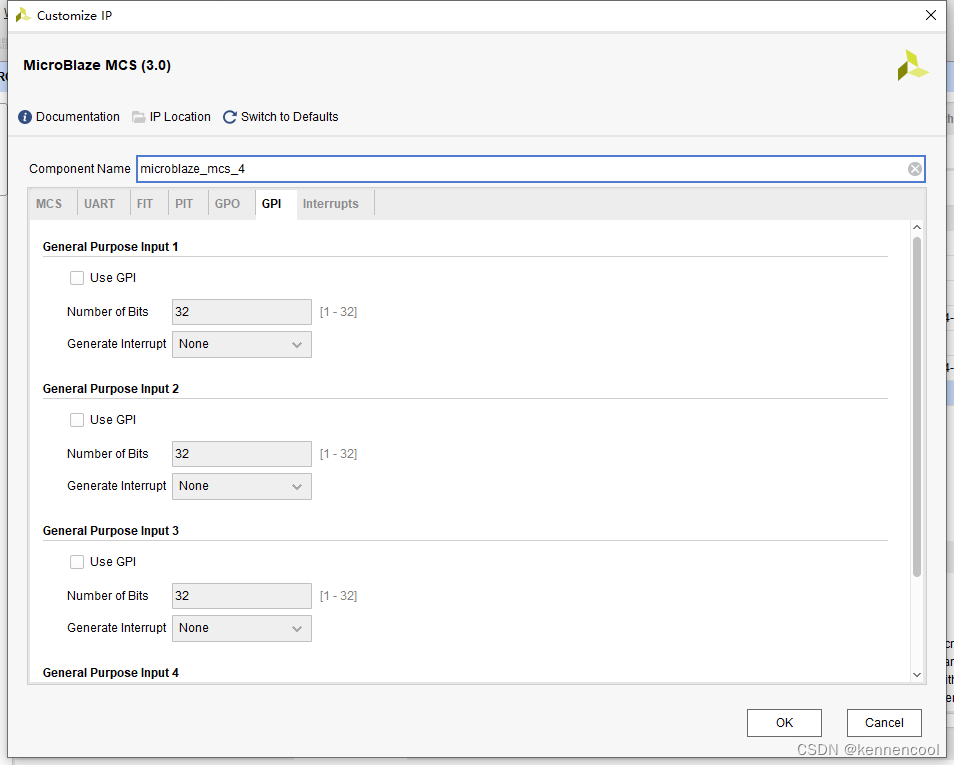

GPI

和 GPO 对应,不做详细解释。

这里不做配置。

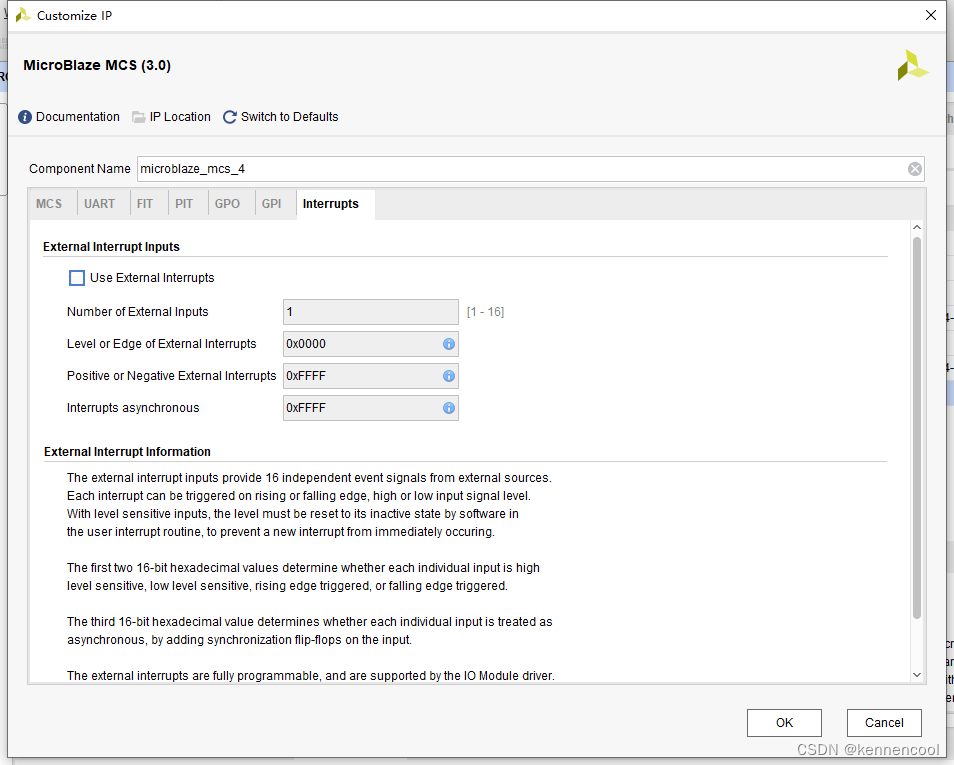

Interrupts

允许外部设备通过特定的信号通知处理器发生了某些重要的事件,处理器在接收到中断信号后,会立即暂停当前正在执行的任务,并跳转到预先定义好的中断处理程序,以处理中断事件。

这里不做配置。

1.3 在 Verilog 源码中实例化 IP

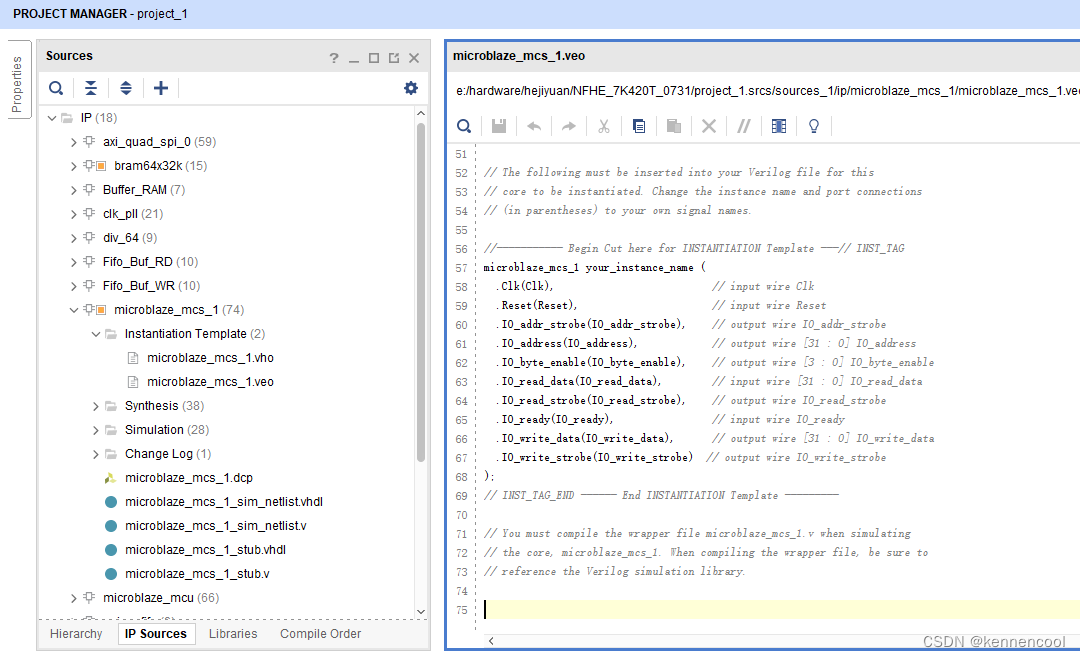

Vivado 2018.2 中,点击 Sources 下方 IP Sources -> 展开 microblaze_mcs IP,在 Instantiation Template 下的 .veo 文件中,可以找到模块实例化模板

将模板代码粘贴到使用到该 IP 核的 Verilog 源码文件中进行修改,到此完成了实例化。

2 在 Xilinx SDK 中进行 MicroBlaze MCS 嵌入式软件的开发与调试

这一部分在我的另一篇播客中有完整流程:Xilinx SDK 基于 MicroBlaze MCS IP 核的嵌入式开发与调试_qq_43581650的博客-CSDN博客

总结

本文仅仅介绍了 MicroBlaze MCS IP 核的使用,并不设计到具体的代码开发过程,今后有代码示例了也会分享出来。

参考资料:

Xilinx 官网:pg116-microblaze-mcs;

1268

1268

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?