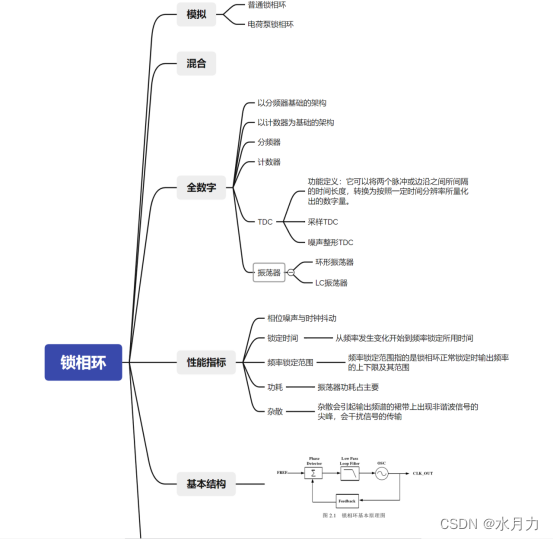

锁相环基本介绍

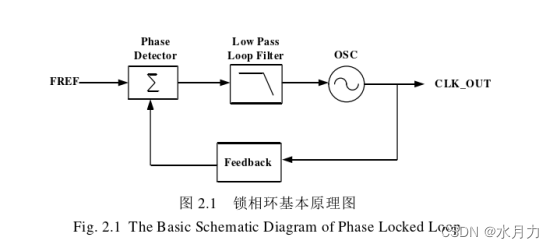

1、锁相环基本原理

锁相环是一个典型的负反馈系统。振荡器 负责产生振荡时钟信号,振荡器的输出时钟信号被反馈环路采样后与输入参考时钟信号 经由相位检测器进行比较,生成相位误差信号,经过滤波器滤波后,反馈给振荡器对输 出时钟信号的频率进行调节。低通滤波器主要是对相位误差信号的高频噪声分量进行滤 波,除去杂散信号。相位检测器对输出时钟信号与输入参考时钟信号的频率和相位进行 比较生成相位误差信号。

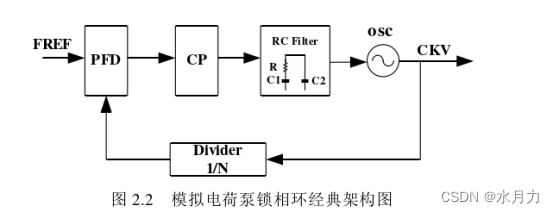

2、模拟电荷泵锁相环

基本结构:鉴频鉴相器, 电荷泵,无源滤波器,压控振荡器,分频器等模块

文章介绍了锁相环的基本原理,包括模拟电荷泵锁相环和全数字锁相环的结构与性能对比。近年来,全数字锁相环成为主流,因其高集成度、低抖动和调谐范围的优势。文中列举了多个近年来的研究成果,展示了在不同工艺节点上的低功耗、高分辨率设计,以及针对相位噪声和调谐范围的优化策略。

文章介绍了锁相环的基本原理,包括模拟电荷泵锁相环和全数字锁相环的结构与性能对比。近年来,全数字锁相环成为主流,因其高集成度、低抖动和调谐范围的优势。文中列举了多个近年来的研究成果,展示了在不同工艺节点上的低功耗、高分辨率设计,以及针对相位噪声和调谐范围的优化策略。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3679

3679

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?