记录集成电路版图提取的步骤(不涉及公司文档)

研究生给导师打工,做芯片的逆向工程,公司一般都会有完成的工作教程,自己记录一下。

所使用的软件工具:

1.chipanalyzer(芯愿景公司提供的,用来查看芯片的相片、提取模拟器件、连线)

2. HxDesigner(中间软件,操作与virtuoso类似。导入chipanalyzer的edf文件后,可以得到完整的器件,连线关系。用于进行SVS错误检查和电路整理。)

3.Cadence IC51/61(在HXdesigner软件中整理好电路图后,可以到处到仿真器中进行真正的工艺库文件替换和仿真了!)

芯片的逆向工程大致分为器件的提取、连线、整理和仿真三个步骤。提取和连线在chipanalyze软件上进行,整理是导入到HxDEsigner软件中进行,仿真就是最后可以在virtuoso软件中仿真验证了。

一、提图连线

用chipanalyze中打开芯片工程,你就能看到一个芯片的全部版图概貌。这里需要一点小小的集成电路版图知识。一般芯片分为有源层,poly层和金属层。是堆叠的三层。就像三层楼房,打的孔就是电梯,电流可以通过电梯相互连接。(有的芯片可能会用到第四层,第五层,金属线用了两三层)、

器件提取

通过每一层的颜色和形状,就可以判断NMOS、PMOS、电阻、三极管、、、

(不同的工艺,比如双极型工艺或者cmos工艺,器件的判断有所不同,需要经验的积累)

器件提取所使用的操作:框选器件——量取尺寸——画path线——ctrl+A打包——ctrl+enter重新命名(根据规则命名)

连线

每次启动前,最先的操作是 N+F3,勾选连续连线和自动打孔

按N画线,根据器件pin的位置,引出pin角,连接所有的金属线。器件必须从第一层先引出一段,再连金属线。(不同层的线颜色不同,不同层之间的连线必须看到有连接孔,否侧不算连接到一起。有时候不会自动打孔,按insert键调出打孔器件,移动光圈到打孔的位置,按O打孔,再按insert取消打孔光标.)

连完线之后进行物理检查和逻辑错误检查。(软件会自动检查出悬空引线、悬空引脚等等)

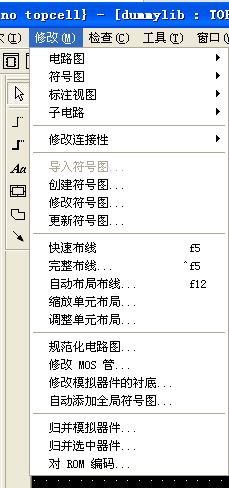

二、电路整理

连完线之后,需要先做SVS检查。(前提是分为两组进行连线)导出电路数据到HXDESIGNER软件后,可以对两组不同连线svs,会检查出两组不同的连线,打印出错误的PDF,两组检查错误。

检查完之后,就可以进行电路整理了~

电路整理前,先对器件进行缩放处理

通常1.5倍-2倍即可,否则器件会重叠在一起。

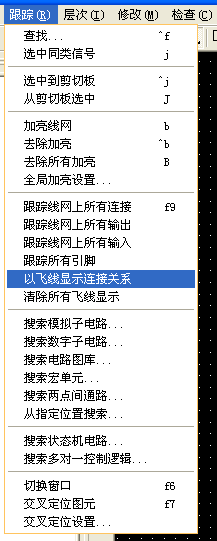

然后以飞线显示连接关系

最好对地线和电源线进行全局加量,增加效率。

==========================

3月2日 更新

难度最大的还是电路整理。

根据datesheet系统框图,对应的引脚,大致分出子电路模块。

将一片电路整理为子电路,层次化处理。

各自对自己子电路的理解来整理,按照上电下地,左进右出的原则进行整理。保证容易看懂电路。

(注:打开跟踪中的以飞线方式跟踪线网;B、shift+B高亮取消线网;注意更换S/D的引脚;归并模拟器件等等)

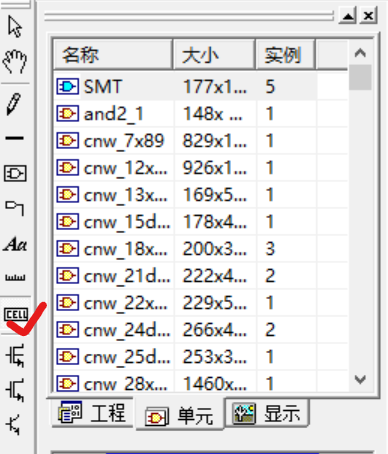

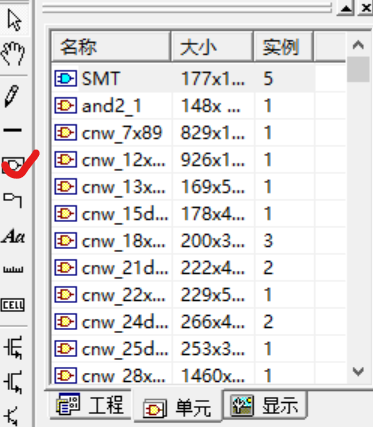

5/24 数字模块的提取:

数字模块的提取也很简单,因为数字模块都是由简单的逻辑门组成。较为简单是反相器,两输入与非门,两输入或非门...RS触发器是两个两输入与非组成。并且在数字模块中存在大量重复的模块,不需要一个一个去提取,可以用枚举的方法来一步完成。

1.做分区

做分区是为了,把你看出来的是数字部分的框出来,方便软件在你框出来的数字区域进行枚举,否则就是在整个版图寻找了!

2. 增加模板

然后右键,编辑单元模板,按照电源、地、输入、输出增加pin;

3. 枚举单元实例

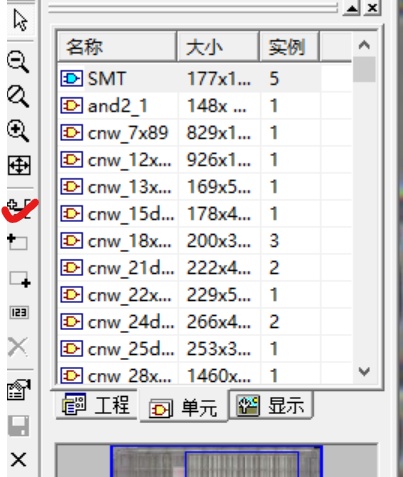

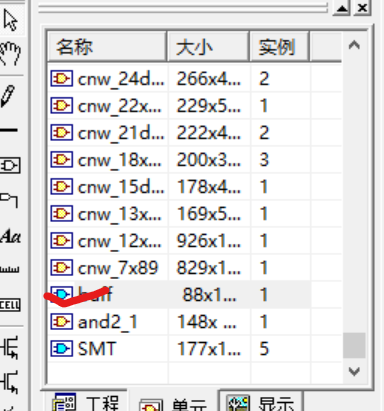

添加好pin后,退出编辑单元模板,在左侧的单元中找到需要枚举的单元,右键自动搜索单元,他会在你框出来的分区中,根据图形找到相近的模块。

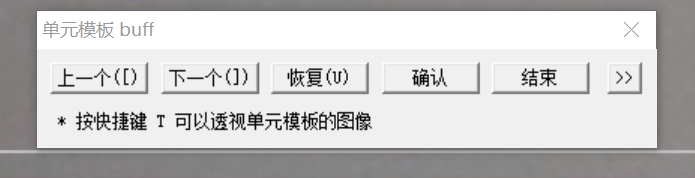

搜索完成会出现蓝色的标志,这时候在右键 《开始确认实例》,就可以一个一个确认相似的实例是否确实相同。

确认表示为相同实例,并且会自动做好一个单元实例在版图上,下一个表示跳过这个检查下一个相似实例。所有的都检查完成就可以结束了。

文章介绍了芯片逆向工程的过程,包括使用ChipAnalyzer进行器件提取和连线,通过HxDesigner进行SVS错误检查和电路整理,以及在CadenceIC中进行仿真。关键步骤涉及识别芯片层、提取器件、连线、检查和整理电路,特别是电路的模块化处理和数字模块的枚举方法。

文章介绍了芯片逆向工程的过程,包括使用ChipAnalyzer进行器件提取和连线,通过HxDesigner进行SVS错误检查和电路整理,以及在CadenceIC中进行仿真。关键步骤涉及识别芯片层、提取器件、连线、检查和整理电路,特别是电路的模块化处理和数字模块的枚举方法。

1709

1709

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?