FPGA约束文件–UCF文件

前言

FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。这三类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF文件,最后再经过实现后生成PCF 文件。

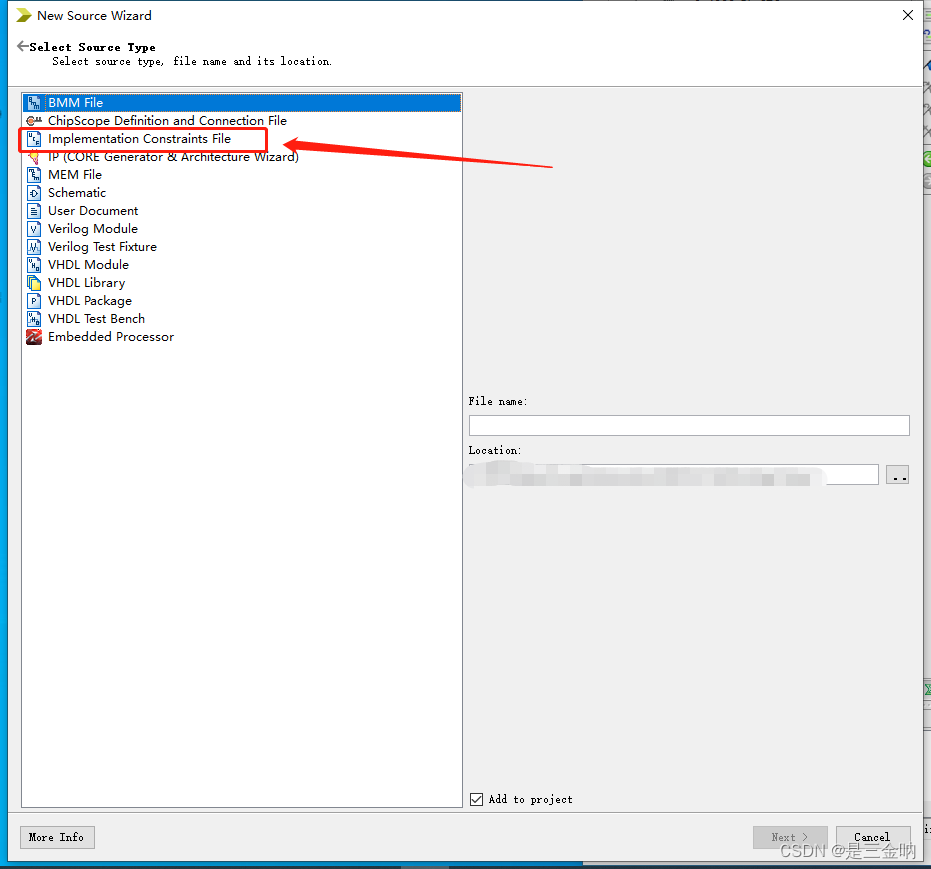

一、创建UCF文件

ISE中PlanAhead 可以用来分配引脚,分配好后点击保存会自动生成一个 UCF 文件,但那样操作麻烦,所以直接创建一个用户约束文件,即UCF 文件,在文件中手动输入时序约束语句和引脚分配语句。

- 第一步

- 第二步

选好名字和文件路径点击NEXT就行了。

二、编写UCF文件。

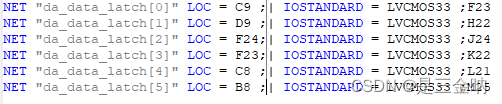

常见的我们需要用到以下约束语句和引脚分配语句:

-

NET:端口关键字,用来引出端口,需要和程序中的一样,例如clk,rst_n;需要注意的是,像input [3:0] A 要写成A[3]、A[2]、A[1]、A[0]。

-

LOC:引脚关键字,后面接等于号用来把端口分配到具体引脚。

-

IOSTANDARD:电压标准关键字,后面接等于号用来约束引脚的电压如 IOSTANDARD = “LVCMOS33”。表达的是 IO BNAK 电压为 3.3V,所以设置为“3.3-V LVTTL”。

-

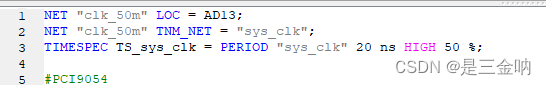

TNM_NET(timing name for nets):网络约束,把时钟(sys_clk)选出来赋予命名如 TNM_NET =sys_clk_pin,并对整个网络所在路径的所有有效同步元件进行约束,可以穿过 IBUFG。

-

TIMESPEC、PERIOD:周期约束,用来约束时钟周期如 TIMESPEC TS_sys_clk_pin = PERIOD

sys_clk_pin 50000 kHz。

更多语句可以专门去看一下,像是通配符啊,优先级啊,等等还有很多,在此就不多废话了,然后点击保存后就可以进行编译了

4988

4988

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?