我们在对程序进行仿真,确认仿真无误后,就需要上板子进行验证

下面我以花式流水灯程序为例FPGA状态机实现花式流水灯_居安士的博客-CSDN博客

介绍FPGA如何上板,以及抓信号的几种方法

目录

FPGA上板

写约束文件

首先创建约束文件

点击add source,选择add or create constraints

点击crate file,给约束文件命名

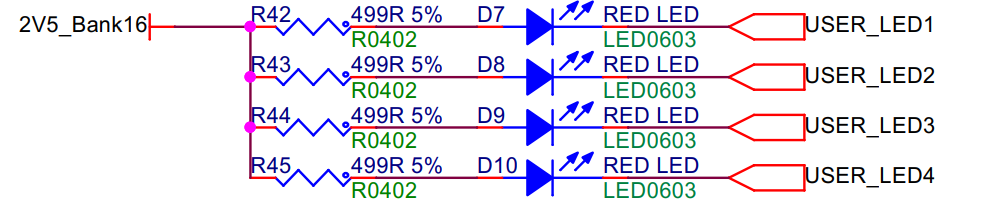

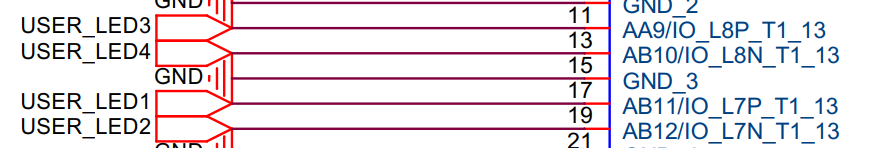

constraints里面会出现约束文件.xdc文件,接下来根据FPGA原理图在约束文件里面把管脚和电平标明。

可见LED1对应AB11,LED2对应AB12,LED3对应AA9,LED4对应AB10

set_property PACKAGE_PIN Y18 [get_ports clk_50m]

set_property IOSTANDARD LVCMOS33 [get_ports clk_50m]

set_property PACKAGE_PIN AB11 [get_ports {led_out[0]}]

set_property PACKAGE_PIN AB12 [get_ports {led_out[1]}]

set_property PACKAGE_PIN AA9 [get_ports {led_out[2]}]

set_property PACKAGE_PIN AB10 [get_ports {led_out[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_out[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_out[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_out[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_out[3]}]前两行是时钟约束,信号名称需要和代码对应起来

后面是管脚约束,将led信号放在芯片的引脚:set_property PACKAGE_PIN xxx [get_ports xxx]

将led所在引脚的电气标准设置为LVCMOS33:set_property IOSTANDARD LVCMOS33 [get_ports xxx]

保存约束文件,之后生成比特流文件

生成比特流文件的步骤:

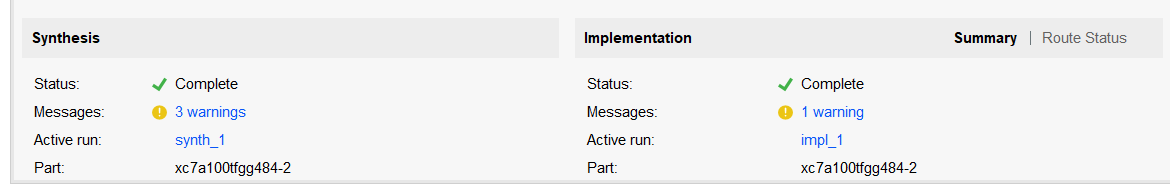

1 点击 Run Synthesis 进行综合

2点击Run Implementation 。如果工程尚没有进行综合(Synthesis)则会先进行综合,之后再进行实现(Implementation)。

3 点击Generate Bitstream。则会同时检查是否已经进行了综合和实现,如果没有则依次进行综合、实现最后再生成二进制文件。

若不出现严重警告和错误,则生成比特流文件

出现下面界面:

接着将板子进行连接

上板步骤:

1.点击open hardware manager——open target——自动连接

2鼠标右键选择program device

3点击运行

随着掉电之后,比特流程序也就随之消失,再次上电,又要重新编译下载程序,如果想把程序保留,需要固化程序

固化步骤:

1.鼠标右键 Generate Bitstream点击Bitstream setting

2.勾选bin文件——ok

3 鼠标右键选择add configuration memory device

4.选128 Mb;选spi;选x1_x2_x4;下面芯片选倒数第二个——ok

5.选择bin文件:.tuns——impl——bin

6.固化成功显示:

7.再次运行,将bit文件改成bin文件

ps:若要擦除,就再下载一次,只勾选Erase

在这里LED灯的亮灭是清晰可见的,我们可以判断程序运行成功,但是有些程序是否成功运行是无法通过板子反映出来的,这个时候就需要抓信号

FPGA抓信号

抓信号有几种方法,在这里分别进行列举,大家可以根据自己的喜好选择

1综合图像法

点击run synthesis——运行完成后点击schematic

在图像上选中信号线,鼠标右击Mark debug

再进行综合,选择save

再进行综合,连线图上面出现小虫:

若想去掉:鼠标右键unmark debug

接下来设置debug:鼠标右键setup debug

修改抓的时间(数据深度1024等)——finish

重新生成比特流文件并运行

2.添加代码法

在需要检测的信号前面加(*mark_debug=”ture”*)

(*mark_debug=”ture”*)wire time1_en;

(*mark_debug=”ture”*)wire time2_en;重新生成比特流文件并运行

3.调用IP核法

搜索ILA,选择ILA(integrated logic analyzer)

选择检测多少路和数据深度

设置信号的位宽(根据自己的程序)

把ILA例化进有待检测信号的程序里面

把ILA例化进有待检测信号的程序里面

ila_0 your_instance_name (

.clk(clk_25m), // input wire clk

.probe0(time1_en), // input wire [0:0] probe0

.probe1(time2_en), // input wire [0:0] probe1

.probe2(led_out) // input wire [3:0] probe2

);重新生成比特流文件并运行

抓信号操作

这个时候会自动出现.ltx文件

点击program,会自动弹出下面的debug页面

对需要抓取的信号进行触发条件设置,之后运行

单个信号抓取,红线会在信号满足触发条件的地方

多个抓取,红线会在同时满足触发条件的地方

抓取的信号位宽不为1时,可以修改需要抓取的数值

综上, 我以花式流水灯为例,介绍了FPGA上板的方法:包括写约束文件,生成比特流文件,以及固化操作;此外还介绍了3种抓信号方法

1636

1636

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?