VIVADO控制BIT文件配置速度与压缩

前言

FPGA加载程序有时候会需要用外置FLASH,有些FLASH的传输速率可能没有那么高,容量小,导致上电后程序不能正常加载到FPGA或者不能烧录到FLASH芯片,所以需要我们在生成BIT文件进行降速处理和压缩处理,这里有两种方式介绍如何改变我们BIT文件的配置操作

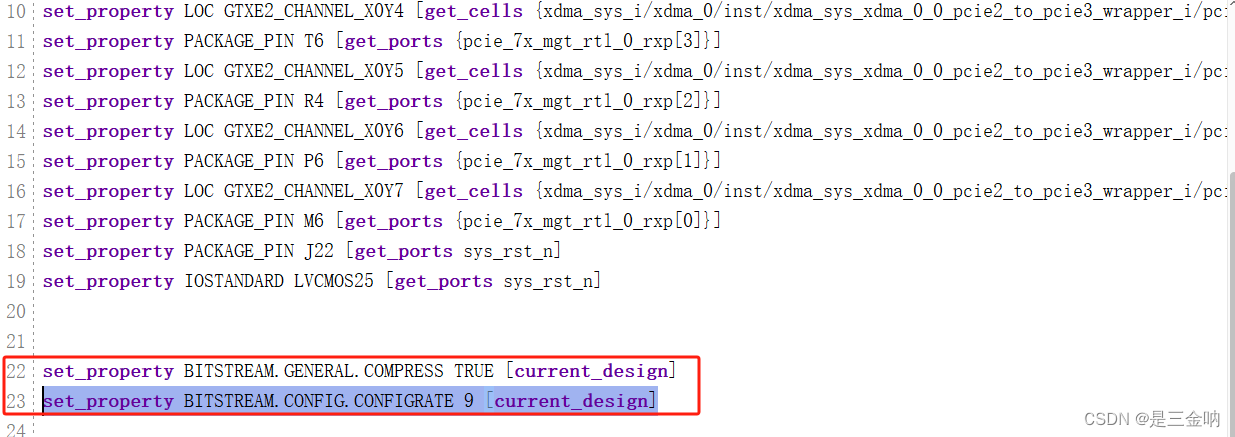

一、采用XDC约束文件

这个是最简单暴力的操作,只需要打开XDC文件

输入set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design],对文件进行压缩;

输入set_property BITSTREAM.CONFIG.CONFIGRATE N [current_design],设置文件配置速度,其中N的单位为MHz,例如要配置9MHz的配置速度,约束只需要加上“set_property BITSTREAM.CONFIG.CONFIGRATE 9 [current_design]”即可

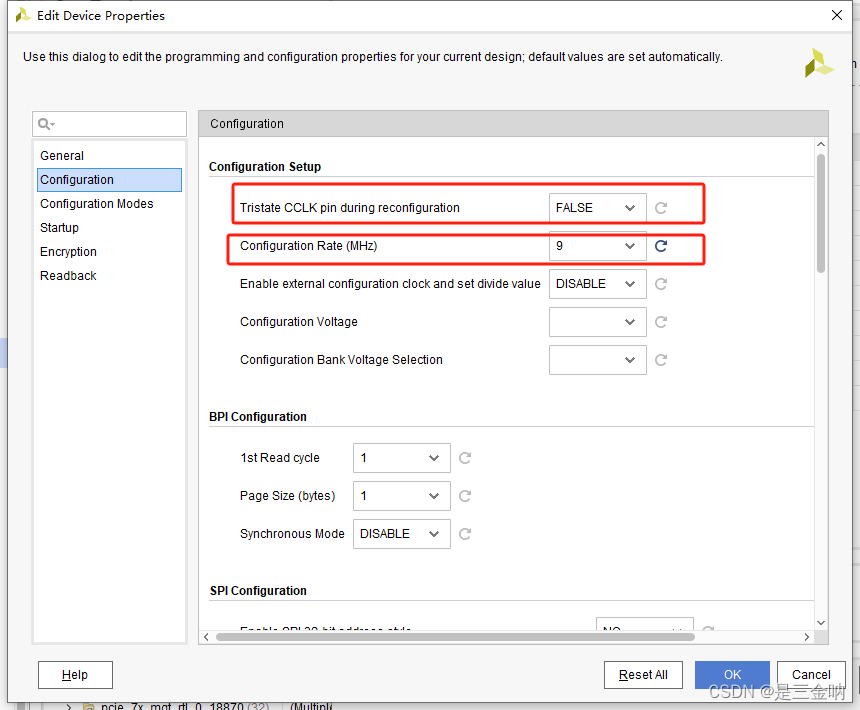

二、配置页面配置

打开RTL ANALYSIS–>Open Elaborated Design,在该页面下打开PROJECT MANAGER–>Settings–>Configuration下,其中Configuration Rate选择合适的配置速率,Tristate CCLK pin during reconfiguration选择是否压缩

三、题外–如何去提高综合速度

方法一:

在Vivado tcl console中输入:

set param general.maxThreads n

n为CPU线程数,默认为8。

检查是否成功设置可在Vivado tcl console中输入:

get_param general.maxThreads

方法二:

使用Linux系统中的Vivado。linux系统下的Vivado综合速度更快。

6751

6751

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?