1.c创建FIFO的IP核

在IP catalog里面搜索FIFO并双击,保存为my_fifo

然后一直点击next

读和写的full和empty都要√上,不然后面定义要出错

勾选inst文件

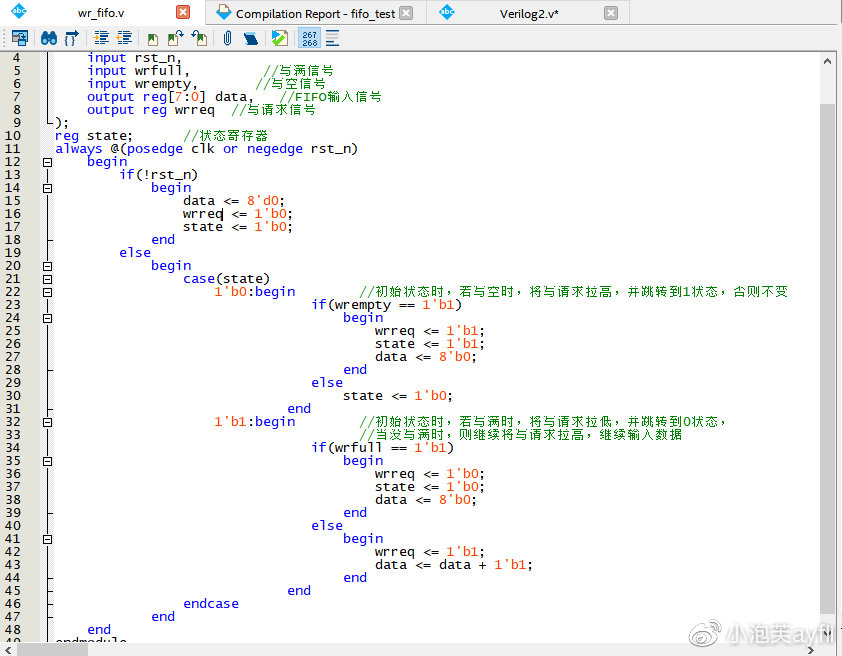

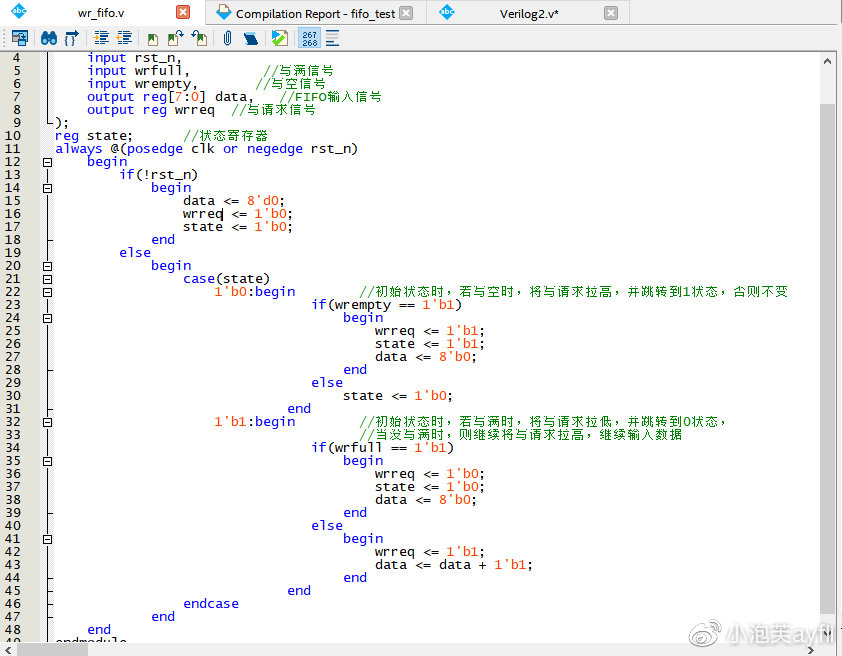

2.对FIFO进行写入操作

3.对FIFO进行读出操作

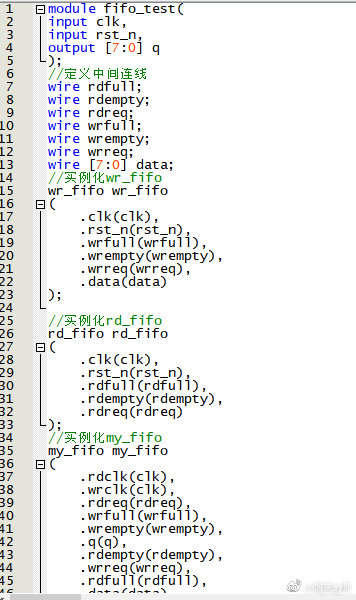

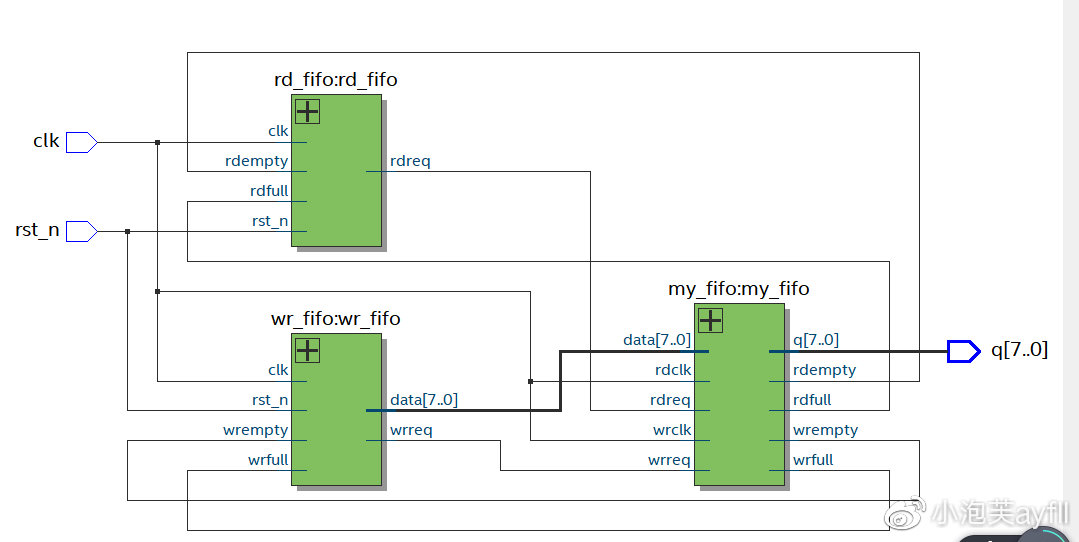

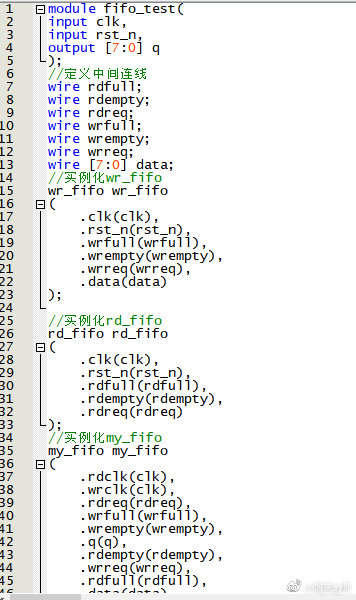

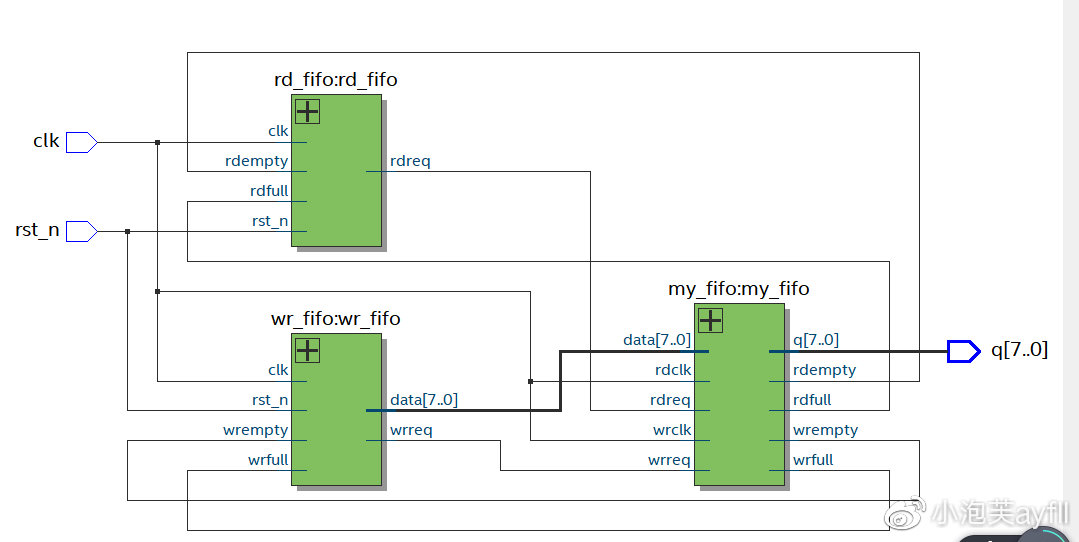

4.顶层文件的编写及rtl结构图

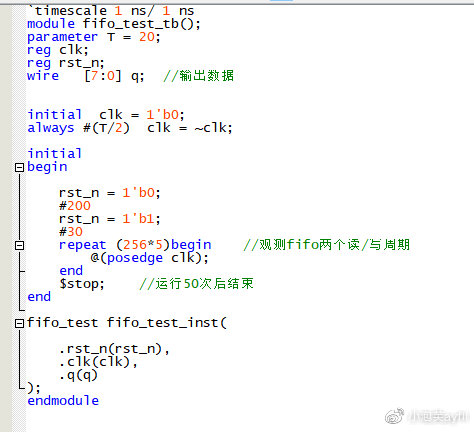

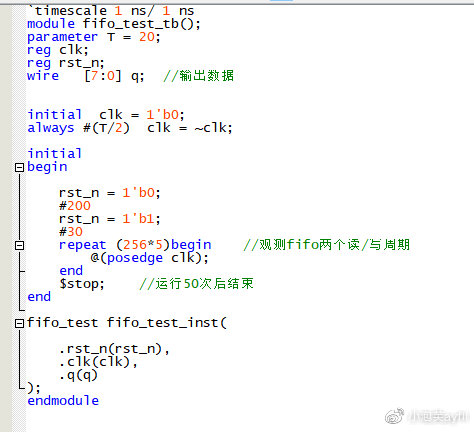

5.测试文件的编写

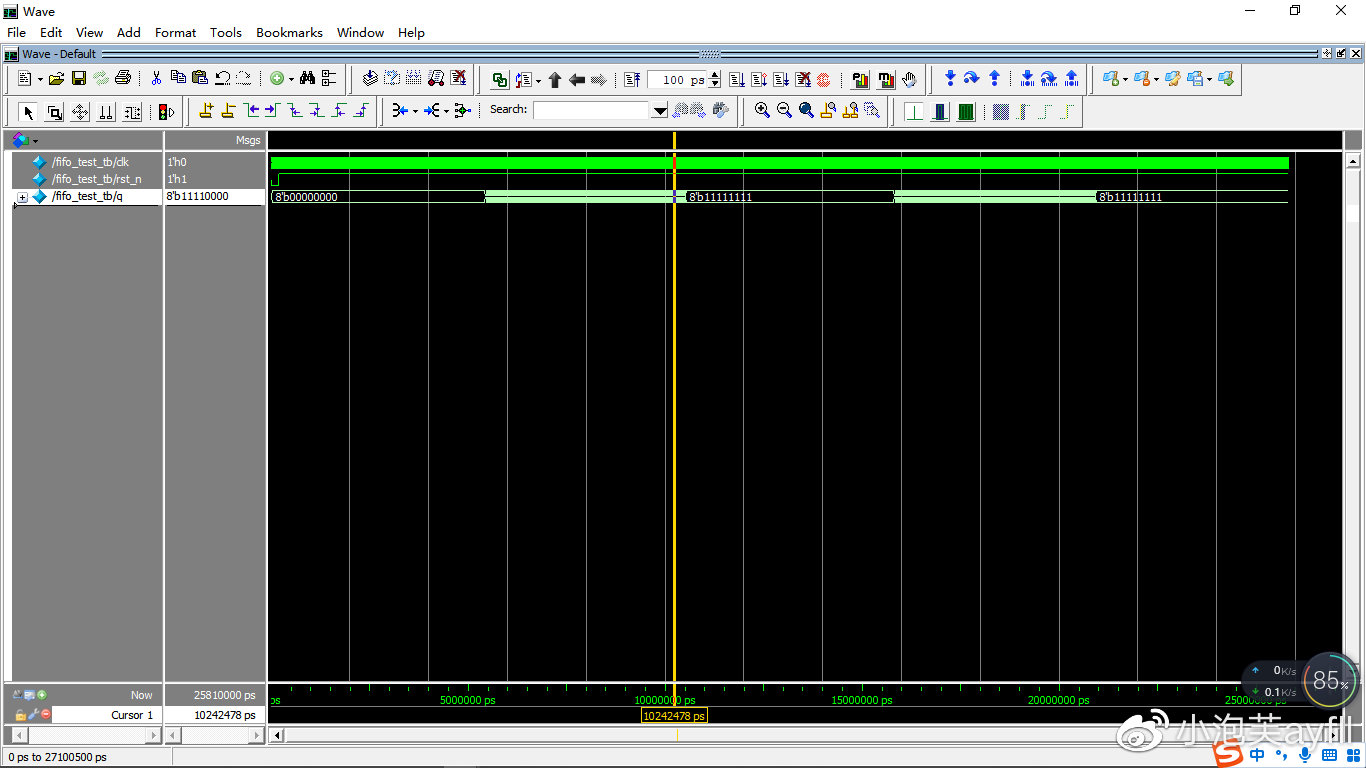

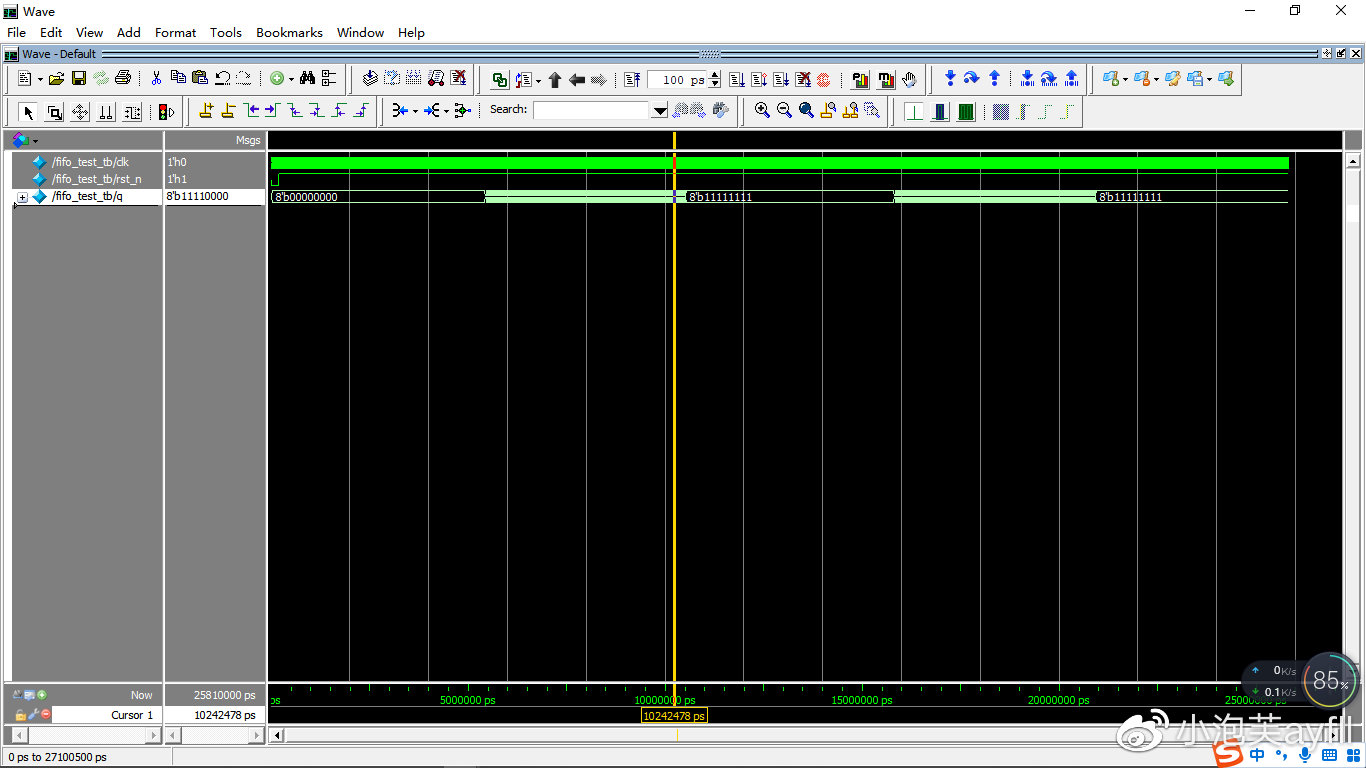

6.仿真结果

工程文件上传至qq群:868412045

1.c创建FIFO的IP核

在IP catalog里面搜索FIFO并双击,保存为my_fifo

然后一直点击next

读和写的full和empty都要√上,不然后面定义要出错

勾选inst文件

2.对FIFO进行写入操作

3.对FIFO进行读出操作

4.顶层文件的编写及rtl结构图

5.测试文件的编写

6.仿真结果

工程文件上传至qq群:868412045

2777

2777

2718

2718

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?