一、FPGA的自我介绍

FPGA(Field-Programmable Gate Array),全称叫现场可编程门阵列。能够通过编程来配置其硬件结构,实现特定功能的数字电路。

FPGA拥有强大的可编程性,其主要由大量的可编程逻辑单元以及丰富的I/O资源组成,能够通过硬件描述语言(VHDL/Verilog)定义其电路功能,通过用户编程配置后实现不同的硬件逻辑。

FPGA属于是硬件结构电路,拥有一定的并行处理能力。在一些高频高速信号处理、实时控制等场景下,性能远超CPU/GPU的串行架构。并行处理能力,直接通过硬件来实现,使其链路延时非常小,响应速度能够达到纳秒级别。

部分FPGA支持运行时动态重配置,可进行不同功能模块的切换,实现更为灵活的应用。

二、FPGA的基本结构

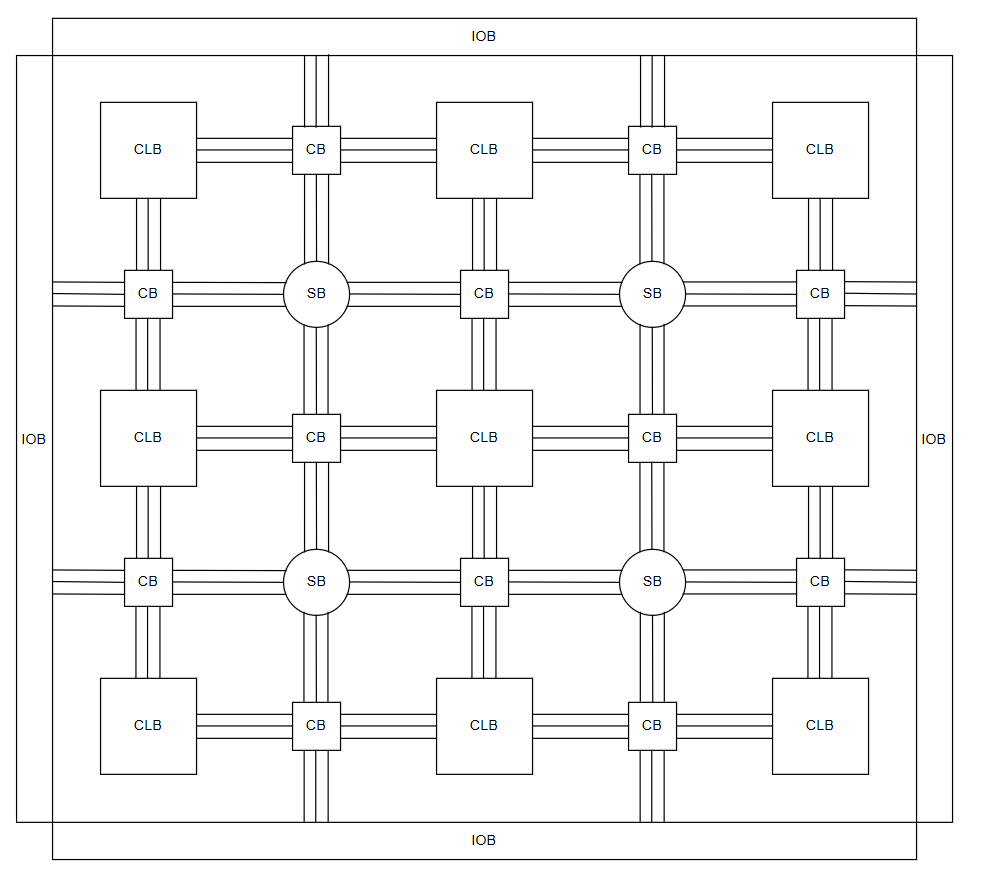

FPGA的基本原理结构图如下图所示:

FPGA中的基本逻辑单元为CLB模块。每一个CLB模块中一般都会包含若干个查找表(LUT,Look-Up Table)、触发器(FF,Flip-Flop)以及多路选择器(MUX)。一个FPGA芯片中包含着成千上万个基本逻辑单元模块,在这些基本逻辑单元组成的结构中间穿插着丰富的连线资源,使得基本逻辑单元之间能够通信。在每个基本逻辑单元模块中间,还有CB和SB两个模块。其中CB模块的作用是将基本逻辑单元的输入输出连接到顶层IO模块上,而SB模块的作用是对水平和竖直的连线资源进行切换。所有结构的外层,都是功能强大的IOB模块,能够提供内部模块与外部模块的数据通信。

随着技术的不断发展,FPGA相关的架构也会变得越来越复杂,并且会有越来越多的资源种类出现,但是不论如何变化,最基本的架构还是有IOB、CLB和连线资源组成的。

三、FPGA的开发环境

1.厂商专用的开发工具

(1)Xilinx(AMD)

- Vivado Design Suite:综合、布局布线、仿真、调试、比特流生成;支持VHDL/Verilog,集成IP核库

- Vitis:面向高层次综合(HLS)和AI加速开发

(2)Intel(Altera)

- Quartus Prime:类似Vivado,支持Cyclone/Arria系列FPGA;集成Nios II软核处理器开发环境

- ModelSim Intel Edition:仿真工具(与Quartus无缝集成)

(3)国产FPGA厂商

- 紫光同创:Pango Design Suite(类似Vivado)

- 安路科技:TD(Tang Dynasty)工具链

2.仿真与验证工具

- ModelSim/QuestaSim:行业标准仿真工具,支持功能仿真与时序仿真。

- Verilator:开源仿真器,适合快速验证逻辑设计。

- GTKWave:开源波形查看工具,配合仿真使用。

3.辅助开发工具

HLS(高层次综合)工具:

- Xilinx Vitis HLS:将C/C++代码转换为RTL(如加速图像处理算法)

- Intel HLS Compiler:类似功能,支持OpenCL

四、FPGA的开发流程

1.设计输入

- 硬件描述语言:Verilog/VHDL编写逻辑代码

- IP核集成:调用自带模块(如FIFO、Block ram核)

2.逻辑仿真

- 功能仿真:验证逻辑正确性

- 时序仿真:加入实际延迟,验证时序约束

3.综合(Synthesis)

- 将HDL代码转换为门级网表

- 优化逻辑资源占用

4.布局布线(Place&Route)

- 将逻辑映射到FPGA物理位置,规划信号路径

- 关键指标:时序裕量、布线拥塞程度

5.生成比特流(Bitstream)

- 生成 bit 文件,通过JTAG下载到FPGA

6.验证与迭代

- 在板卡上验证功能,通过ChipScope(Xilinx)或者SignalTap(Intel)抓取实时信号

- 根据测试结果修改迭代程序代码

1084

1084

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?