题目

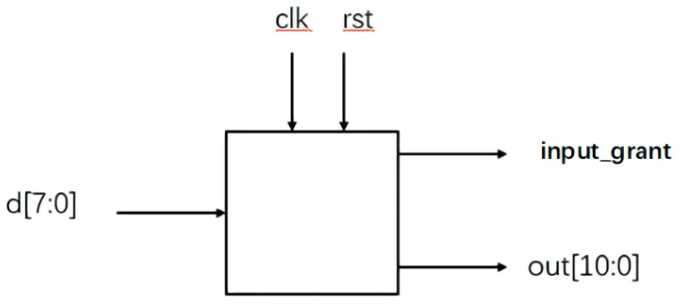

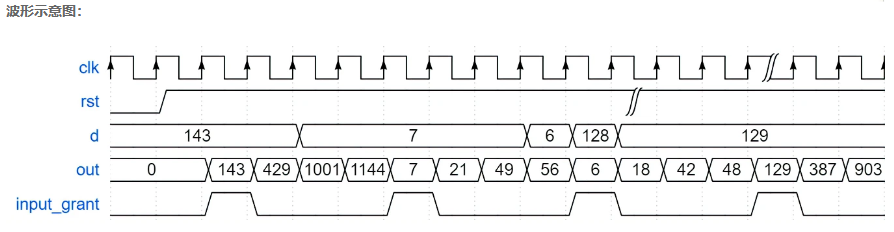

已知d为一个8位宽的数,请在每个时钟周期分别输出该数乘1、3、7、8,并输出一个脉冲信号通知此时刻输入的d有效(d给出的信号的上升沿表示写入有效)。

根据乘法的倍数,可以对乘法运算采用移位运算进行实现,如下表。

| 乘法倍数 | 近似位运算操作 |

|---|---|

| 1 | d |

| 2 | (d<<1) |

| 3 | d + (d<<1) |

| 4 | (d<<2) |

| 5 | d + (d<<2) |

| 6 | (d<<1) + (d<<2) |

| 7 | d + (d<<1) + (d<<2) |

| 8 | (d<<3) |

答案

`timescale 1ns/1ns

module multi_sel

(

input [7:0]d ,

input clk,

input rst,

output reg input_grant,

output reg [10:0]out

);

reg [1:0] cnt;

always @(posedge clk or negedge rst)

if(~rst)

cnt <= 2'b0;

else

cnt <= cnt + 1'b1;

reg [7:0] sr_d;

always @(posedge clk or negedge rst)

if(!rst) begin

out <= 11'd0;

input_grant <= 1'b0;

end

else

case(cnt)

2'b00:

begin

input_grant <= 1'b1; //乘1

out <= d;

sr_d <= d;

end

2'b01:

begin

input_grant <= 1'b0;

out <= sr_d + (sr_d<<1); //乘3

end

2'b10:

begin

input_grant <= 1'b0;

out <= sr_d + (sr_d<<1) + (sr_d<<2); //乘7

end

2'b11:

begin

input_grant <= 1'b0;

out <= (sr_d<<3); //乘8

end

default:

begin

input_grant <= 1'b0;

out <= d;

end

endcase

endmodule

160

160

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?