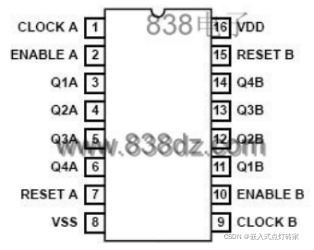

【芯片引脚图】

图CD4520-1 CD4520芯片引脚图

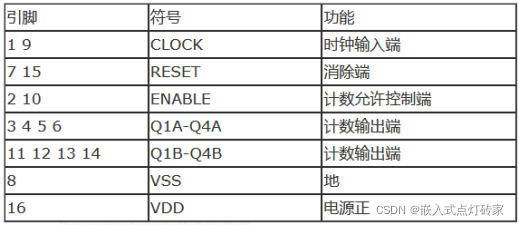

芯片引脚功能图如下:

【芯片功能概述】

表CD4520-2 CD4520芯片真值表

CD4520是二、十进制(8421编码)同步加计数器,内含两个单元的加计数器,其功能表如真值表所示。每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。由表可知,若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK端置“0”;若用CL℃K信号上升沿触发,触发信号由CL℃K端输入,ENABLE端置“1”。RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET端置“0”时,CD4520才开始计数。

CD4520采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次。这样从初始状态(“0”态)开始计数,每输入10个时钟脉冲,计数单元便自动恢复到“0”态。若将第一个加计数器的输出端Q4A作为第二个加计数器的输入端ENB的时钟脉冲信号,便可组成两位8421编码计数器,依次下去可以进行多位串行计数。

CD4520为二进制加计数器,由两个相同的内同步4级计数器构成。计数器级为D型触发器,具有内部可交换CP和EN线,用于在时钟上升沿或下降沿加计数。在单个单元运算中,EN输入保持高电平,且在CP上升沿进位。CR线为高电平时,计数器清零。计数器在脉动模式可级联,通过将Q3连接至下—计数器的EN输入端可实现级联,同时后者的CP输入保持低电平。

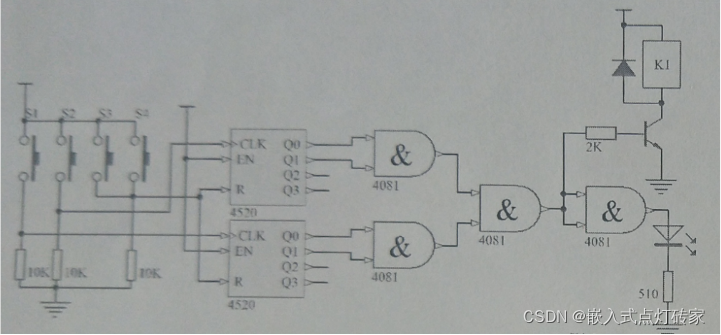

【芯片实例讲解】

实例一:密码锁

图CD4520-3 CD4520之实例一:密码锁

如图所示:先按下S3,再按三次S1,后按三次S2;此时CD4520A和CD4520B的Q0和Q1均为高电平,密码锁开锁,LED灯亮。其中S3和S4均为复位键,S1和S2为脉冲输入引脚。

实例二:计数器,见2012年省赛题目。

【芯片真题考察】

1)2013年省赛中,考察点为实例一。

本文详细介绍了CD4520二、十进制同步加计数器的引脚功能、工作原理及真值表。该芯片具备并行进位特性,可用于密码锁、计数器等应用。通过实例展示了如何利用CD4520构建密码锁系统,并提及在竞赛中涉及的相关考察点。

本文详细介绍了CD4520二、十进制同步加计数器的引脚功能、工作原理及真值表。该芯片具备并行进位特性,可用于密码锁、计数器等应用。通过实例展示了如何利用CD4520构建密码锁系统,并提及在竞赛中涉及的相关考察点。

1694

1694

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?