一、进制

1、二进制简介

- 一种数字表示法,它使用两个不同的数字符号 0 和 1 来表示数值

- 位(bit):不同于十进制中,每个位可以用 0-9 表示,二进制中每位都是 0 或 1,每个二进制位我们称之为一个 bit,可以表示两种状态。位一般用 b 代替,例如 8 b 代表 8 个 bit

- 字节(byte):8 bt 组成一个字节,总共可以表示 256 种状态。字节一般用 B 代替,例如 8 B 一般表示 8 个字节

- 其他计量单位(K,M,…)

(一)K:表示 2 的十次方,1 KB = 1024 B

(二)M:表示 2 的 20 次方。1 MB = 1024 KB = 1048576 B

(三)G:表示 2 的 30 次方,1 G = 1024 MB

(四)T:表示 2 的 40 次方,1 T = 1024 GB

2、进制符号

- 二进制(B)、十进制(D)、八进制(O)、十六进制(H)

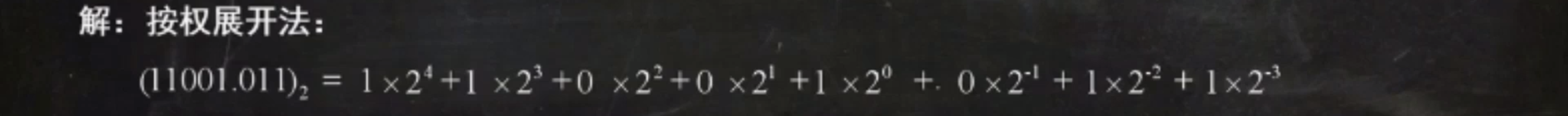

- 二进制转十进制,直接按权展开

- 二进制转十六进制:四位一个,小数点两边数四位为一个数,依次转为十六进制(不足补 0)

- 十六进制转二进制两种方法(比如 12345)

(一)先转十进制,再转二进制:5 * 160+4 * 161+3 * 162+2 * 163+1 * 164,然后再将十进制转二进制,除二取余倒序

(二)直接转,12345(十六进制)转为二进制是 0001 0010 0011 0100 0101

3、二进制算术运算

- 原码、反码、补码

- 计算机存储该数字,是存储该数字对应二进制数字的补码(由于正数补码一样所以平常不在意)

(一)原码:加一个符号位,其 1 表示负数,0 表示正数(如+1000=01000;-1000=11000)

(二)反码:正数反码和原码一样,负数除去符号位都取反(如(-1000)=10111)

(三)补码:正数和原码一样,负数在其反码的基础上加 1(如(-1000)=11000)

正数原码、反码和补码都一样,负数的反码除去符号位都取反,补码在其反码的基础上再加 1 即可 (口诀:正数原反补一样;负数反码除符号位其余取反,补码在反码基础上加 1)

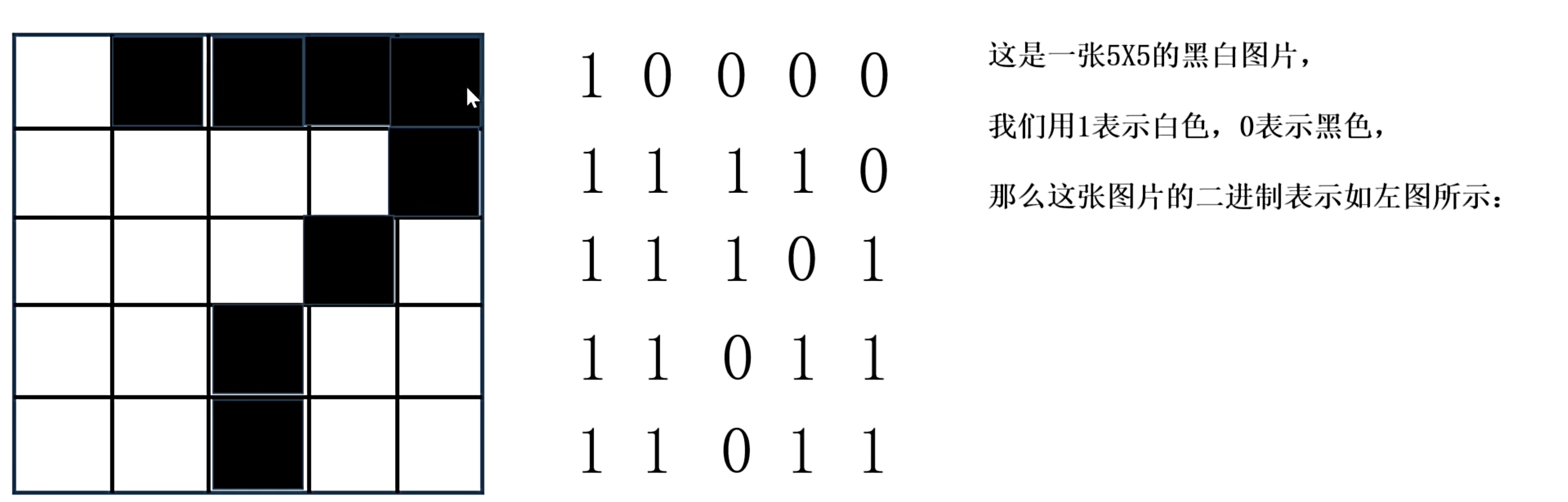

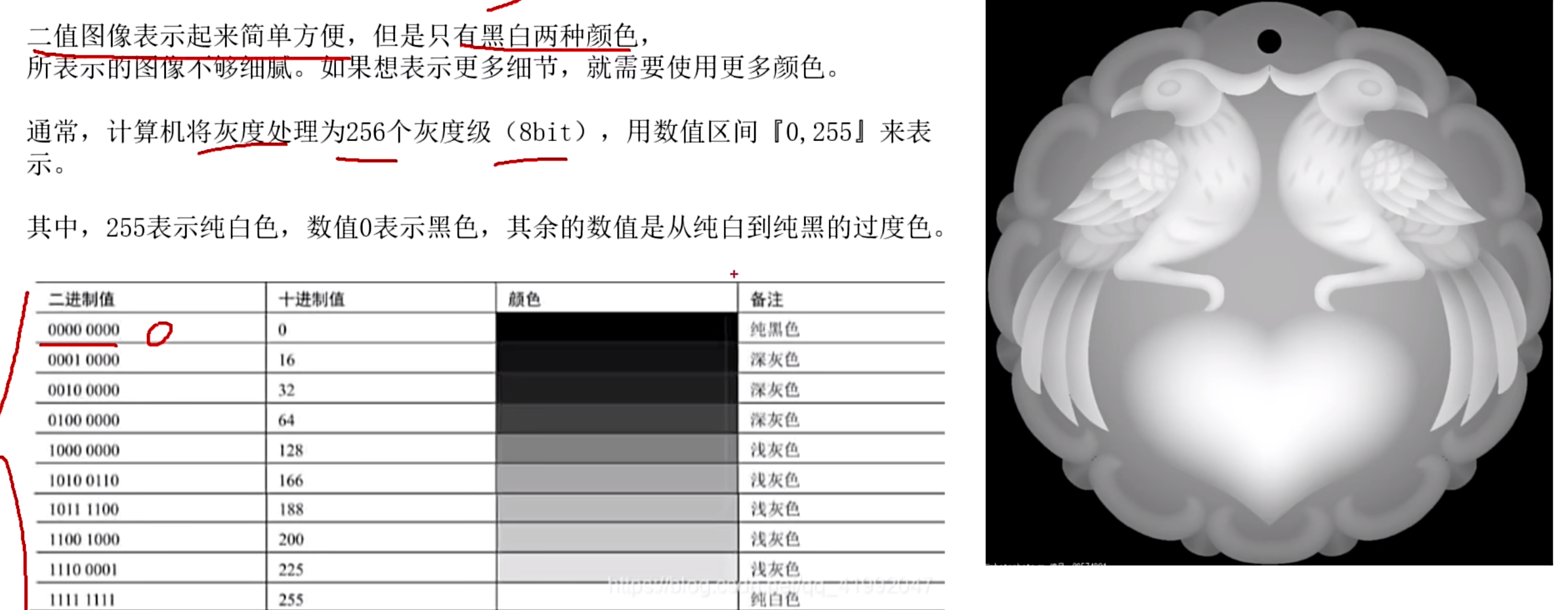

4、二进制表示图片

- 像素的深浅级别我们称为“位深”, 0-255 为 8 位深,0-65535 是 16 位深。位深越大,颜色切分越连续,越不容易出现色阶。现今网络上的图像一般都是 32 位深

- 二值图像

- 灰度图像

- 彩色图像,RGB(红绿蓝)

5、二进制表示声音

- 们将一段时间(例如 1 秒钟)的连续声波分成很多份,并将每一份记录一个平均振幅。拆分的份数,我们称之为采样率。拆分过程中必然会产生信息丢失,而采样率越大,信息丢失越少。目前比较常用的采样率是 44100 HZ 或者 48000 HZ

- 跟图像的颜色深浅类似,也可以用 0-255 或者 0-65535 表示声音振幅的高度。这个数字的取值范围叫做声音的位深。目前通用的位深一般是 16 bit 或者 24 bit #

视频就是连续的图片和声音

6、二进制表示汉字

- GB2312编码:1981年5月1日发布的简体中文汉字编码国家标准。收录7445个图形字符,其中包括6763个汉字BIG5编码:台湾地区繁体中文标准字符集,共收录13053个中文字,1984年实施

- GBK编码:2000年3月17日发布,收录21003个汉字,包含国家标准GB13000-1中的全部中日韩汉字,和BIG5编码中的所有汉字

7、进制转换

- 小转大乘 R 取整;大转小除 R 取余

注意二进制的别称,方便记忆:8421 码

二、电路

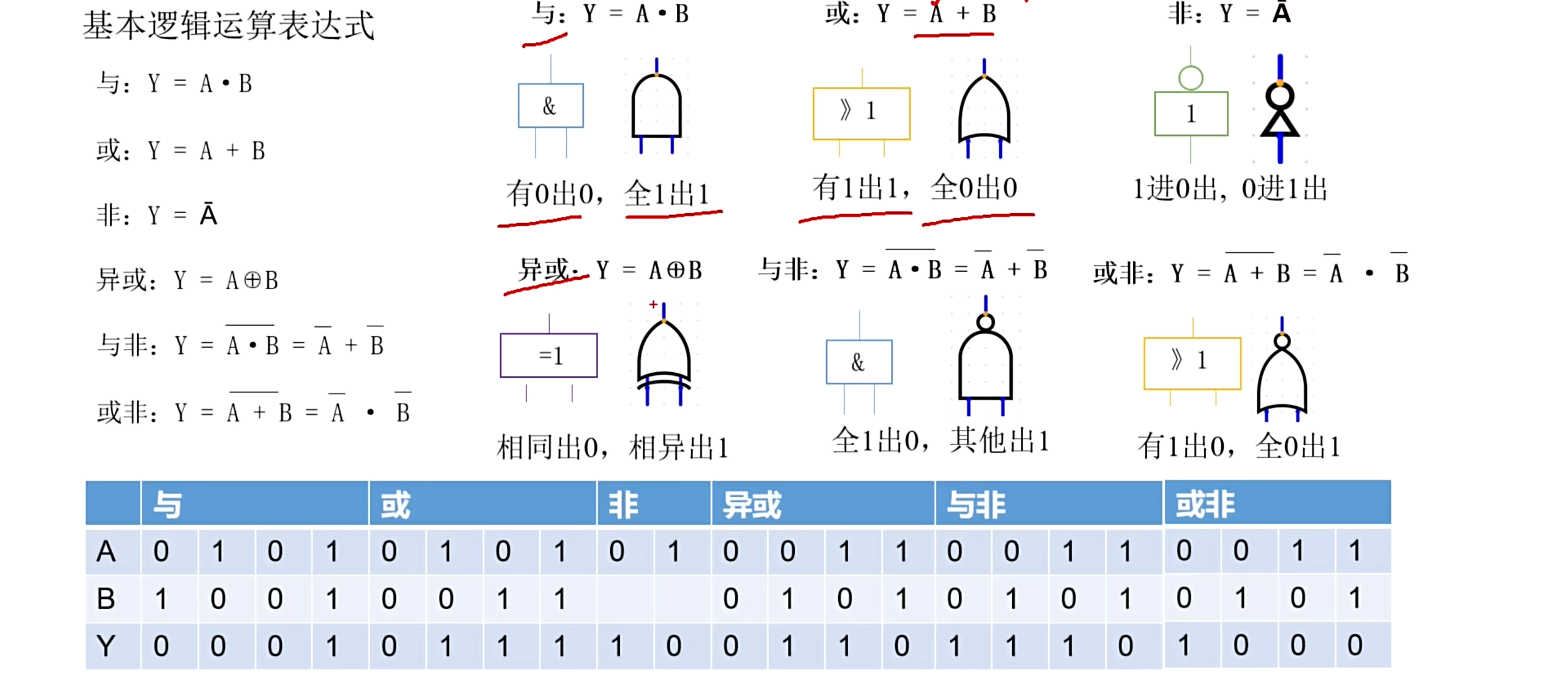

1、与门

- 只要有一个为 0 结果为 0;可以根据运算来画电路,注意理解:Y=AB,A 或 B 只要有一位为 0,则 Y=0,当且仅当 A=B=1 时,Y=1

2、或门

- 只要有一个为 1,结果就为 1,两个为 0 结果才为 0;Y=A+B,只有当 A=B=0 时 Y 才为 0,否则都为 1

3、非门

- 输入为 1,结果为 0,输入为 0,结果为 1;Y=A’其中,A 为 1 时 Y 为 0,A 为 0 时 Y 为 1,恰好相反

4、门电路画法

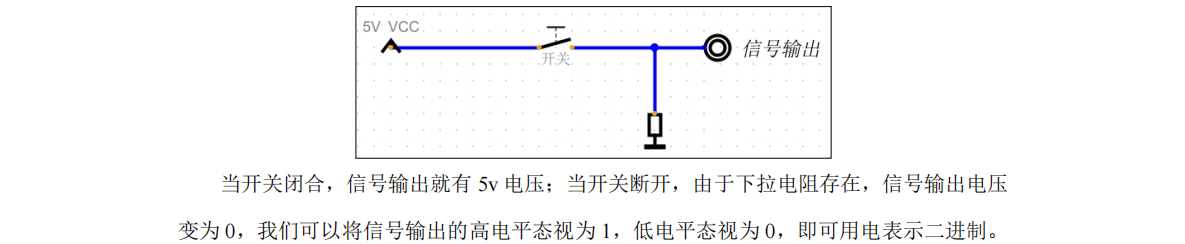

- 高电平是指电路的最高电压,通常为 1(例如 10 V 的电路的高电平应该是 10 V 或接近 10 V)

- 低电平是指电路的最低电压,通常为 0(例如 0 V 的电路的低电平应该是 0V 或接近 0 V )

- 断路被称为高阻态(电路中符号为 Z)

低电平表示0高电平表示1

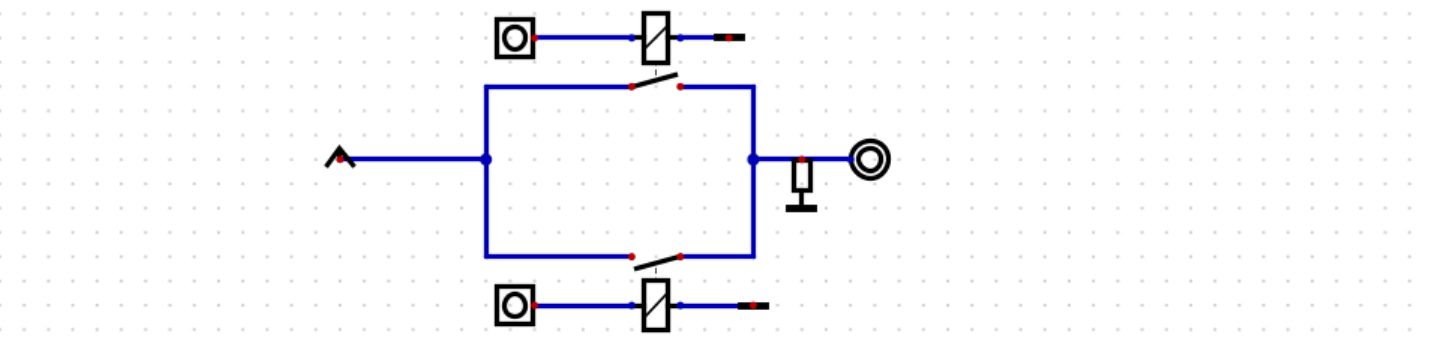

- 以或门为例;有输入输出,电源,继电器(开关);开关左边连接输入,右边接地;输出前接个电阻 > 继电器在广义上可以被认为是开关的一种,根据电路变化自动开关;注意继电器一般左接输出右接地,左电源右输出

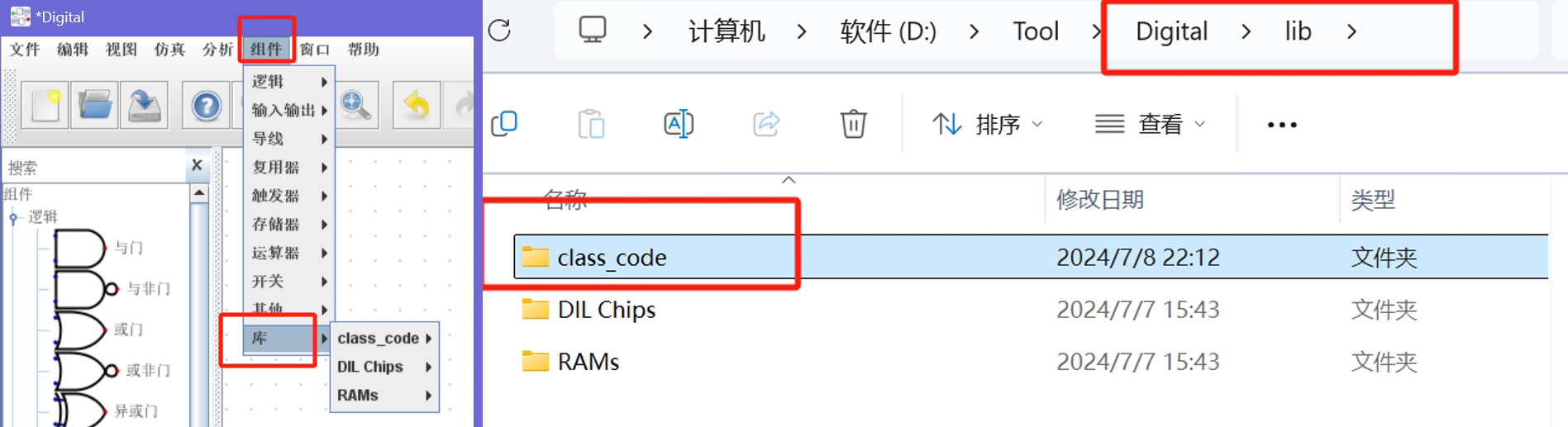

5、Digital 软件

- 使用 Digital 软件注意

(一)库文件保存路径

- 注意颜色

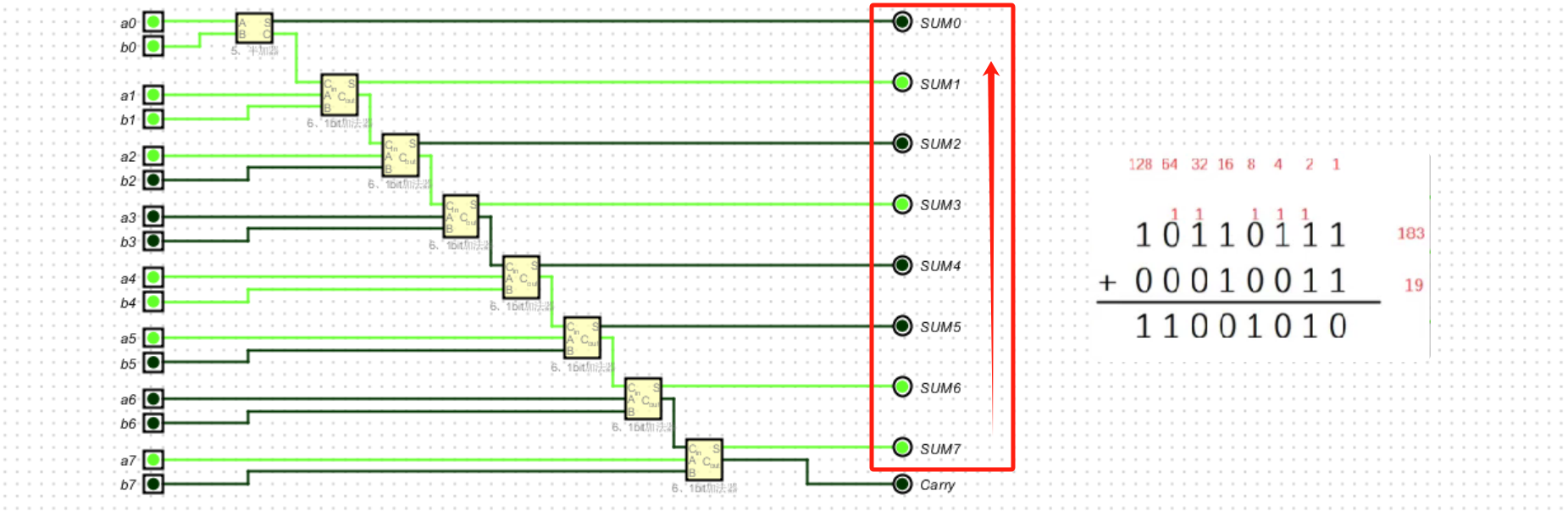

(一)计算的时候是从右往左输入,如 10110111,输入是 11101101(倒序输入,倒序输出)

(二)红绿色盲模式下,黄色为 1,红色为 0

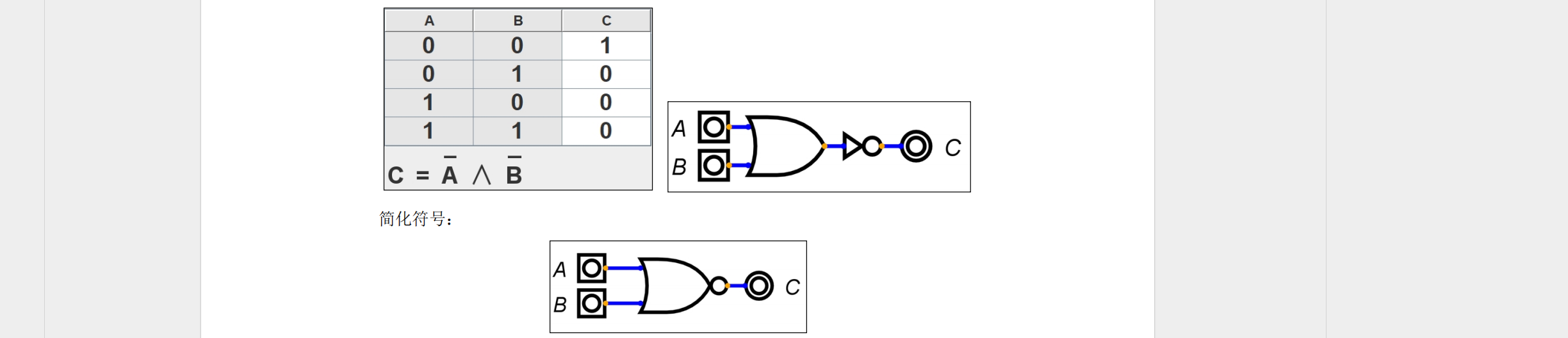

6、逻辑门

- 与非:与门+非门—> !(A&&B),先与再非;Y=(AB)‘=(A+B’)

- 与非门:全 1 为 0,有 0 为 1

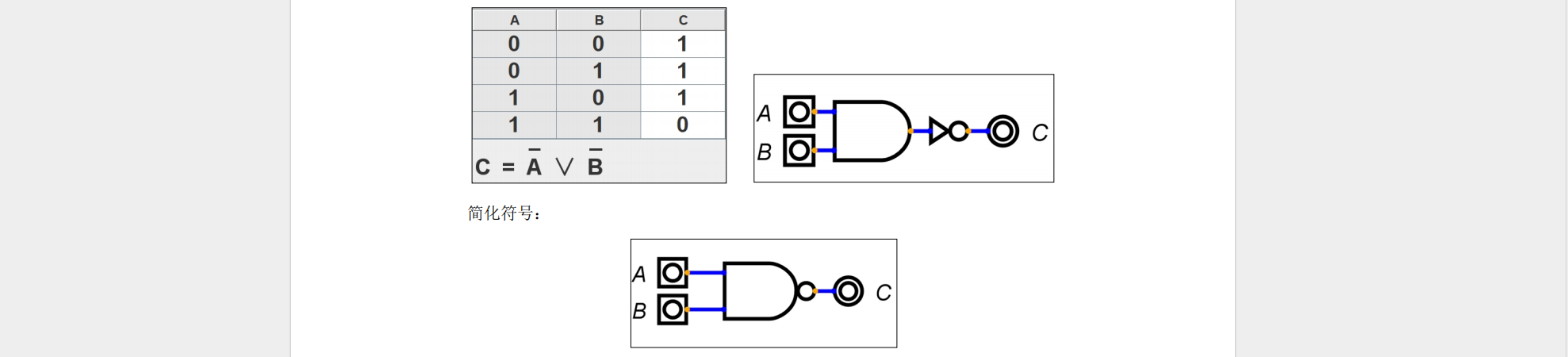

- 或非:或门+非门—> !(A || B),先或再非;Y=(A+B)‘=A’B’

- 或非门:全 0 为 1,有 1 为 0

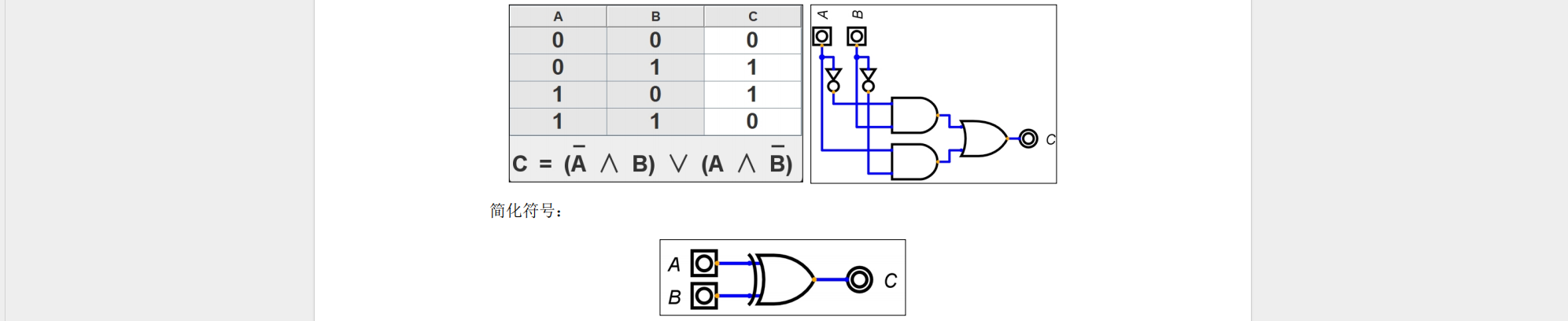

- 异或:异或~A^B,相同为 0 不同为 1,两个输入不同–>输出 1,输入相同–>输出 0,Y=A’B+AB’

(一)偶数个 1 异或为 0,奇数个 1 异或为 1,多少个0 异或均为 0

(二)偶数个 1 同或为 1,奇数个 0 同或为 0,多少个 1 异或均为 1

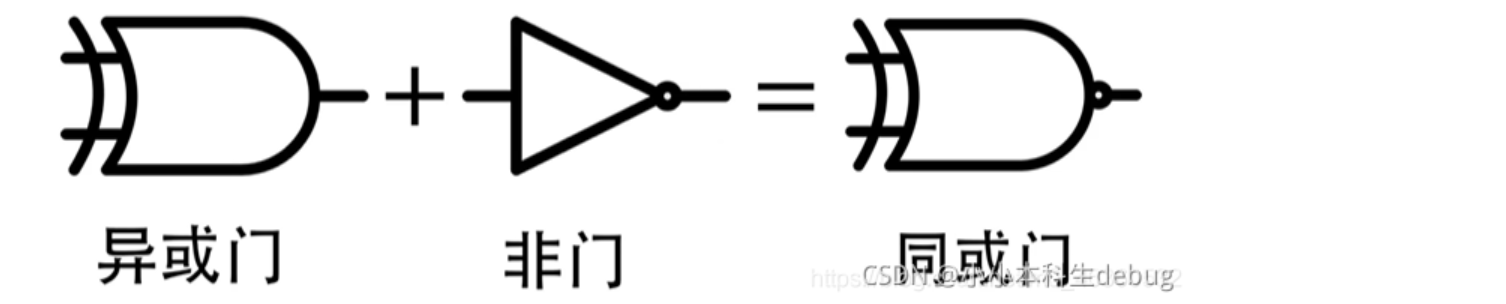

- 同或:异或门+非门—>!(A^B),和异或相反,先异或再非,相同为 1,不同为 0,两个输入不同–>输出 0,输入相同–>输出 1,Y=AB+A’B’

- 总结:三态门的输出有三种状态,高电平,低电平,高阻态;普通门电路只有前两种

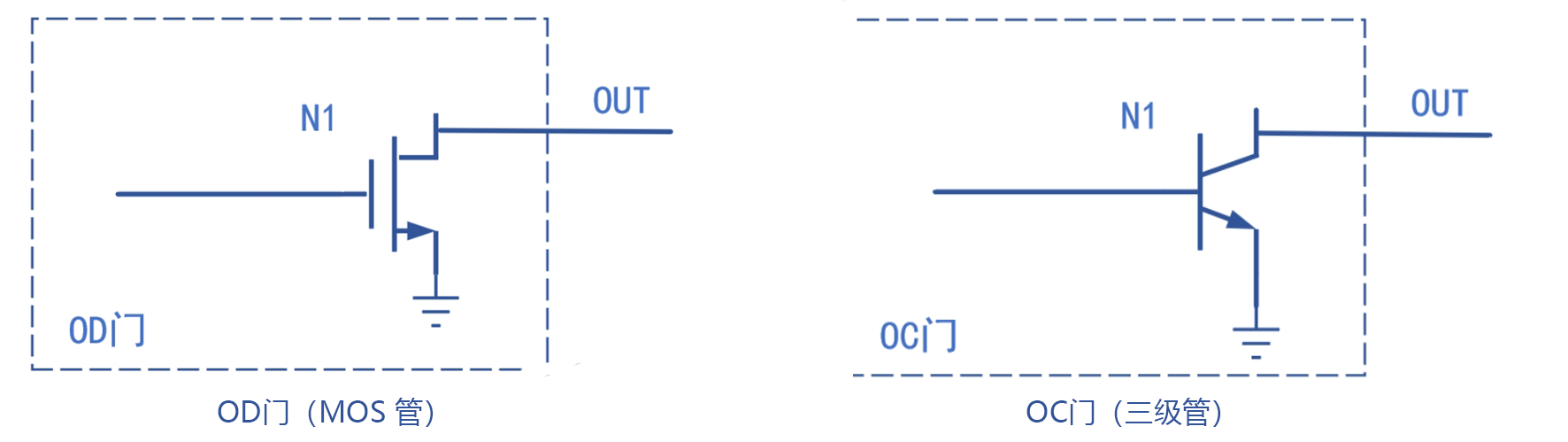

7、OC 门和 OD 门

- OD 门(Open Drain Gate):漏极开路门,与 OC 门类似,当 N 1 导通时,输出低电平;当 N 1 截止时,输出高阻态

- OC 门:集电极开路门,当 N 1 导通时,输出低电平;当 N 1 截止时,输出高阻态(电路的一种输出状态,既不是高电平也不是低电平,电路分析时可以理解为开路)

- OC 门与 OD 门在实现的功能上是相同的,区别在于 OC 门是对于三极管而言,OD 门是对于 MOS 管而言

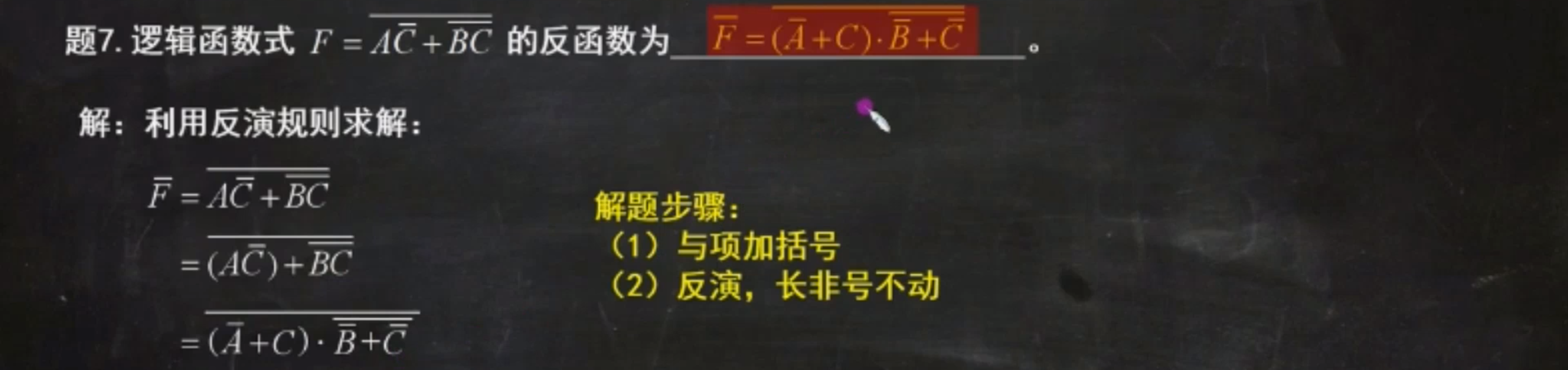

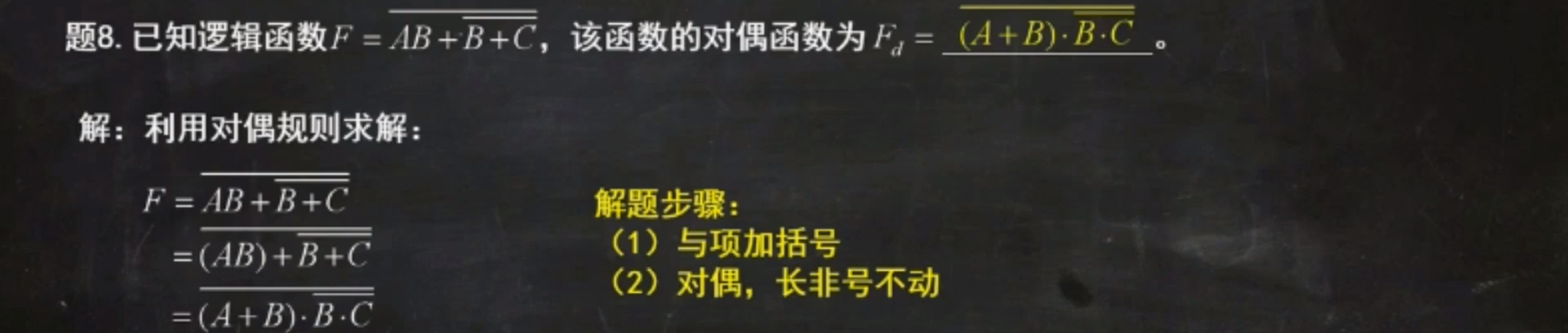

8、规则及常用形式

- 反演规则

- 对偶规则

9、卡诺图

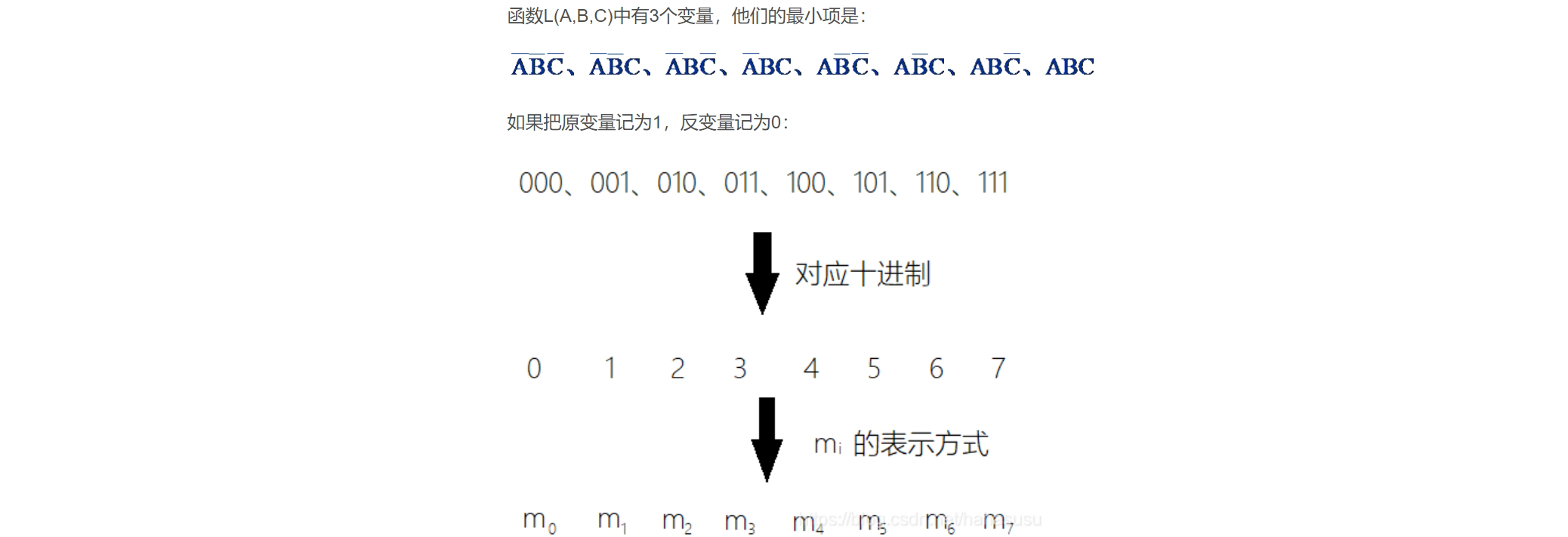

- 最小项:一个函数的某个乘积项包含了函数的全部变量,其中每个变量都以原变量或反变量的形式出现,且仅出现一次,则这个乘积项称为该函数的一个标准积项,通常称为最小项(n 个变量就有 n 个逻辑相邻项)

(一)最小项的表示方法:通常用 mi 来表示最小项

(二)下标 i 的确定方式:把最小项中原变量记为 1,反变量记为 0,当变量顺序确定后,可以按顺序排列成一个二进制数,则与这个二进制数相对应的十进制数,就是这个最小项的下标 i

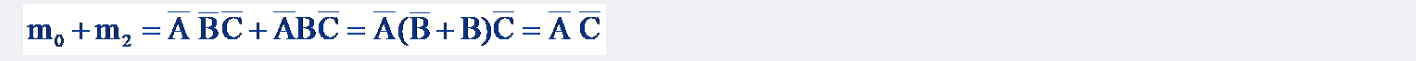

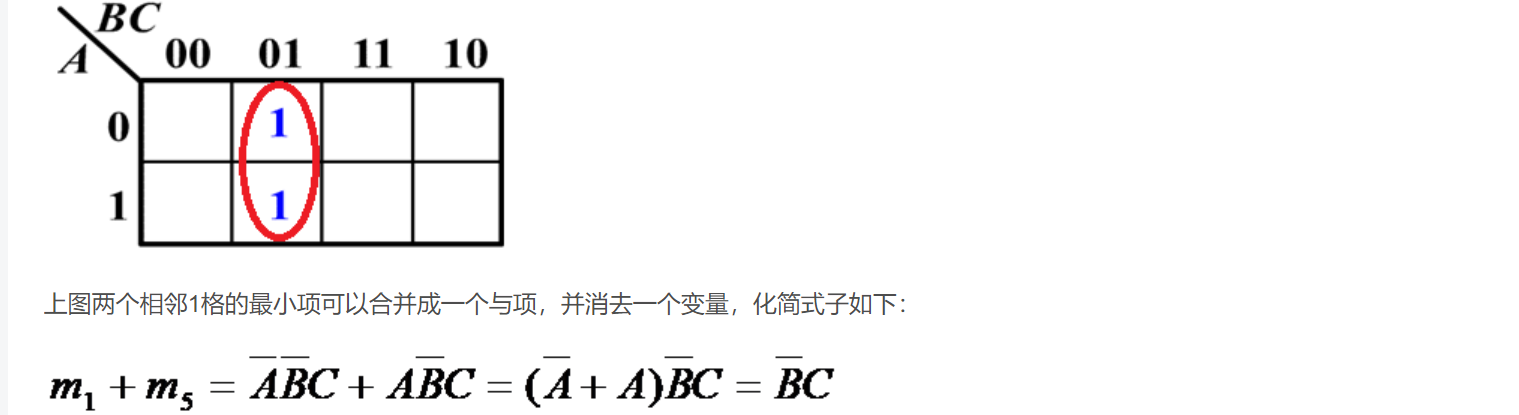

- 最小项的相邻性:相邻的两个最小项之和可以合并一项,消去一个变量

- ABCD,字母上面划横线的就是 0,不划线为 1

- 卡诺图的记忆

(一)在方格图中,每一个方格代表逻辑函数的一个最小项,几何相邻(在几何位置上,上下或左右相邻)的小方格具有逻辑相邻性,即两相邻小方格所代表的最小项只有一个变量取值不同

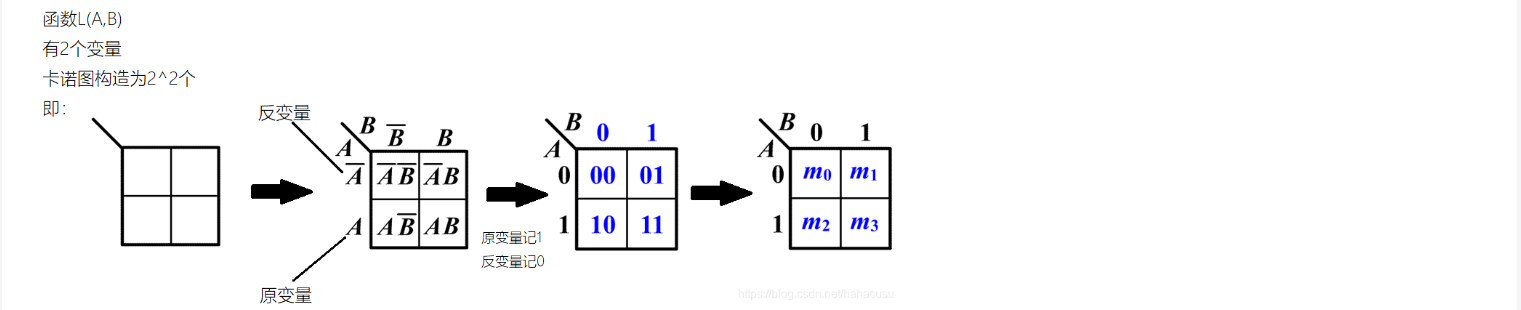

(二)对于有 n 个变量的逻辑函数,其最小项有 2n 个(该逻辑函数的卡诺图由 2n 个小方格构成)

(三)二变量的卡诺图

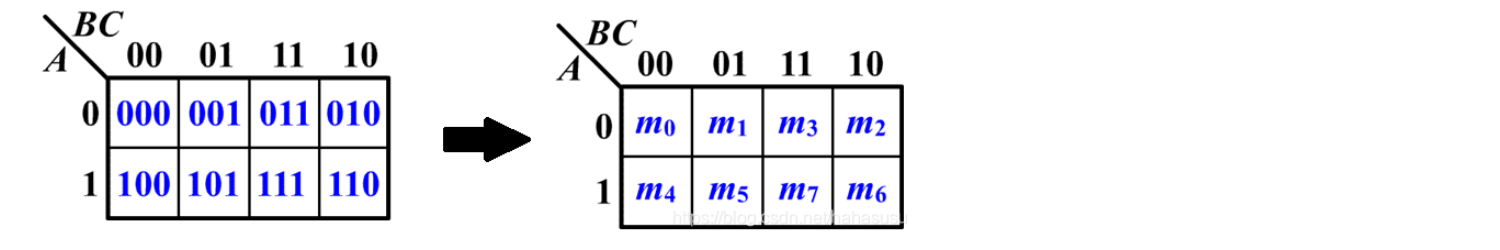

(四)三变量卡诺图(四变量也同理,方格列行均按顺序 00、01、11、10)

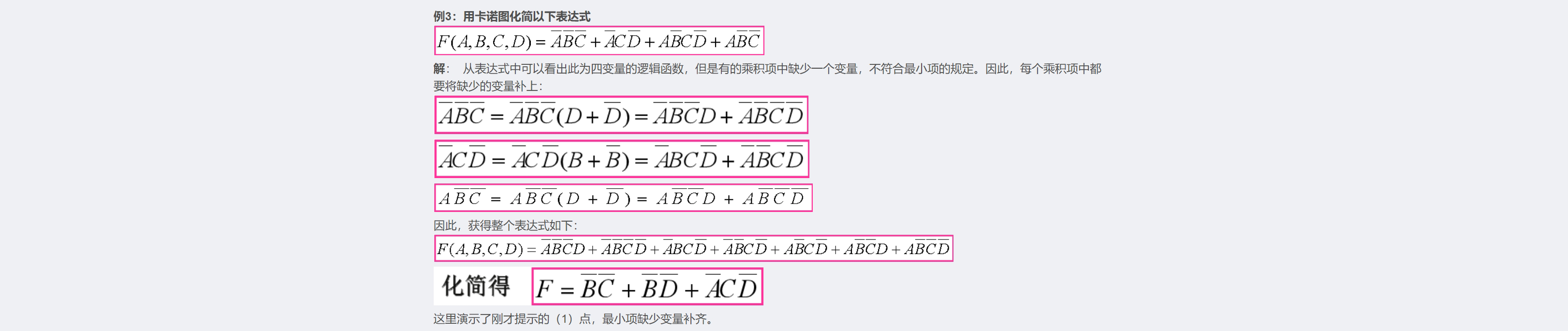

(五)四变量卡诺图(图中的表达式比较特殊,直接找对应字母的重合格子填 1)

- 卡诺图画法

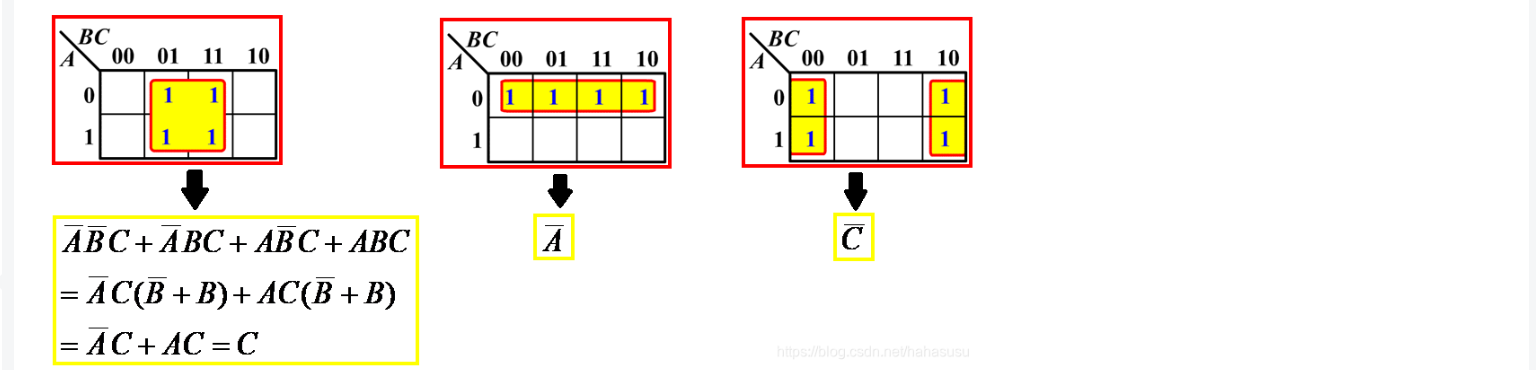

卡诺图中两个相邻 1 格的最小项可以合并成一个与项,并消去一个变量

卡诺图中四个相邻 1 格的最小项可以合并成一个与项,并消去两个变量

卡诺图中八个相邻 1 格的最小项可以合并成一个与项,并消去三个变量

(一)两个相邻的举例

(二)四个相邻的举例

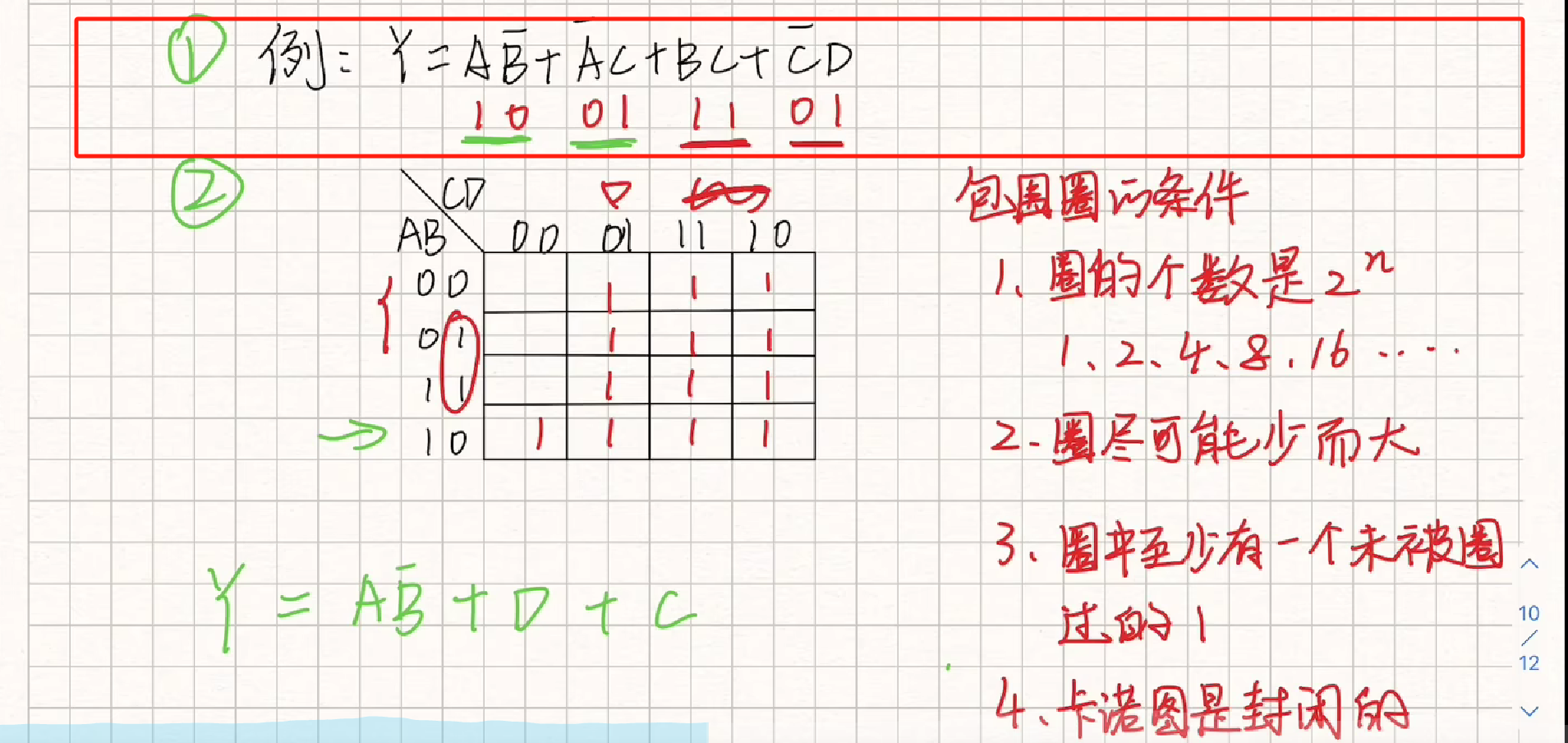

- 解题步骤

(一)先把表达式中 A B C 等参数化为二进制,用 0 和 1 表示,然后找到对应的重合位置(所有行列)填上 1

(二)画圈,相邻的方格都为 1 即可合并为一个圈(消去这个不同的变量,只保留相同的变量)

- 理解画圈化简:直接看轴上的数(横竖都要看,一个圈一个圈看),如图蓝色圈中有 001 和 011,B 发生了变化,消去 B 得到 AC(保留相同的)

- 另外圈笼罩四行的情况:由于 11 与 00,10 和 01 互相消除没有重复,直接不用看

(三)注意对称的 1 是连通的(圈数量不要 2n),但一个圈 2n个方格组合(即圈内的格数必须为 1,2,4,8 等),卡诺图化简所得不唯一

- 特殊情况:化简表达式的时候四变量所有的乘积项都应为四变量,缺少的要补齐,然后重新化简

三、半加器和全加器

1、半加器

- 半加器:完成 1 位二进制相加的一种组合逻辑电路,没有考虑低位来的进位,所以称为半加,A 和 B 是相加的两个数,S 是半加和数,C 是进位数(如半加法器真值(可以看作 A 与 B 二进制 0 与 1 不考虑进位相加,也可以看作 A 异或 B

注意理解:半加器就是一个与门和异或门组成,与门输出进位 C,异或门输出和 S(S 运算刚好是异或的结果)

(一)半加器有两个输入端:A 和 B;两个输出端:和 S、进位 Ci

(二)由一个异或门和与门组成;异或门用于产生和 S,与门用于产生进位 Ci(由于 AB 产生进位才有 Ci,故 AB 与门产生 Ci)

(三)和 S 可以通过异或运算得到,即 S = A ⊕ B;进位 Ci 通过 A 与 B 与运算得到

2、全加器

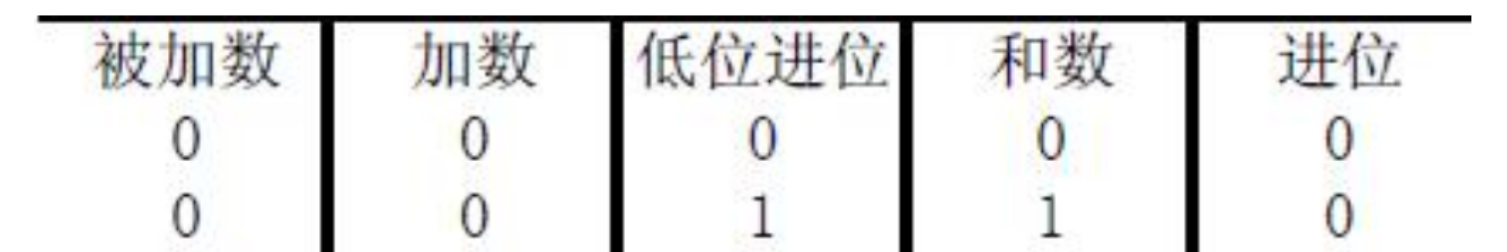

- 全加器:进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的、进位信号 > 两个半加器 + 或门 = 全加器

(一)全加器有三个输入端:A、B、低位进位 Ci-1;两个输出端:和 S、进位 Ci

(二)全加器是由一个半加器加上一个额外的与门、一个额外的异或门(用于计算和位 S)、一个额外的或门(用于计算进位 Ci)

(三)和 S 通过异或运算和与运算的组合得到,表达式为 S = A ⊕ B ⊕ Ci-1;进位 Ci = A 与B + Ci-1与A + Ci-1与B(这里注意+是或,⊕是异或,只要Ci-1、A、B 中任意两个数为 1,Ci 就为 1,可以简化为 Ci = A 与 B + Ci-1与(A+B))

- 半加器 S 就是 A+B,全加器 S 是 A 与 B 与 C(低位进位)三个数的异或

- 如图示,第一个半加器输入 A 和 B,第二个半加器输入 C 低位进位和 S,再将两个进位或运算

- 全加器的逻辑表达式:如图做题步骤是先在旁边标出逻辑门的表达式,再直接化简(两个非可以抵消)

- 前给的进位会记入下一个的和 S,加起来超过 1 就会影响进位

3、竞争与冒险

- 组合逻辑电路中的竞争冒险是由电路中存在延时引起的

4、理解二进制相加

- 正数与负数的相加原理是,实际上是正数与负数的补码相加,如 8 和(-3),看成 8+(-3),结果是 0101(5)

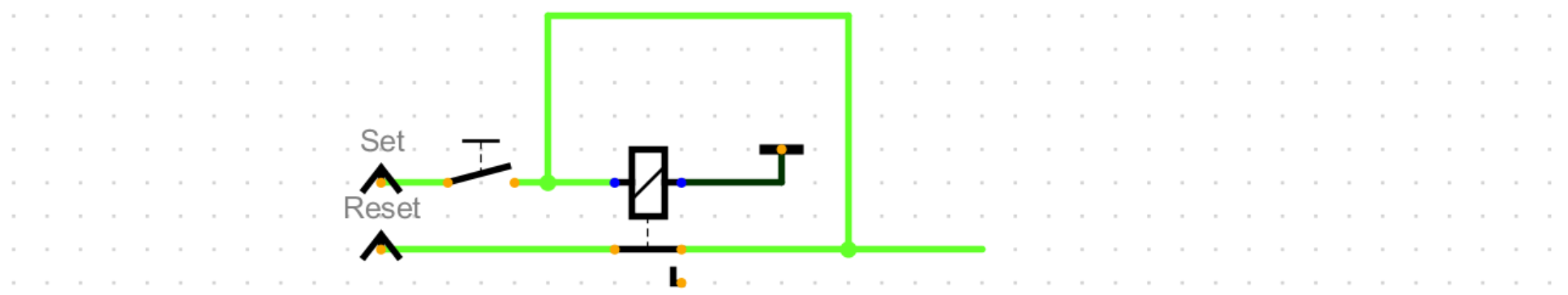

5、用电去记录电的原理

- 输出的结果反向接入到输出端

6、解码器的工作原理

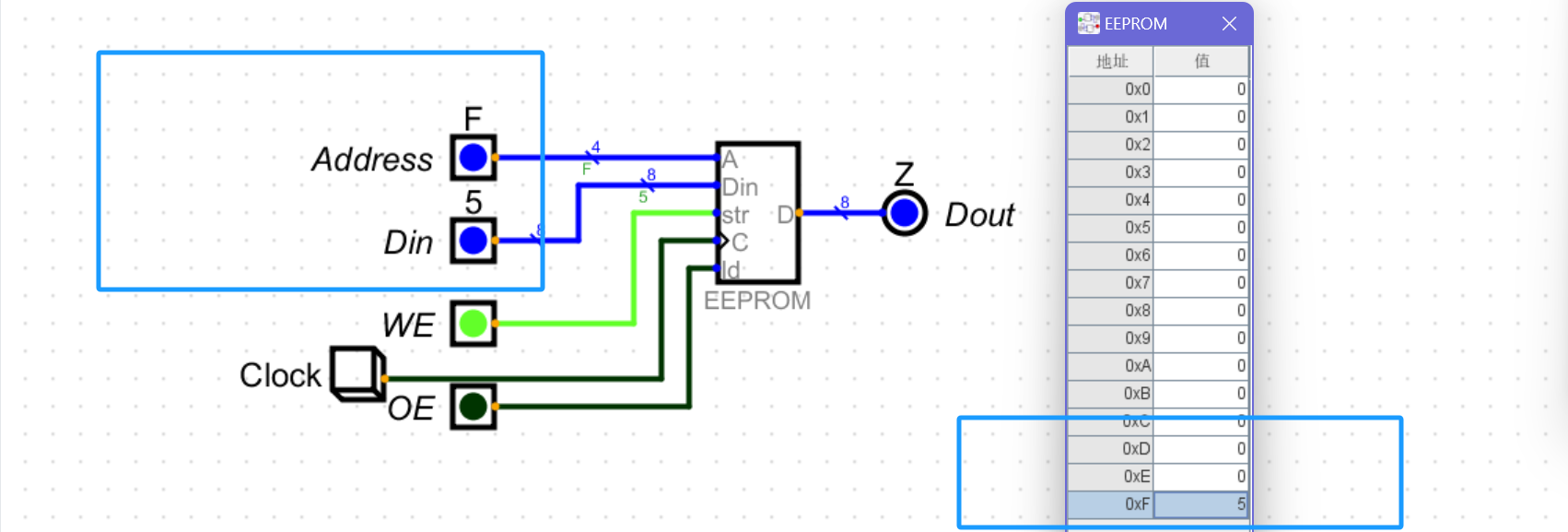

- WE 是写入数据(输入数据),OE 是读取数据(输出数据)

7、存储

- EPROM 和 Flash 都是可编程只读存储器(Programmable Read-Only Memory,PROM)的类型

- WE:输入数据开关;OE:输出数据开关;clock:时钟信号;Din:输入的数据,8 位的;Dout:输出的数据,8 位的;Stored data:内部存储的数据,用于方便观察调试

- 数据位数写一位和八位的区别(存储 1 和 0 / 以 bit 存储,1 bit = 8 位);地址位数是 n 位,那么可以寻址的存储单元数量就是 2^n 个(有多少个空间)

(一)可编程可擦除只读存储器(Erasable ProgrammableRead Only Memory,EPROM):一种可写可读的存储器。用户可根据需要来写入,并能把已写入的内容擦去后再改写的 ROM

(二)Flash :通过电子方式进行擦除,这种擦除方式称为电子擦除(Electrical Erase),通常使用高电压或者脉冲电压来擦除数,单片机常用 Flash

(三)如图,地址位数决定在哪输入数据,然后打开 WE 输入(写入),OE 输出(读取)

四、常用组合逻辑器件

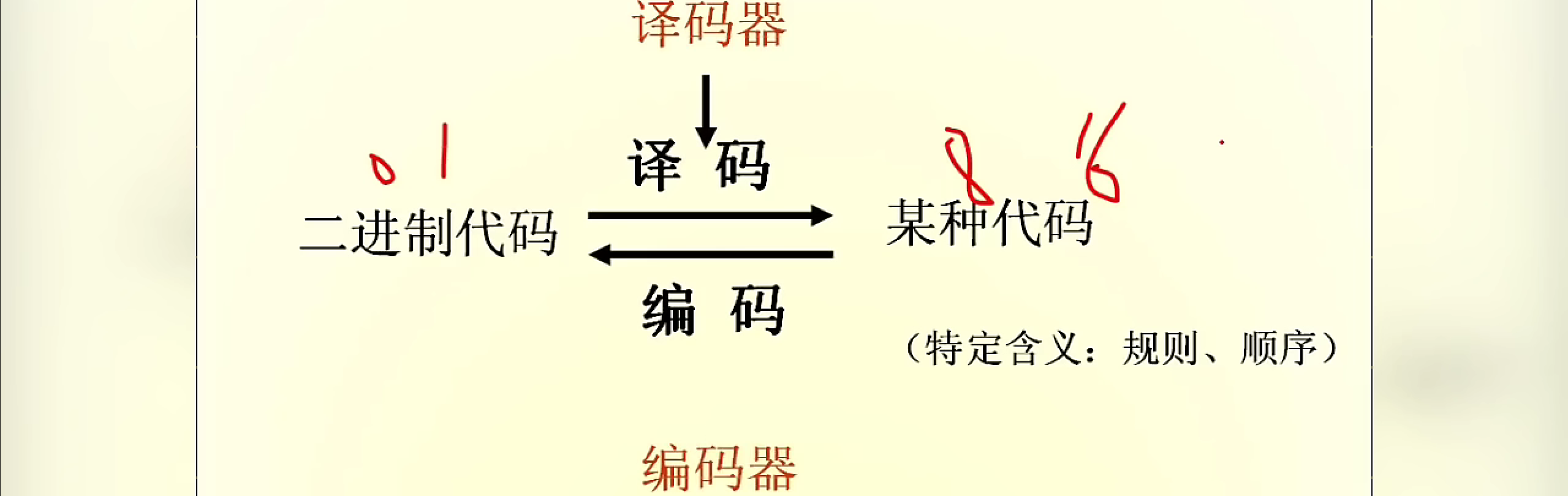

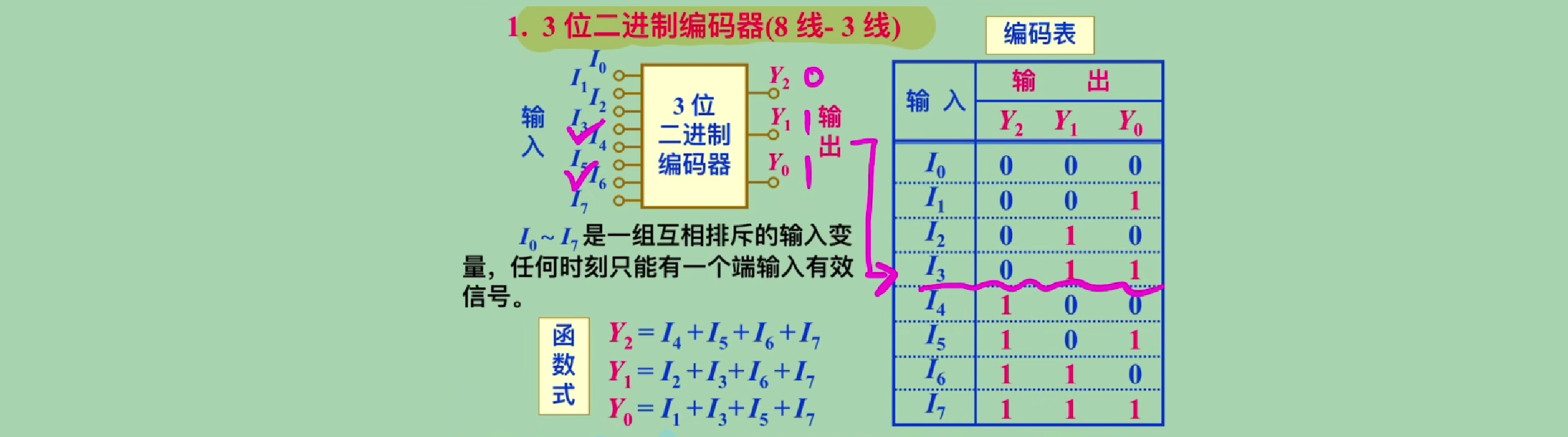

1、编码器(转二进制)

- 将其他进制(8,16)转换为二进制值,则为编码;将二进制转换为其他进制(8,16),则为译码

- 编码器类型:二进制编码器,二-十编码器,优先编码器

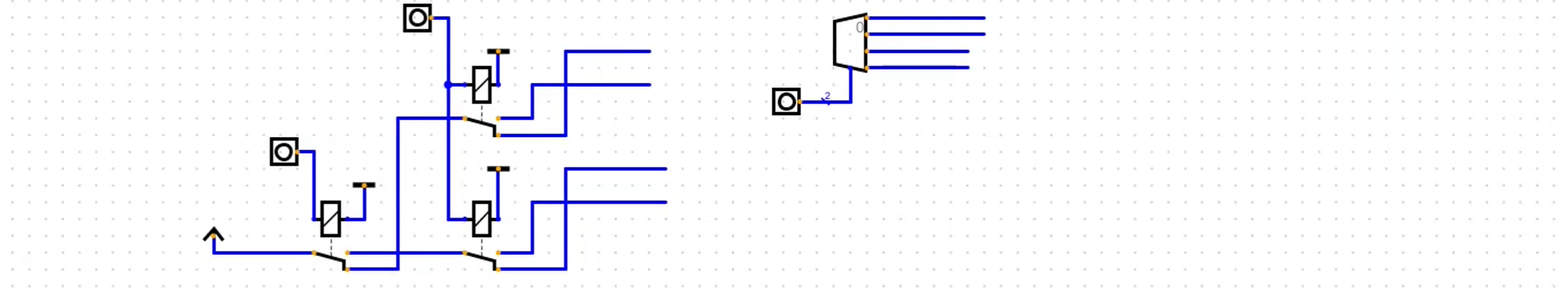

- 二进制编码器:三个输出,(0-7)八个数值(找输出的 1 的位置对应 1 的位置,如 Y0 = I1* I3 * I5 * I7)

同理,十进制编码器是 0-9 十个数字

- 一般是高电平有效的编码器,但如特殊的如 74148 是低电平有效的编码器

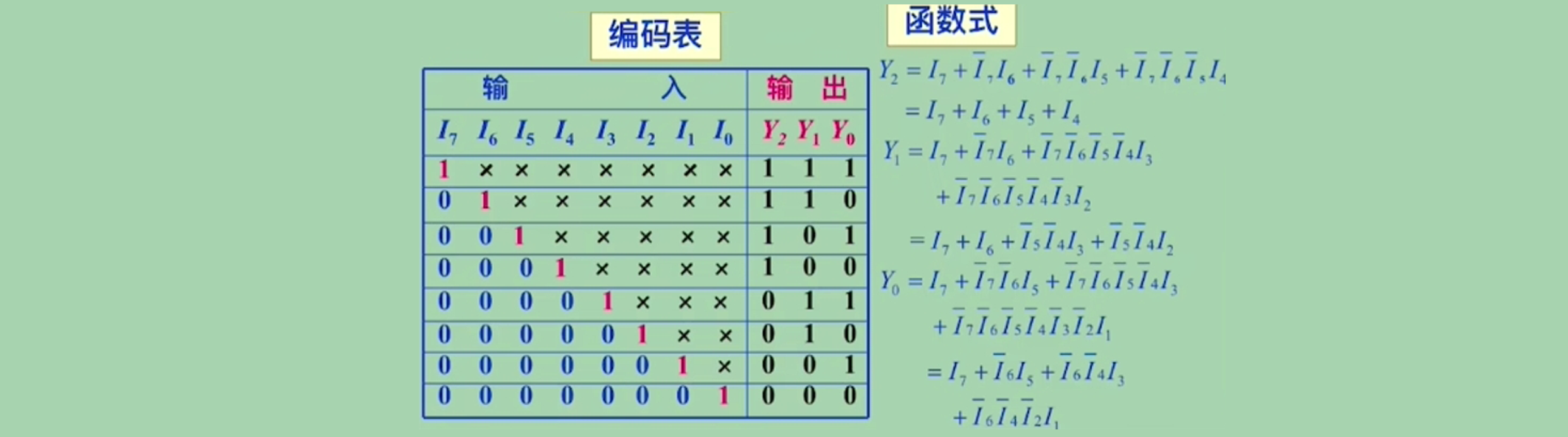

- 优先编码器:允许几个信号同时输出,但只对优先级别最高的进行编码

(一)如 74148 是 8 线-3 线优先编码器,编码输入输出均为低电平有效,若输入 I7 I6 I5 I4 I3 I2 I1 I0为 11011001,输出 Y2Y1Y0 应为(010)

- 依照上面:I5 非=0、 I2 非=0、 I1 非=0,I5优先级最高,由于是低电平有效,取反I5对应的Y2Y1Y0

- 普通编码器和优先编码器的区别:普通编码器任何时候只有一个请求;优先编码器允许多个请求,事先规定优先级

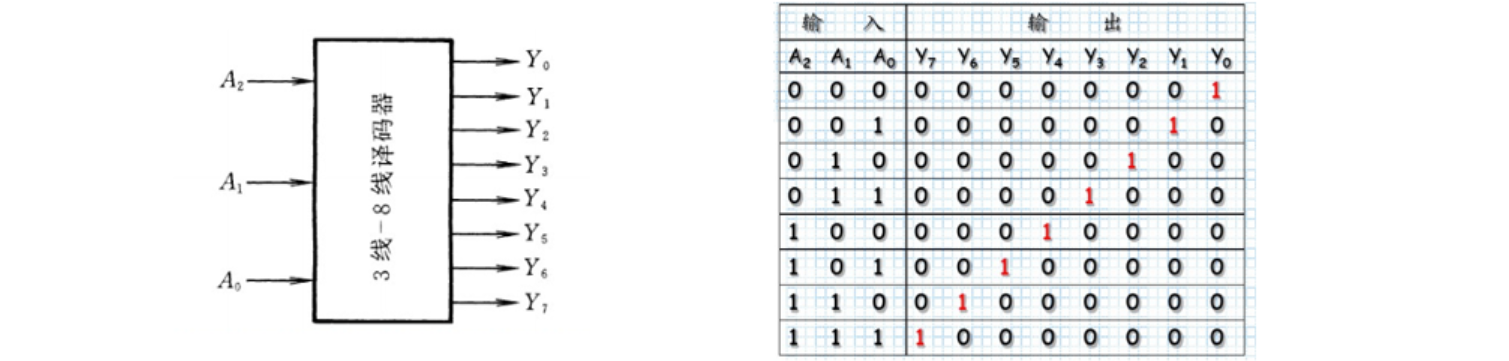

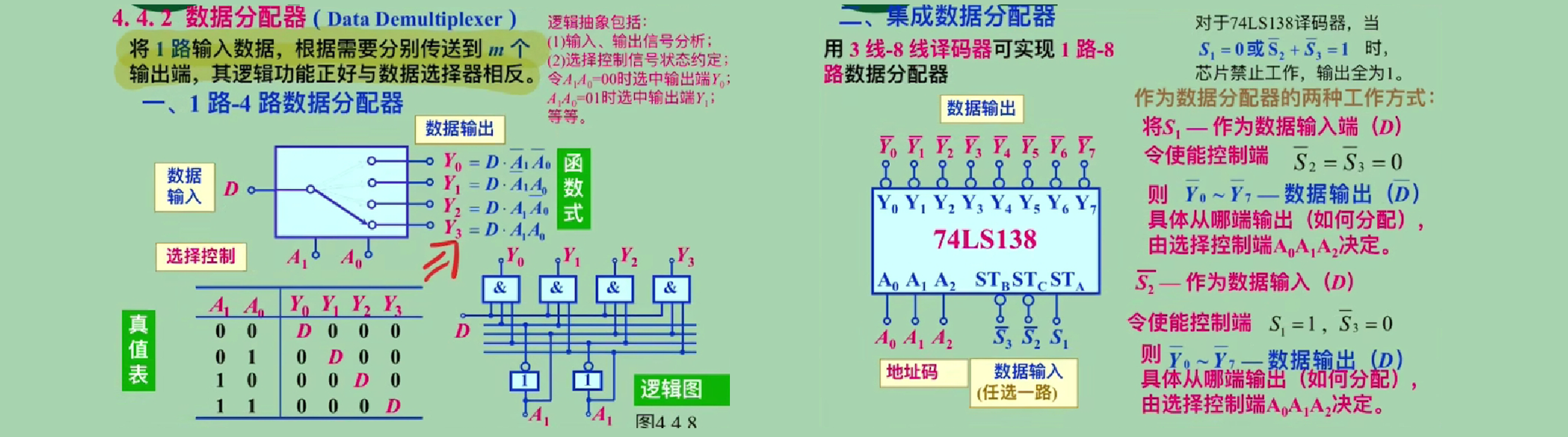

2、译码器(转十进制)

- 将输入的二进制码译成对应的输出高、低电平信号,如图 3 线-8 线译码器(译码器是左斜 1,编码器是右斜 1)

- 使能端:控制信号输入端;如 74LS138 的使能端两种情况, S1=0 或 S2 非 + S 3 非 = 1;S1 = 1 且 S2 非 + S3 非 = 0

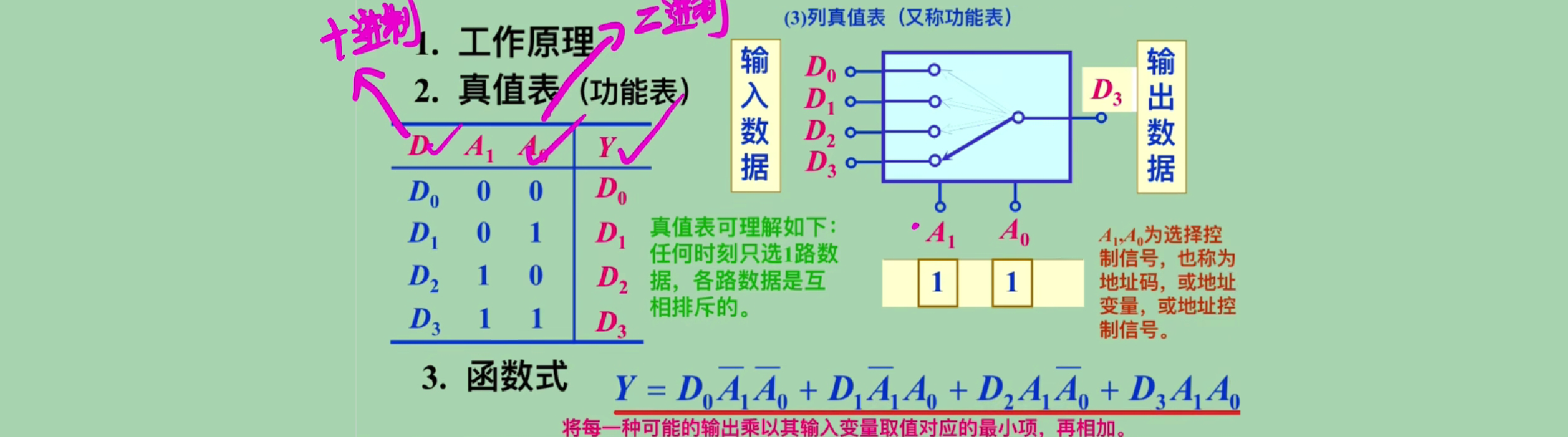

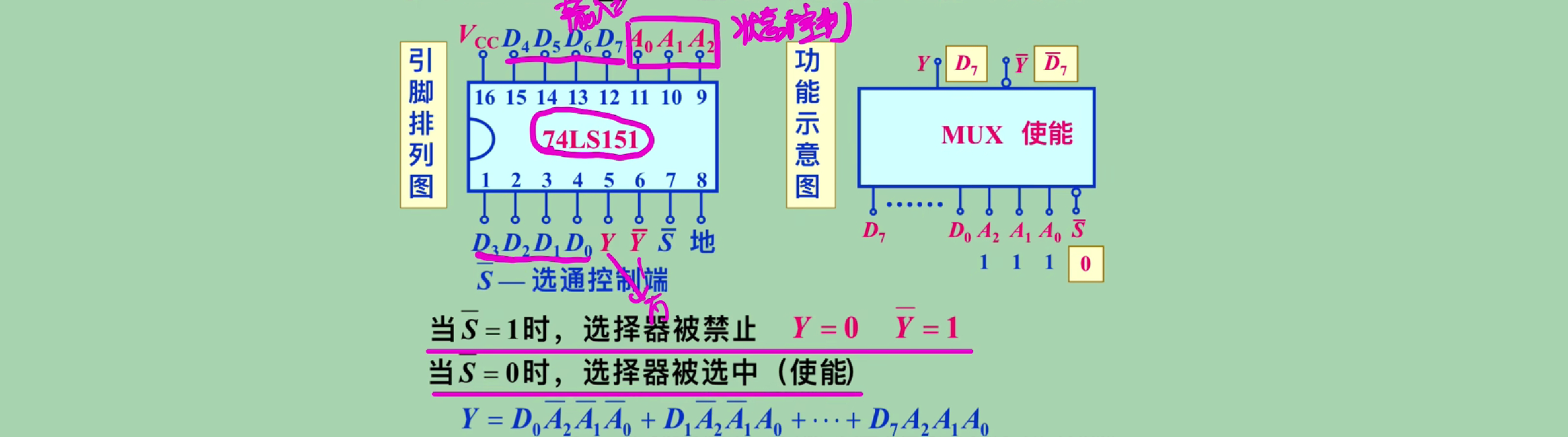

3、数据选择器

- 数据传输方式:并行传输和串行传输

(一)并行传输:数据以成组的方式,在多条并行信道上同时进行传输(有多个数据位同时在设备之间进行的传输)

(二)串行传输:使用一条数据线,将数据一位一位地依次传输,每一位数据占据一个固定的时间长度

- 数据选择器就是把并行传输->串行传输;数据分配器就是把串行传输->并行传输(A1 A0 是二进制表示,D0 等是十进制表示)

- 集成数据选择器:八选一的数据选择器,74151、74LS151、74251、74LS251

4、数据分配器

- 把串行传输->并行传输

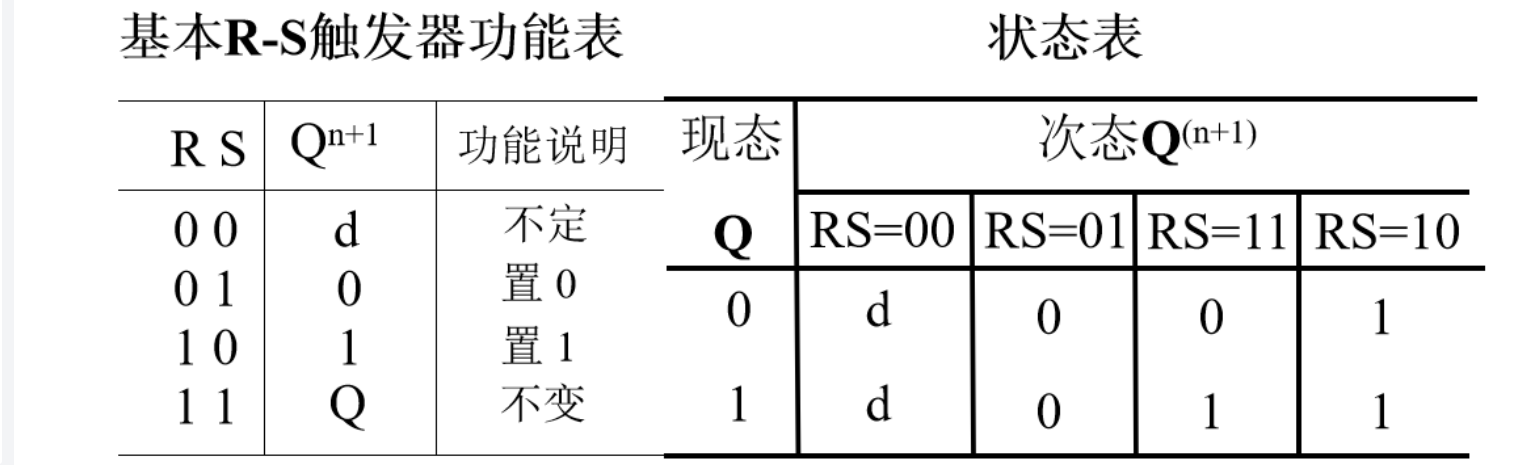

5、触发器

- 有两个稳定的状态(两个互补的输出端 Q 和 Q 非)(0、1),以表示存储内容;能够接收、保存和输出信号

- 通常将 Q = 1 和非Q = 0 称为“1”状态,而把 Q=0 和非Q=1 称为“0”状态。当输入信号不发生变化时,触发器状态稳定不变

- 现态和次态

(一)现态:Qn触发器接收输入信号之前的状态

(二)次态:Qn+1 触发器接收输入信号之后的状态(下图又叫次态真值表)

- 触发器分类

(一)按电路结构和工作特点:基本、同步、边沿

(二)按逻辑功能分:RS、JK、D 和 T(T’);其他::TTL 和 CMOS,分立和集成

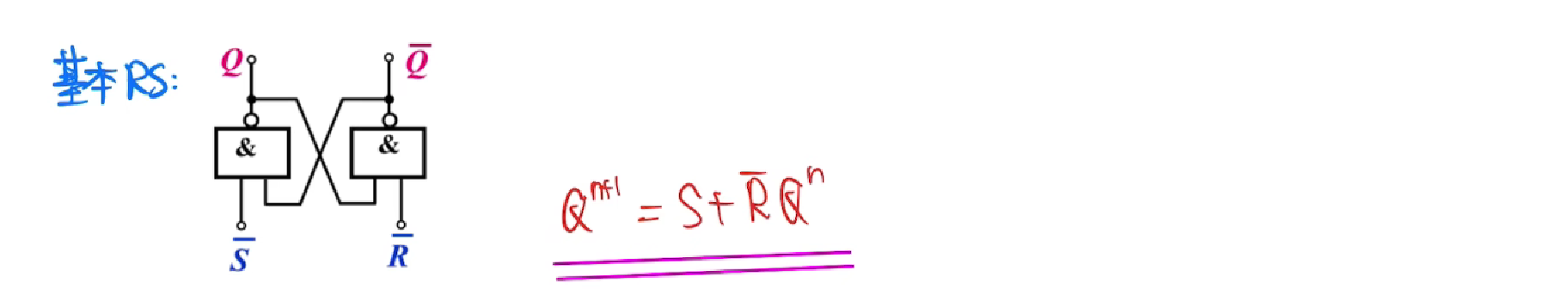

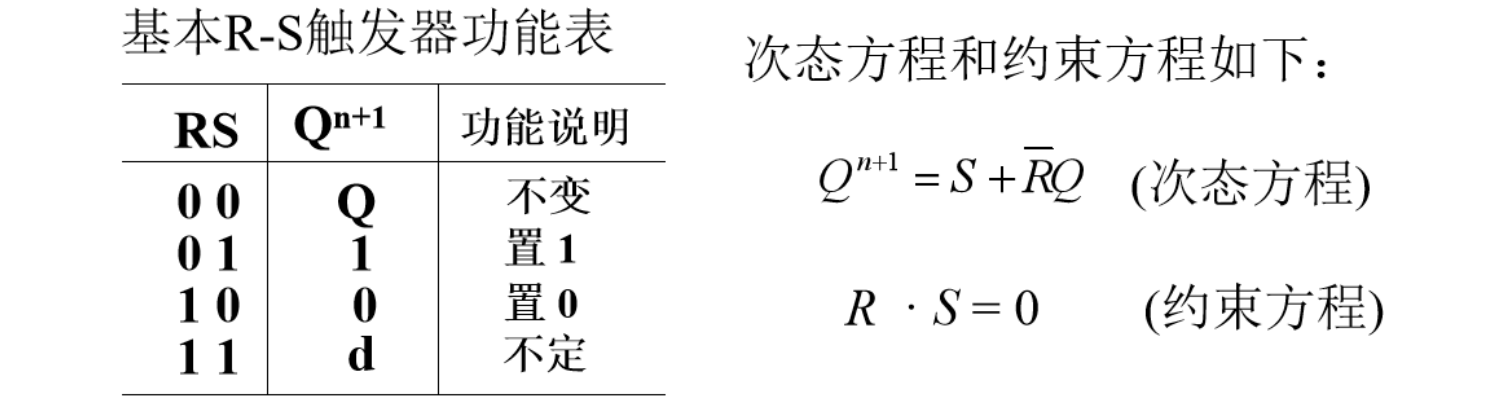

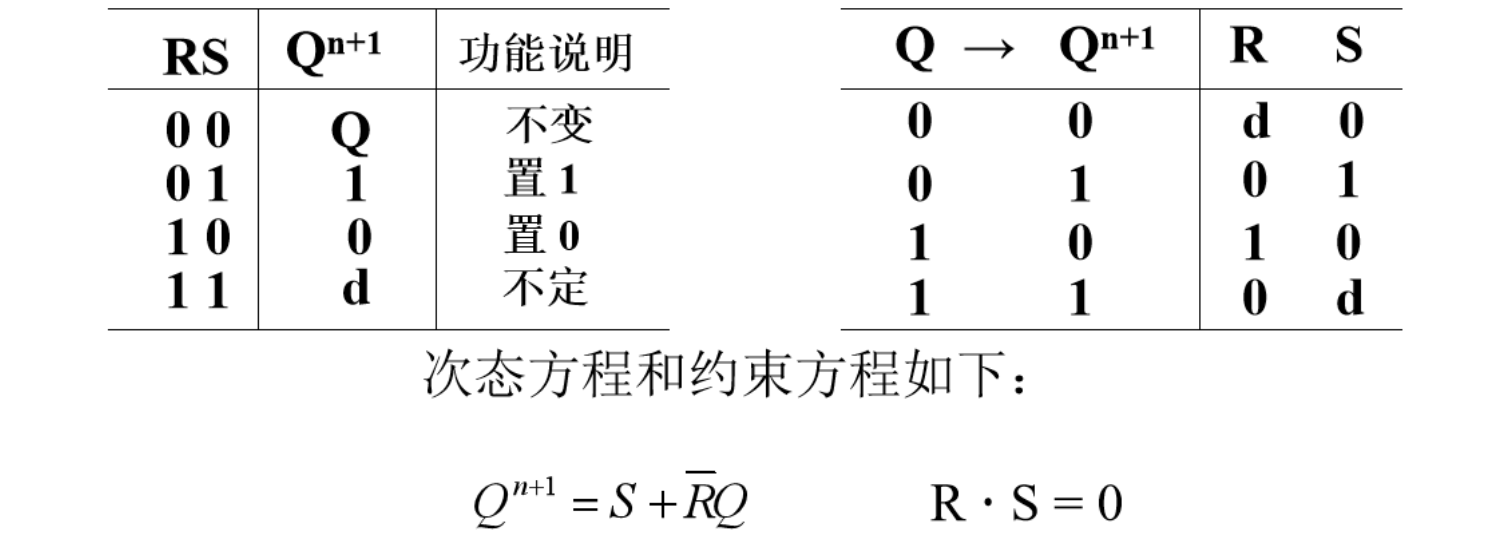

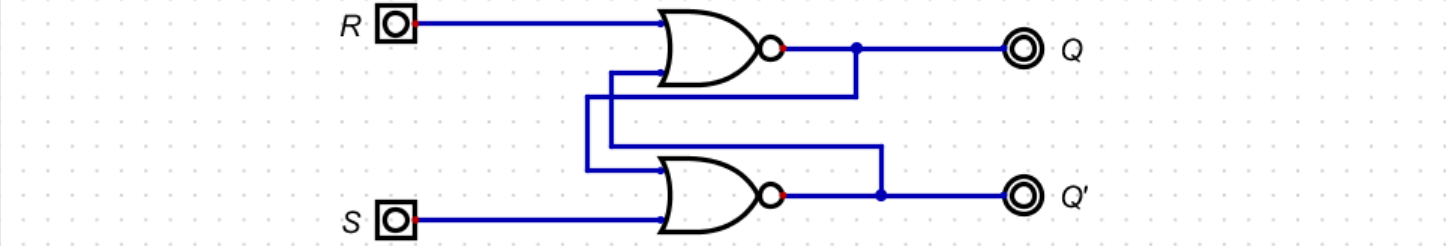

- 基本触发器: R 称为置 0 端或者复位端,S 称为置 1 端或置位端;逻辑符号输入端加小圆圈表示低电平或负脉冲有效

(一)与非门触发器:若 R=1,S=1,则触发器保持原来状态不变;若 R=1,S=0,则触发器置为 1 状态;若 R=0,S=1,则触发器置为 0 状态;不允许出现 R=0,S=0(RS 为 11 不变,10 为 1,01 为 0)

(二)或非门触发器:和与非门相反,RS 为 00 不变,01 为 1,10 为 0

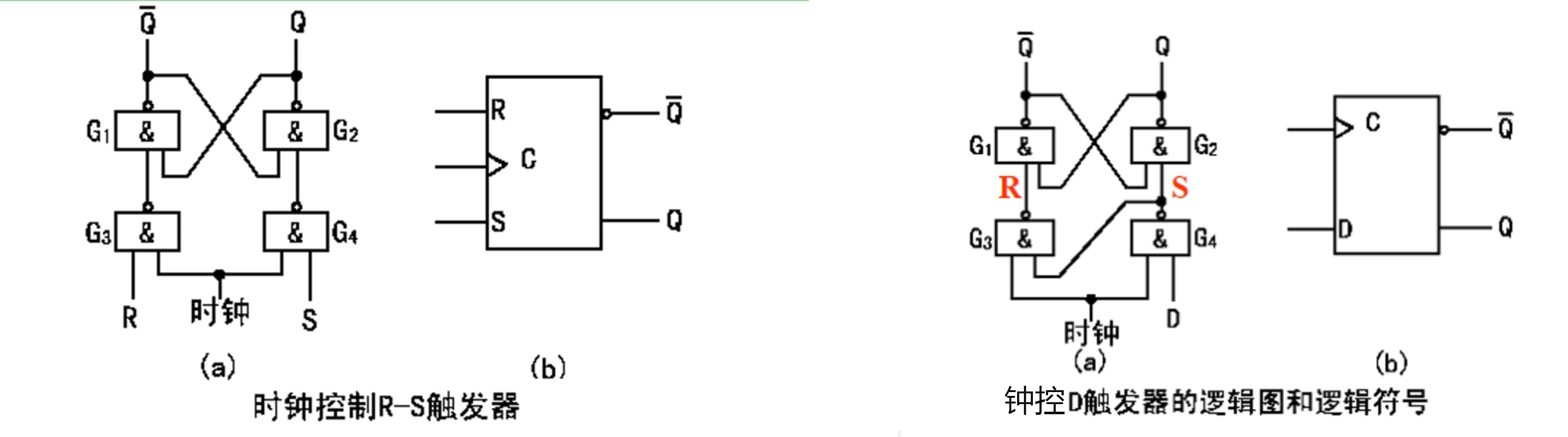

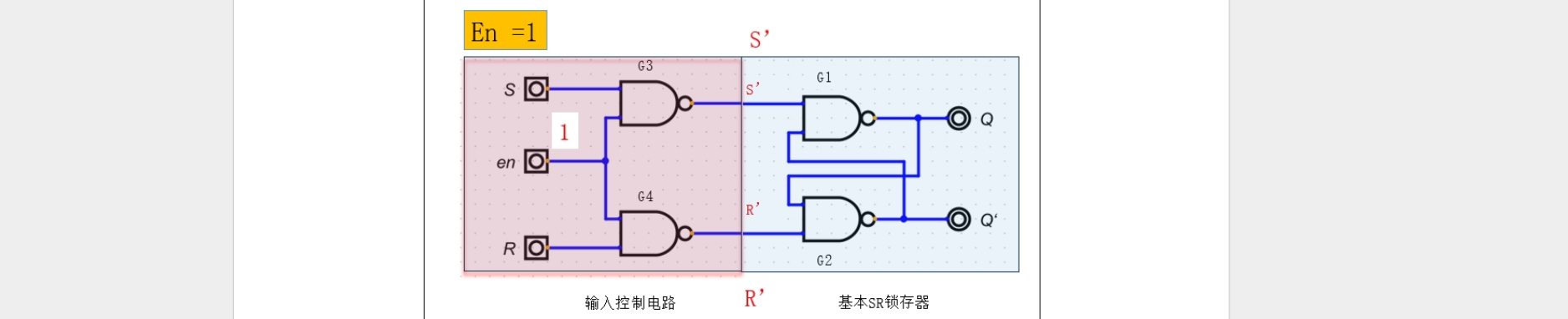

(三)时钟控制的 R-S 触发器:功能和或非门触发器一样,由四个与非门构成。其中两个与非门构成基本 R-S 触发器,另外两个与非门组成控制电路,通常称控制门

(四)钟控 D 触发器:无时钟脉冲作用(C=0)时,控制电路封锁,无论 D 为何值,与非门 G3、G4 输出均为 1,触发器状态保持不变

当时钟脉冲作用(C=1)时,若 D=0,则门 G4 输出为 1,门 G3 输出为 0,触发器状态被置 0;若 D=1,则门 G4 输出为 0,门 G3 输出为 1,触发器状态被置 1

时钟为低电平的时候,数据输入是无效的,只有当时钟为高电平的时候,数据的输入才会输出到 Q

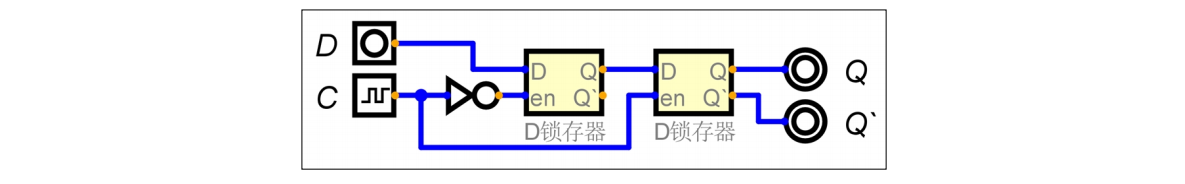

(五)边沿触发的 D 触发器 > C 信号不论是高电平还是低电平,Q 都不会随 D 变化;只有当 C 信号由 0 变 1 的一瞬间,D 的值能够传递到 Q

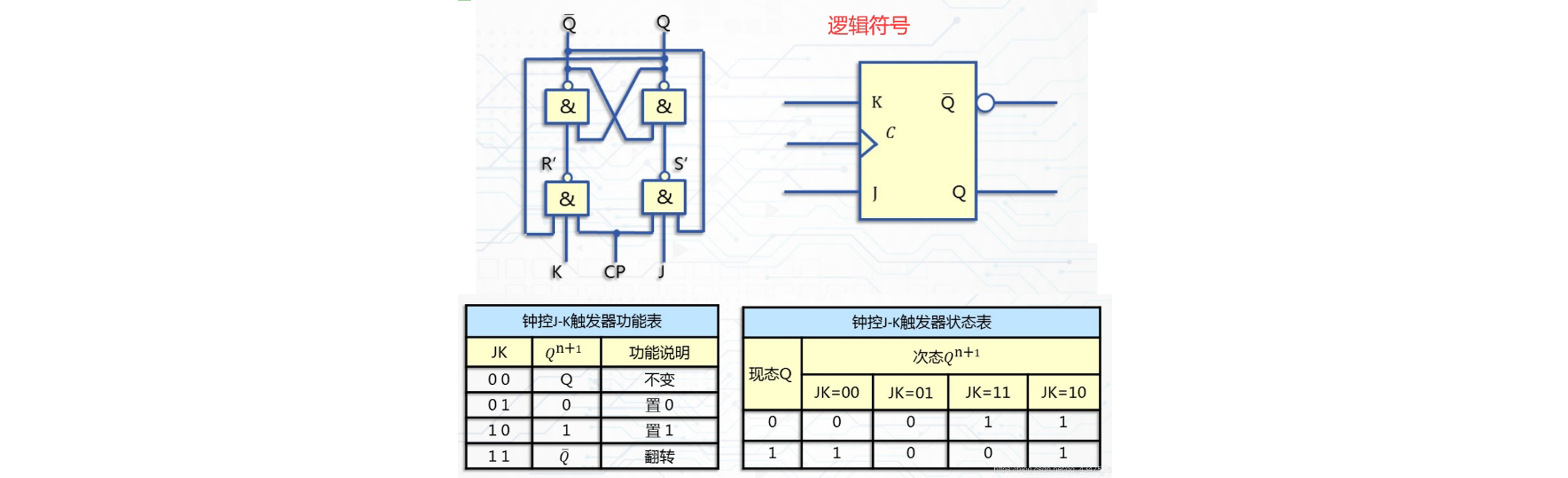

(六)钟控 JK 触发器:在时钟控制 R-S 触发器中增加两条反馈线,将触发器的输出交叉反馈到两个控制门的输入端,并把原来的输入端 S 改成 J,R 改成 K,即可改进成 J-K 触发器

五、其他逻辑器件

1、锁存器

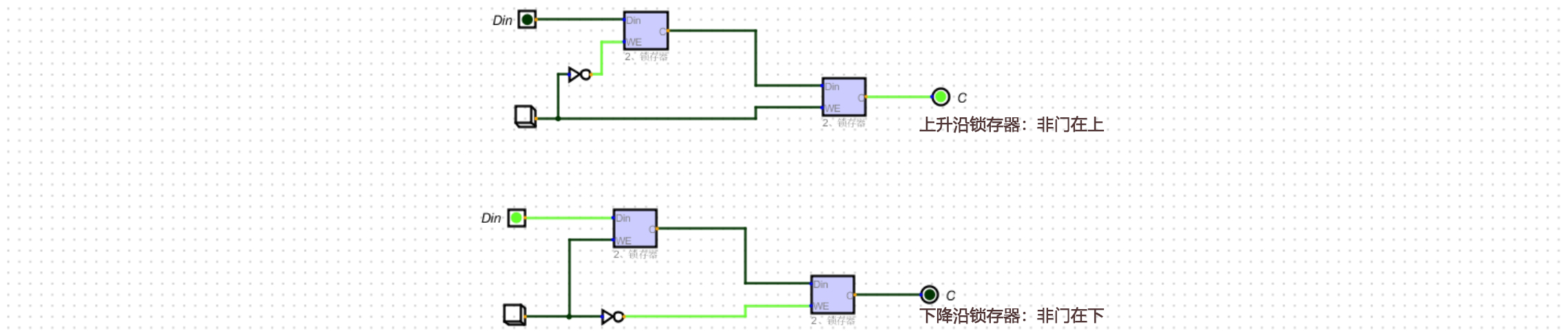

- 如图,两个与门把信号锁死,传不到后面去

也可以理解:把门打开,再用 Din 开关存东西进去,再关门,存了高电平;如果把门打开没有存东西,会自动存一个低电平

- 下降沿锁存器(Din 什么状态,按下按钮就存入什么状态,上升沿同理)

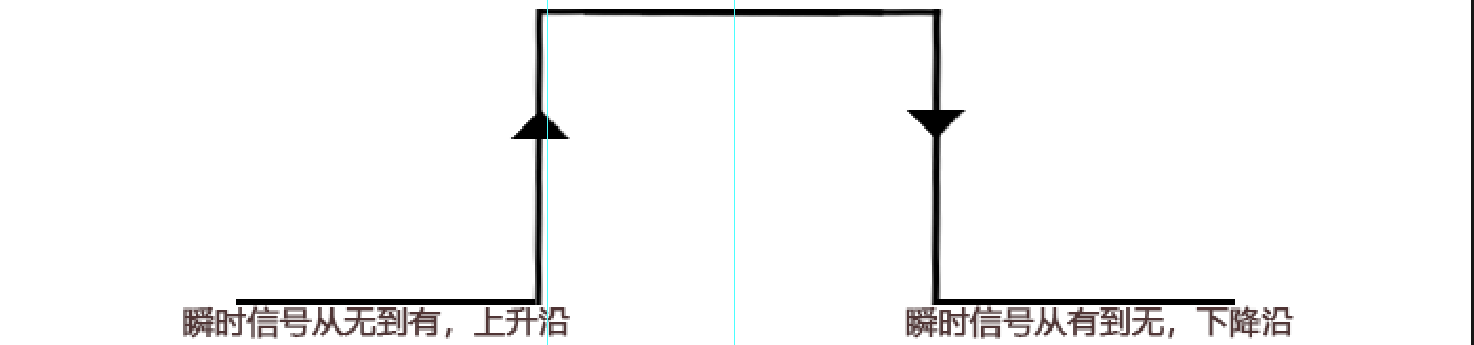

- 理解上升沿下降沿

2、时钟

- CPU 需要 clock 同步内部操作,精准的时间控制,确保每个内部操作在正确的顺序与速度内执行

- 边沿触发:边沿指信号的边缘变化,包括从低电平到高电平的上升沿,以及从高电平到低电平的下降沿

3、SR 锁存器

- 与非门和或非门 1,2 条均一样

(1)当S ’ 为0,R ’ 为 1, Q=1、Q ’ =0;(置位)

(2)当S ’ 为1,R ’ 为 0, Q=0、Q ’ =1;(复位)

- 与非门是S ’ 为1,S ’ 为 1,Q 和 Q ’ 状态不变,0,0电路无意义

- 或非门是S ’ 为0,S ’ 为 0,Q 和 Q ’ 状态不变,1,1电路无意义

SR锁存器的约束条件:S ’ + R ’ = 1

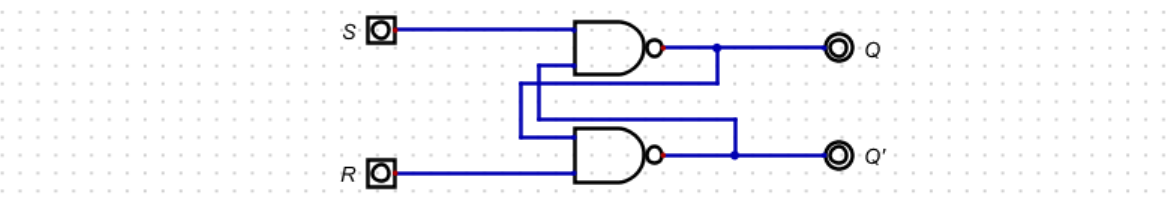

有两种构成方式。由两个或非门构成。由两个与非门构成,如图是两个与非门

SD(称为置位端,或者置 1 输入端),RD(称为复位端,或者置 0 输入端)(Set 和 Reset)

- 理解(但 SD=0 就是不置 1,当 RD=0 就是不置 0;故原输出保持不变)

RS 锁存器是异步的,其状态变化直接由 R 和 S 的输入控制,不受时钟信号的影响

同步 RS 触发器(可视为带时钟控制的 RS 锁存器)是同步的,其状态变化仅在时钟信号的特定边缘上发生,由 R 和 S 的输入以及时钟信号共同决定

- 如图是或非门

- 如图是与非门

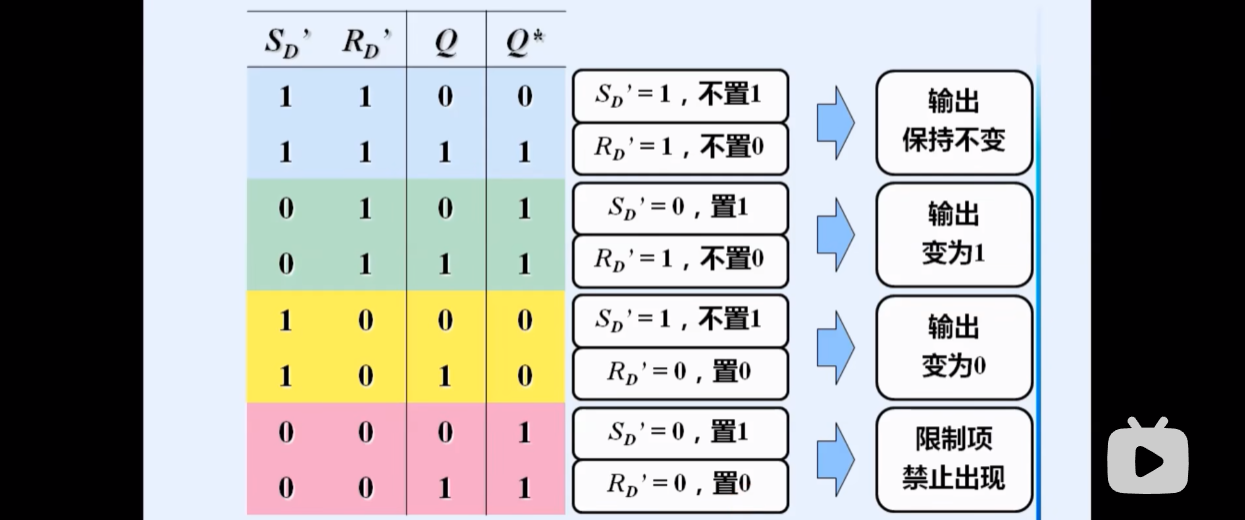

- 或非门总结:注意 Q 为初态(初始输出状态),Q’为次态(下一时刻输出状态)

(一)S =1,R =0 时,输出 Q‘均为 1

(二)S =0,R =1 时,输出 Q‘均为 0

(三)S =0,R =0 时,(不置 0 和 1)输出保持不变

(四)S = 1,R =1 时,限制项禁止出现(SD=1,RD=1 时,当 S、R 同时回 0 后,无法判断锁存器回到“0”还是“1”状态。因此,正常输入信号应遵循 SDRD = 0 约束条件)

(五)Q’ = S+R’Q,SR=0

- 与非门总结

(一)SD = RD = 1 时,输出保持不变(注意有状态变化,如 0 ->1,则没有到达稳定,还需要传一次数据)

(二)SD =0, RD = 1 时,输出 Q’ 变为 1

(三)SD =1, RD = 0 时,输出 Q’ = 0

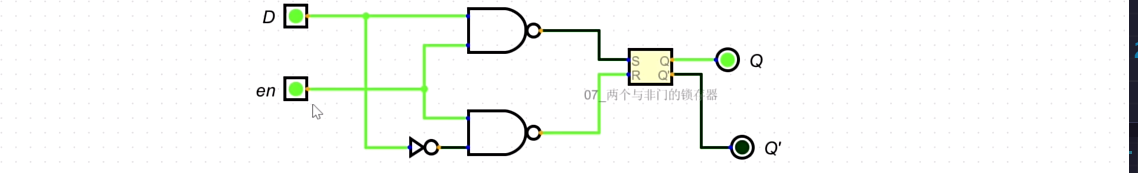

4、带 en 输入的 D 锁存器

- 使能端En:D锁存器的使能端用于控制何时锁定数据。当使能端E为高电平时,锁存器处于活动状态,数据输入D的值会被锁定到输出端Q。当使能端E为低电平时,锁存器处于非活动状态,输出端Q保持前一次锁定的值不变(按一下存进去了,再按一下不变)

- D 锁存器通常具有两个互补输出端 Q 和 Q’,分别表示输出的正常值和反相值(方便后续电路的连接)

- En = 0 时,输出保持不变;当 en=1 时,与非门 G 3 输出就是 S’,与非门 G 4 的输出就是 R’

- 当 en 为 1 时,输出 Q’ 的值与 D 输入的值相同 (即有一个存数据的功能)

- 注意:上升沿触发 / 下降沿触发可以在信号变化的瞬间立即触发,而不需要等待信号稳定在一个特定的电平(D 触发器)

- D 触发器的输出端 Q 只在下一个时钟脉冲到来时更新,而 D 锁存器的输出端 Q 会立即更新

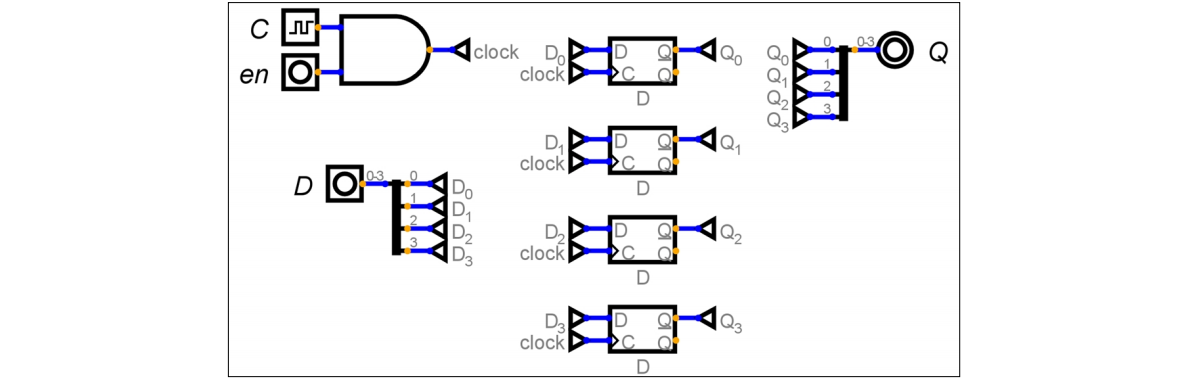

5、寄存器

- D 触发器可以在时钟上沿存储 1 bit 数据,如果我们想存储多个 bit 的数据,就需要用多个 D 触发器并联实现,这种电路我们称之为寄存器

- 4 bit 输入 D 会在时钟输入上升沿存储到 Q,再给这个寄存器加上 en 信号如下

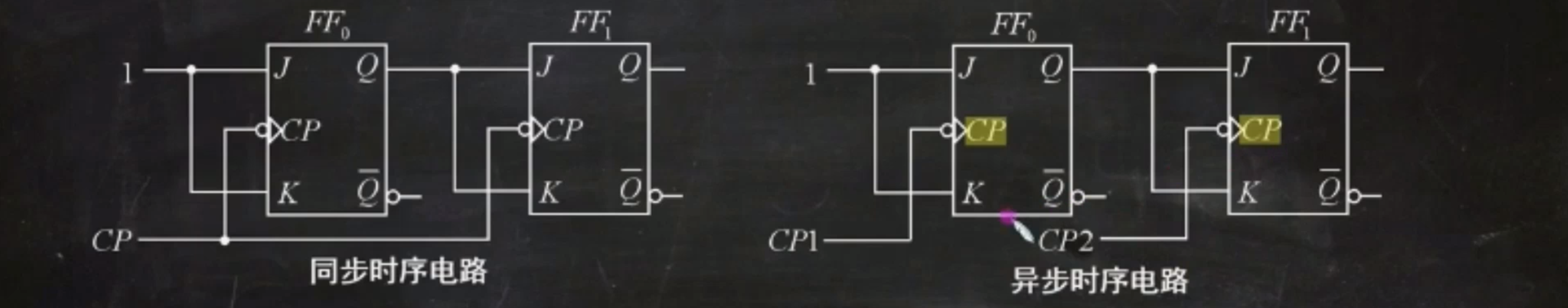

6、时序逻辑电路

- 同步时序电路:所有触发器共用一个触发信号源 CP

- 异步时序电路:触发器没有共用一个 CP 源

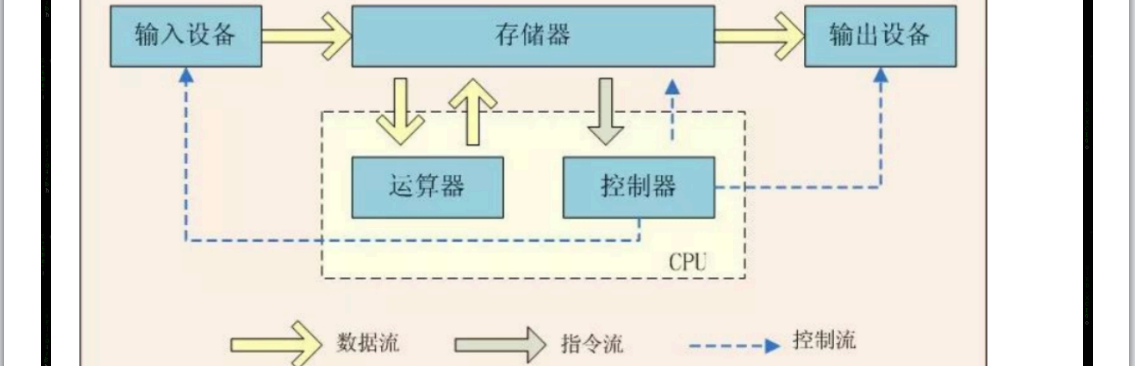

六、冯诺依曼模型

1、四个子系统

- 存储器:用来存储数据和程序的区域

- 算数逻辑单元(ALU):用来进行计算(算数运算、逻辑运算、位运算等)的地方

- 控制单元:对存储器、算数逻辑单元、输入/输出等子系统进行控制操作

- 输入/输出单元:输入子系统负责从计算机外部接收输入数据,输出子系统负责将计算机处理结果输出到计算机外部

2、计算机组成部件

- 可以分为三大类:中央处理单元(CPU)、主存储器(内存)、输入/输出子系统

- CPU 用于数据的运算:算数逻辑单元(ALU)、控制单元(PC 程序计数器,IP 地址寄存器)、寄存器组

- 算数逻辑单元:对数据进行逻辑、移位和算数运算

(一)算术运算:整数和浮点数的加减运算

(二)位移运算:逻辑移位运算和算术移位运算

(三)逻辑运算:非、与、或、异或,这些运算的输入数据为二进制模式,运算结果也是二进制模式

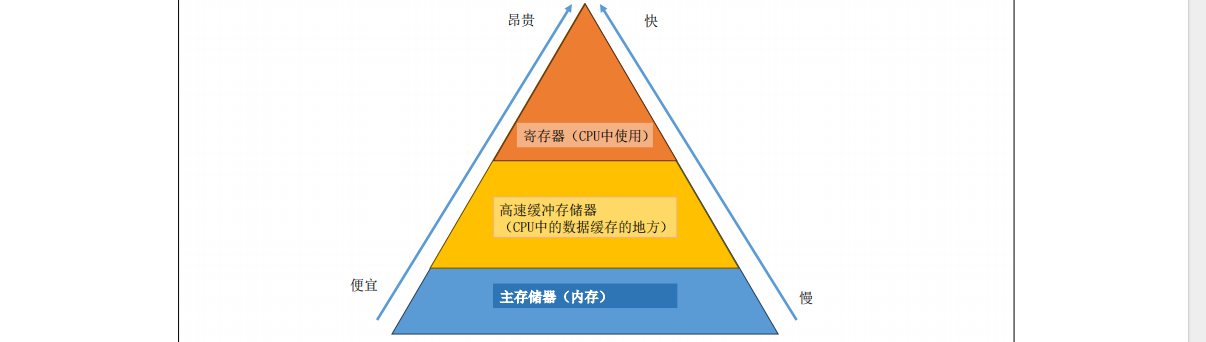

- 寄存器:用来存放临时数据的高速独立存储单元

(一)数据存储寄存器:保存运算的中间结果

(二)指令存储器(IR):CPU 从内存中逐条取出指令,并存储在指令存储器中,解释并执行指令

(三)程序计数器(PC):保存当前正在执行的指令地址,当前指令执行完成后,计数器自动加 1,指向下一条指令的内存地址

- 控制单元:控制各个子系统的操作,控制是通过从控制单元到其他子系统的信号来进行的

- 内存:存储单元的集合,每个存储单元都有唯一的标识,称为地址(数据以“字”的形式在内存中传入传出,字可以是 8 位、16 位、32 位、64 位)

- 内存类型

(一)随机存取存储器(RAM) > 特点:系统断电后,信息(程序或数据)丢失

(二)只读存储器(ROM):里面的数据由制造商写进去,用户只能读不能写 > 特点:系统断电数据不会丢失。常用来存储那些在开机时运行的程序

- 高速缓冲存储器:存储数据的速度比内存快,比寄存器慢。通常容量较小,被置于 CPU 和主存储器(内存之间)

- CPU 与主存储器之间的连接:通常由称为总线的三组线路进行连接:数据总线、地址总线、控制总线

(一)数据总线:由多根线组成,每根线每次传送 1 个位的数据。线的数量取决于计算机字的大小。例如:计算机的字是 32 位(4 个字节),那么需要 32 根线的数据总线,以便同一时刻同时传送 32 位的数据

(二)地址总线:允许访问存储器中的某个字的。地址总线的线数取决于存储空间的大小。例如:存储器的容量为 2 的 n 次方个字,那么地址总线一次需要传送 n 位的地址数据,因此需要 n 根线

(三)控制总线:负责传送指令的。例如:如果计算机有 2 的 m 次方条控制命令,那么控制总线就需要有 m 根

3、输入输出

- 输入/输出设备不能直接与 CPU 和内存的总线相连接,输入/输出设备都是磁性或光学设备,而 CPU 和内存是电子设备

- 输入/输出控制器:连接输入/输出设备到总线上,中介,提升读取速度

- I/O 设备的连接控制器:控制器清除了输入/输出设备与 CPU 以及内存在本质上的障碍,控制器可以是串行或并行的设备

(一)串行控制器:只有一根数据线连接在设备上

(二)并行控制器:有多根数据线连接到设备上,一次能同时传送多个位

- 常用控制器:SCSI、火线、USB 和 HDMI

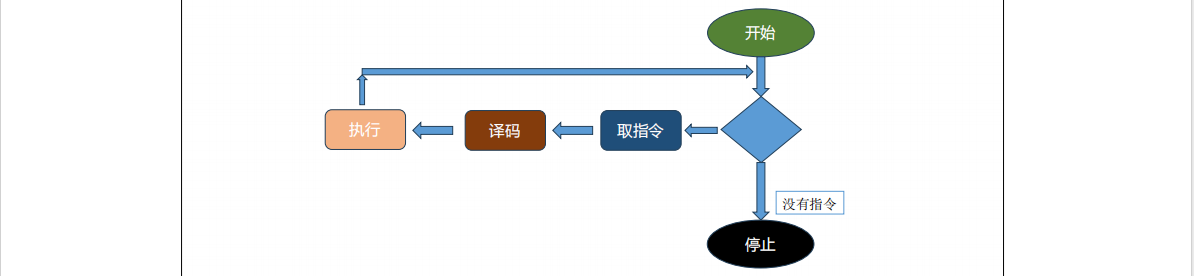

4、程序执行:机器周期(重复的机器周期:取指令->译码->执行)

- 取指令:CPU 从内存中取出下一条要执行的指令

- 译码:CPU 对取出的指令进行解码,确定指令的类型和操作数

- 执行:CPU 根据译码结果执行相应的操作,如算数运算、数据传输等,并可能更新 CPU 内部的状态或内存中的数据

5、不同体系结构

- CISC(复杂指令集计算机):指令集大而复杂,单条指令可完成多个操作

- RISC(精简指令集计算机):指令集精简,每条指令功能单一,易于并行处理

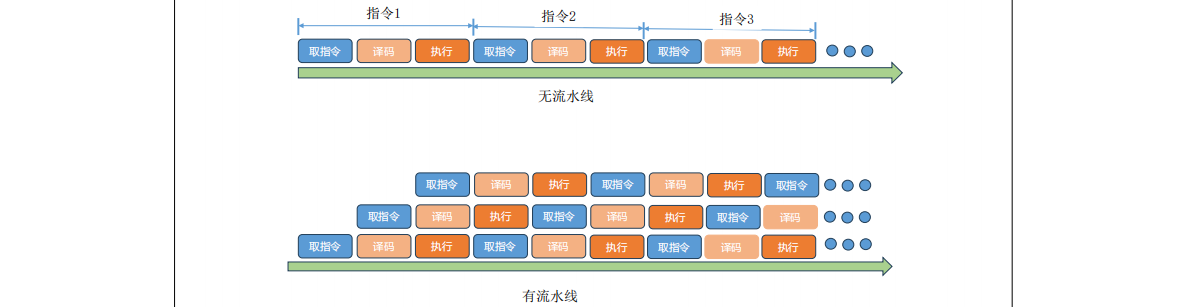

- 流水线:将指令执行分解为多个阶段,并行处理不同指令的不同阶段以提高效率

6、简单计算机

- 一般由三部分组成:CPU、存储器、输入/输出(I/O)系统

七、设计计算机硬件

1、实现一个 ALU

- 记得背诵第三点,第 7 点存储

2、理解部分

- 注意理解地址位数(二进制位数)

- 故八位地址就是三位地址位数,000,001,010,011,100,101,110,111(0-7)

- 隧道中蓝色的点是输入,黄色的点是输出(注意分辨)

绝缘基材层,铜箔层,丝印层,阻焊层

2156

2156

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?