目录

一、设计要求

L A B : V r e f = 1.2 o r 0.8 , ∂ V r e f ∂ T ∣ T = 60 ° = 0 , I D 4 = 10 u LAB :V_{ref} = 1.2 \,or\,0.8 ,\frac{\partial V_{ref}}{\partial T} \small \mid T=60°=0,I_{D4} = 10u LAB:Vref=1.2or0.8,∂T∂Vref∣T=60°=0,ID4=10u

二、原理图分析

∣

I

D

4

∣

=

V

T

ln

n

R

1

+

∣

V

B

E

1

∣

R

2

=

1

R

2

(

∣

V

B

E

1

∣

+

R

2

R

1

V

T

ln

n

)

\begin{aligned}\left|I_{D 4}\right| & =\frac{V_{T} \ln n}{R_{1}}+\frac{\left|V_{B E 1}\right|}{R_{2}} \\& =\frac{1}{R_{2}}\left(\left|V_{B E 1}\right|+\frac{R_{2}}{R_{1}} V_{T} \ln n\right)\end{aligned}

∣ID4∣=R1VTlnn+R2∣VBE1∣=R21(∣VBE1∣+R1R2VTlnn)

V

B

G

=

R

4

R

2

(

∣

V

B

E

1

∣

+

R

2

R

1

V

T

ln

n

)

V_{B G}=\frac{R_{4}}{R_{2}}\left(\left|V_{B E 1}\right|+\frac{R_{2}}{R_{1}} V_{T} \ln n\right)

VBG=R2R4(∣VBE1∣+R1R2VTlnn)

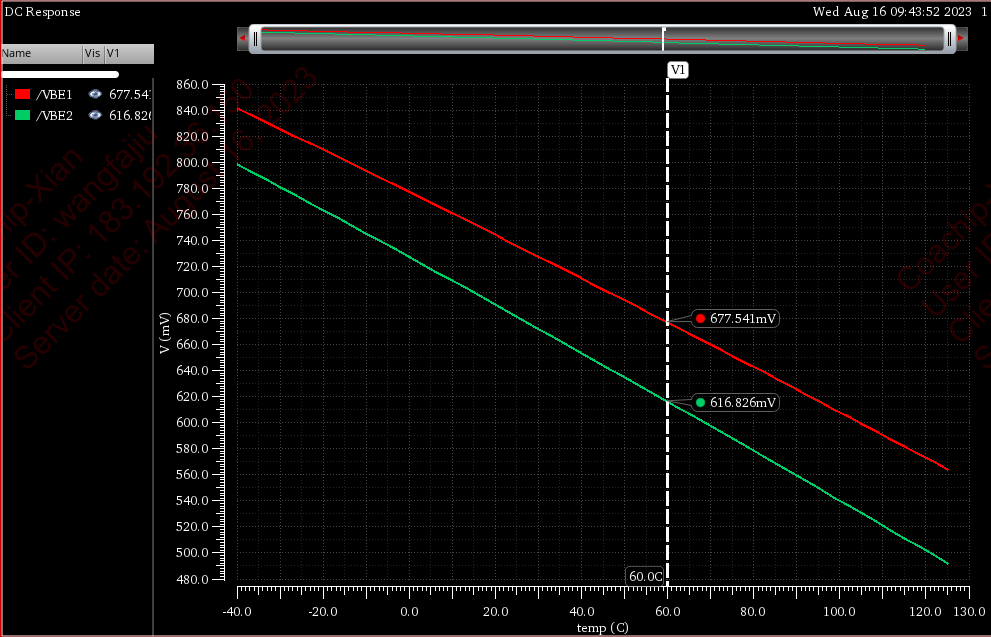

三、三极管温度特性

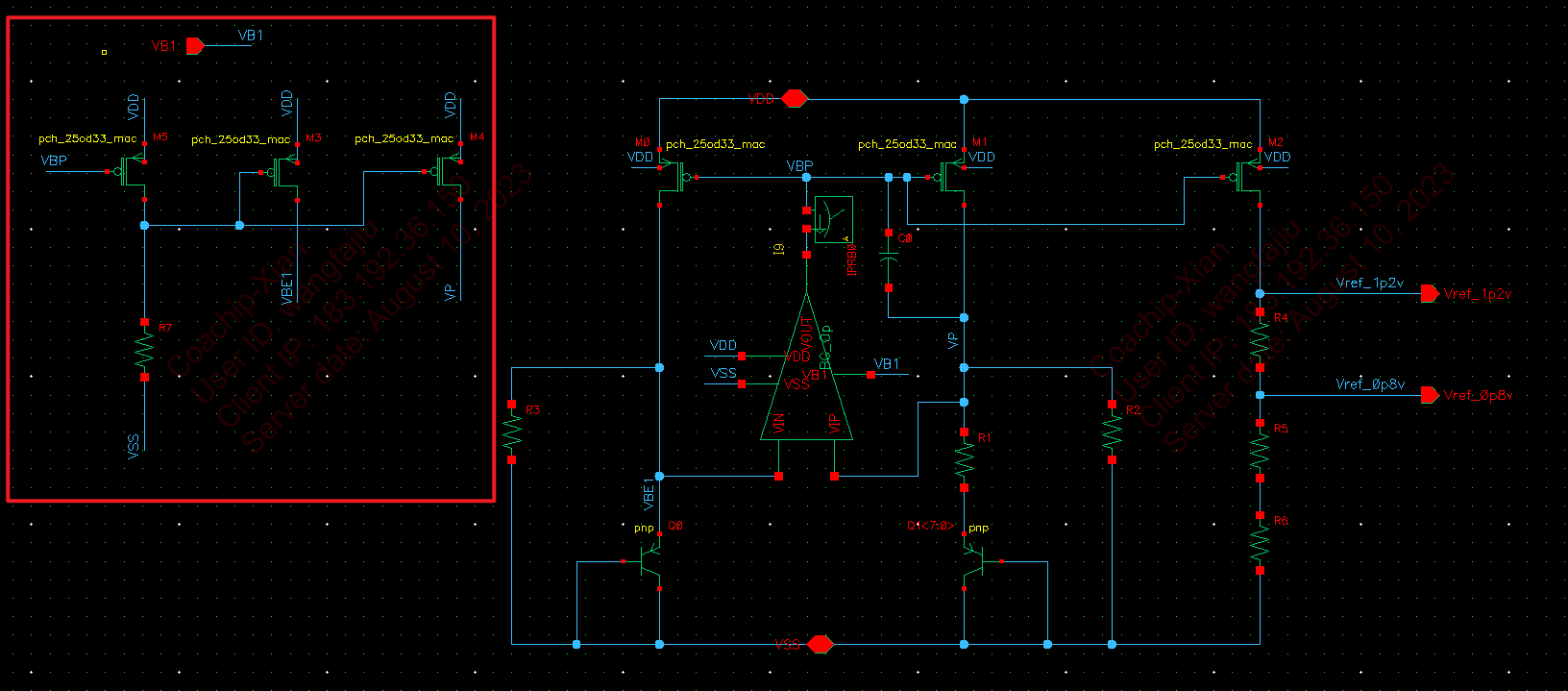

1. 电路图

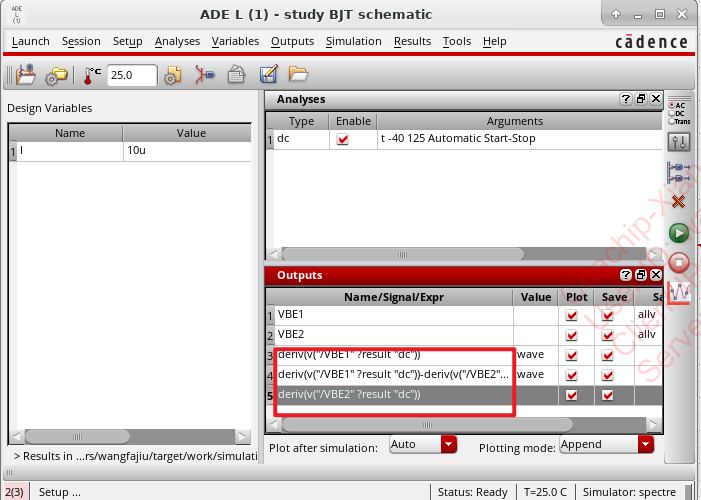

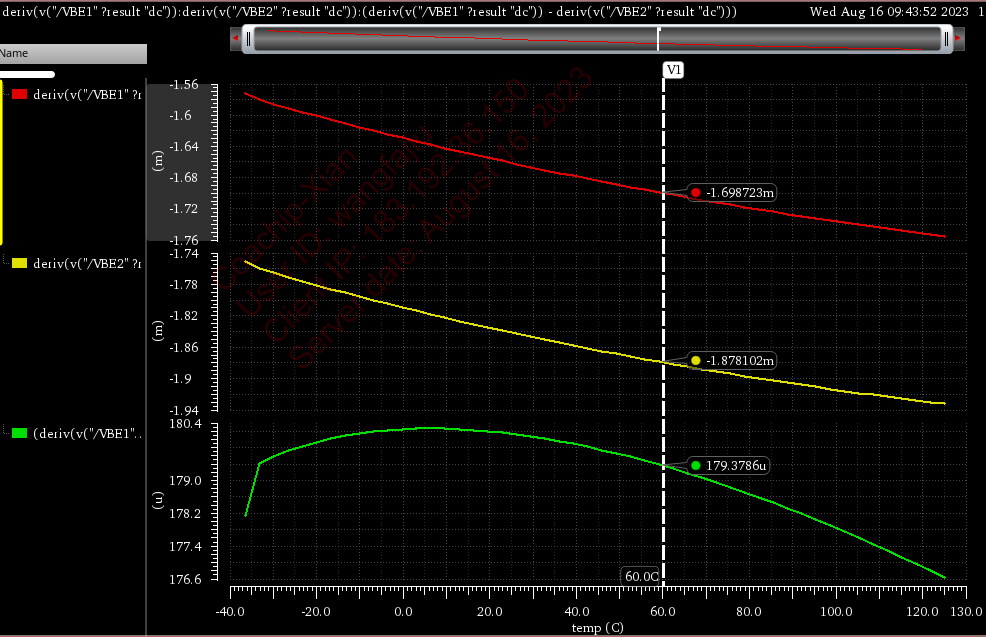

2. 仿真 ∂VBE1,∂VBE2,∂ΔVBE

运用 deriv 函数 添加 VBE1 ,VBE2 的斜率到输出,再添加 ΔVBE 的斜率

∂VBE1 肯定比 ∂VBE2 要大,这样 ∂ΔVBE 才会为正

三、计算电阻值

用 (1) 可以算出 R1 / R3 = 9.47(使左边为 0 达到 0 温度系数)

∂

V

out

∂

T

=

∂

V

B

E

1

∂

T

+

(

k

q

ln

n

)

R

1

R

3

(

1

)

=

∂

V

B

E

2

∂

T

+

(

k

q

ln

n

)

(

1

+

R

1

R

3

)

\begin{aligned}\frac{\partial V_{\text {out }}}{\partial T} & =\frac{\partial V_{B E 1}}{\partial T}+\left(\frac{k}{q} \ln n\right) \frac{R_{1}}{R_{3}} \,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,(1)\\& =\frac{\partial V_{B E 2}}{\partial T}+\left(\frac{k}{q} \ln n\right)\left(1+\frac{R_{1}}{R_{3}}\right)\end{aligned}\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,

∂T∂Vout =∂T∂VBE1+(qklnn)R3R1(1)=∂T∂VBE2+(qklnn)(1+R3R1)

上面求得

∂

V

B

E

1

∂

T

∣

T

=

60

°

=

−

1.7

m

V

/

°

C

,

∂

V

B

E

∂

T

∣

T

=

60

°

=

179

u

V

/

°

C

\frac{\partial V_{BE1}}{\partial T} |_{T=60°} = -1.7mV/°C,\frac{\partial V_{BE}}{\partial T} |_{T=60°} = 179uV/°C

∂T∂VBE1∣T=60°=−1.7mV/°C,∂T∂VBE∣T=60°=179uV/°C

当 R1 / R3 = 9.47 温度系数为 0,对应现在电路图 R2 / R1 = 9.47

V

B

E

=

0.7

V

,

V

T

=

26

m

V

,

l

n

8

=

2.1

V

I

D

4

=

1

R

2

(

0.736

V

+

9.47

×

54.65

m

V

)

=

10

u

⟹

R

2

=

124.8

K

⟹

R

1

=

13.18

K

V_{BE} = 0.7\,V,V_T = 26\,mV,ln8=2.1V \\I_{D4}=\frac{1}{R_2}\left(0.736V+9.47\times 54.65mV \right)=10u \\\Longrightarrow R_2 = 124.8K \\\Longrightarrow R1= 13.18K

VBE=0.7V,VT=26mV,ln8=2.1VID4=R21(0.736V+9.47×54.65mV)=10u⟹R2=124.8K⟹R1=13.18K

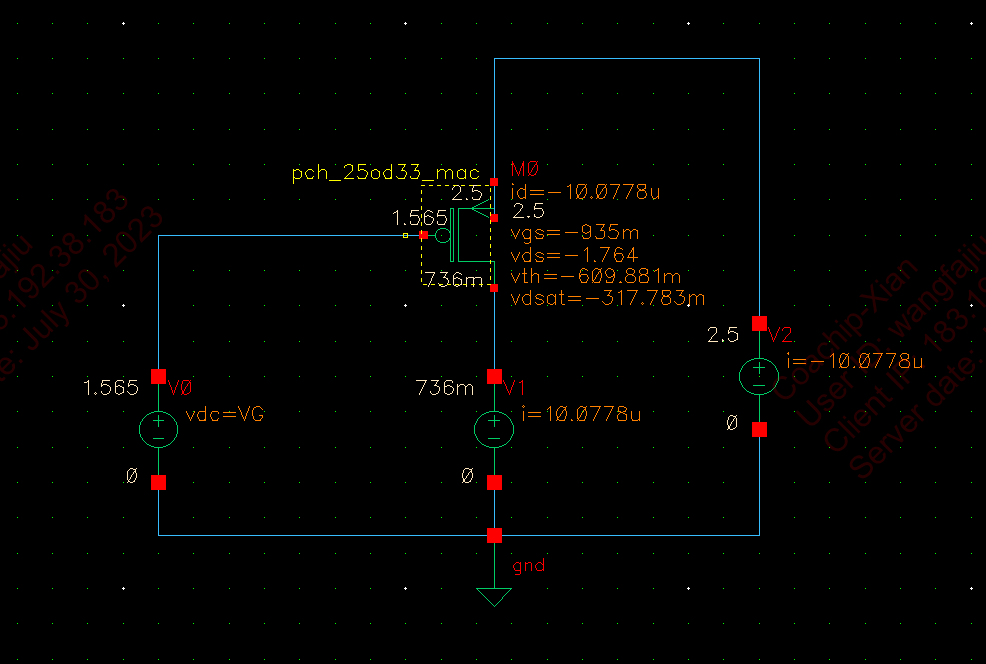

四、扫描MOS曲线

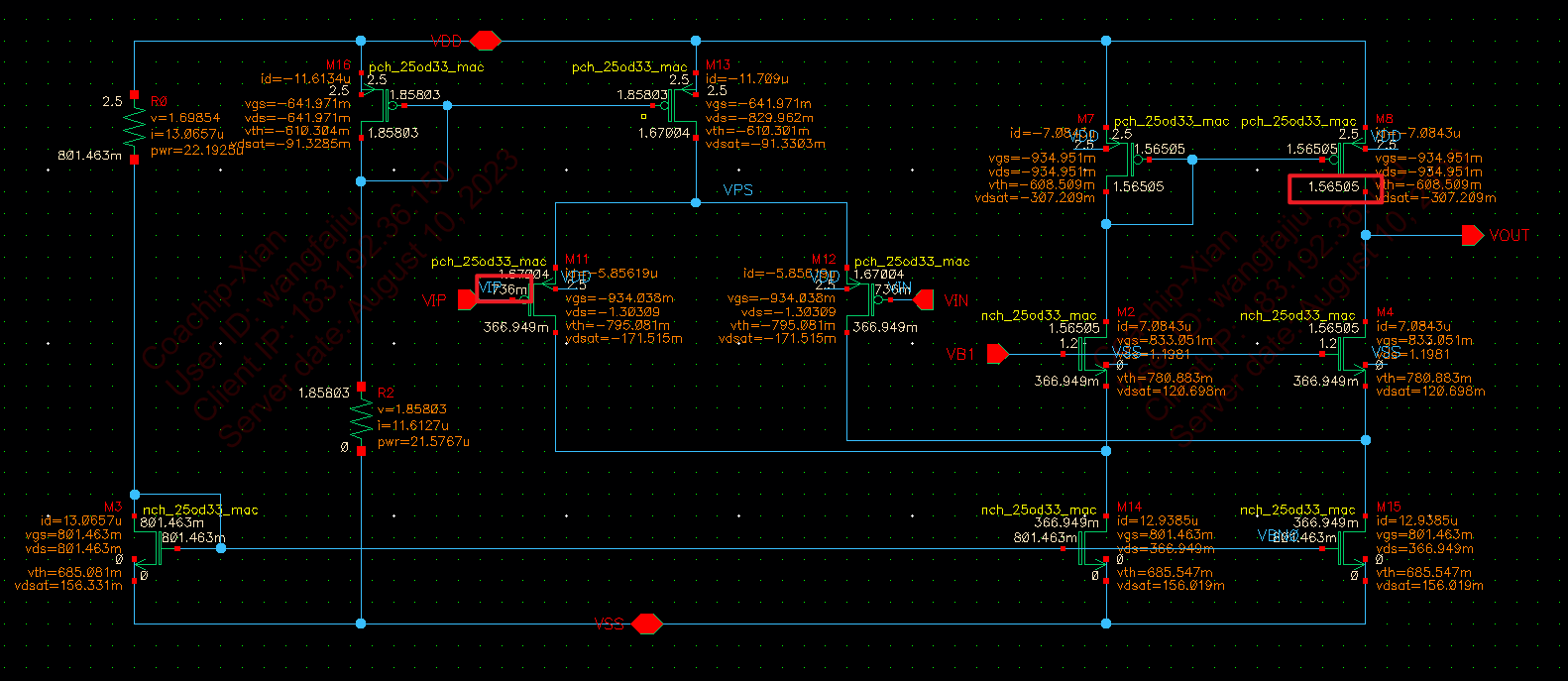

从三极管的温度曲线仿真得 VEB1 = 0.736V ,即输入共模电平为 0.736V,输出可以通过MOS管仿真得到为 1.565V

五、OP 设计

V i n = 0.736 V , V D D = 2.5 V , V O U T = 1.565 V , A V = 60 d B 左右 V_{in} = 0.736V ,V_{DD} = 2.5 V,V_{OUT} = 1.565V,A_{V}=60 dB左右 Vin=0.736V,VDD=2.5V,VOUT=1.565V,AV=60dB左右

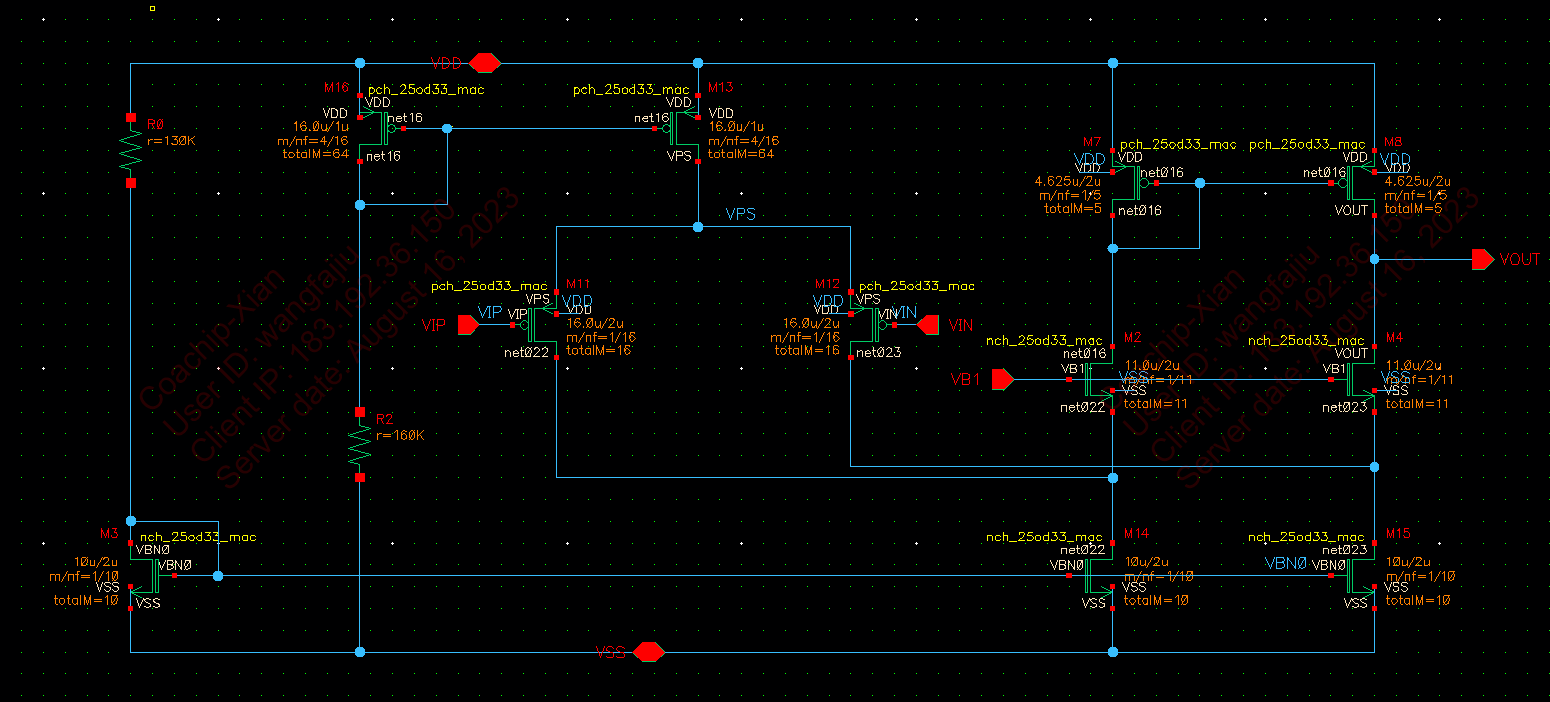

1. OP电路图

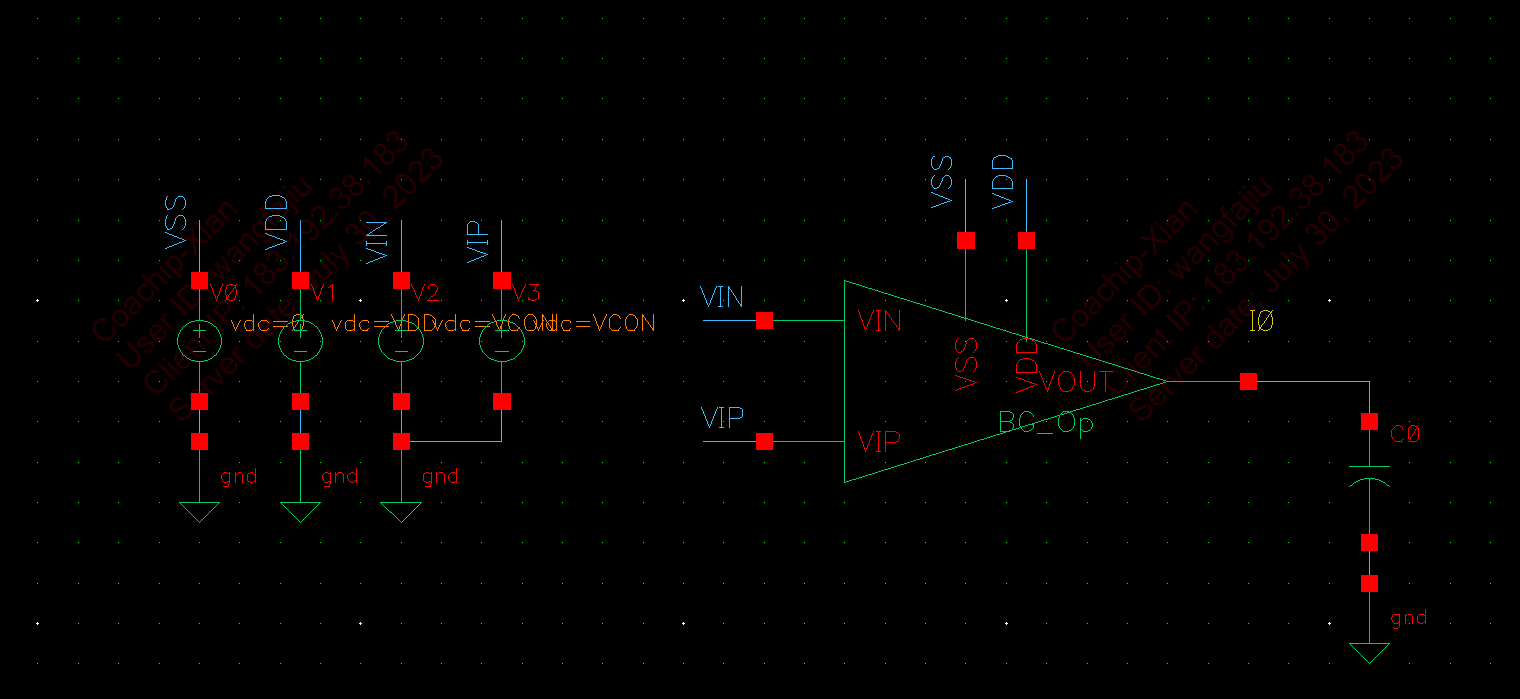

2. 测试电路

3. op直流仿真

六、添加OP去BG电路

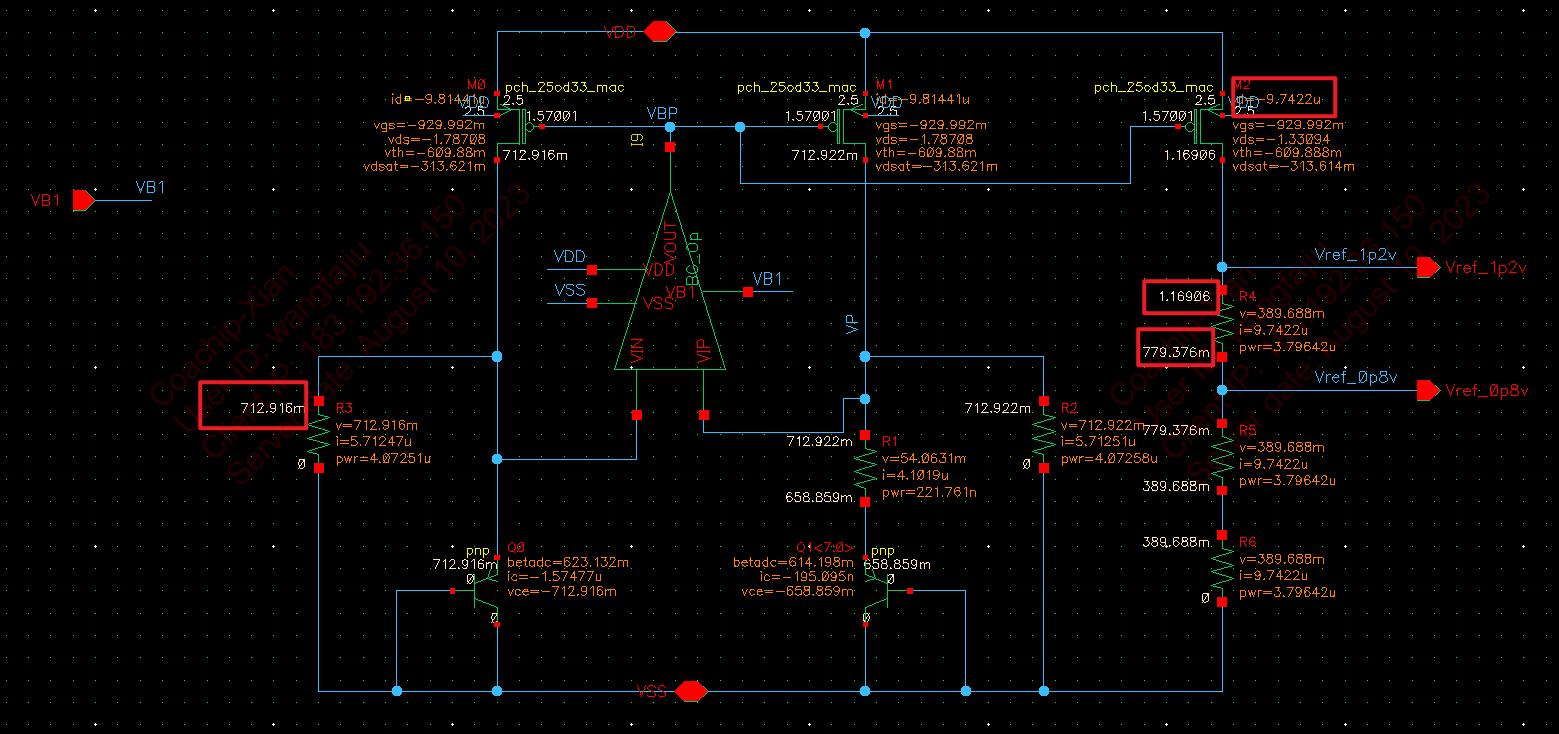

1. BG直流仿真

VBE的值没有达到我们的预期736mV,OP的输出也增大一点

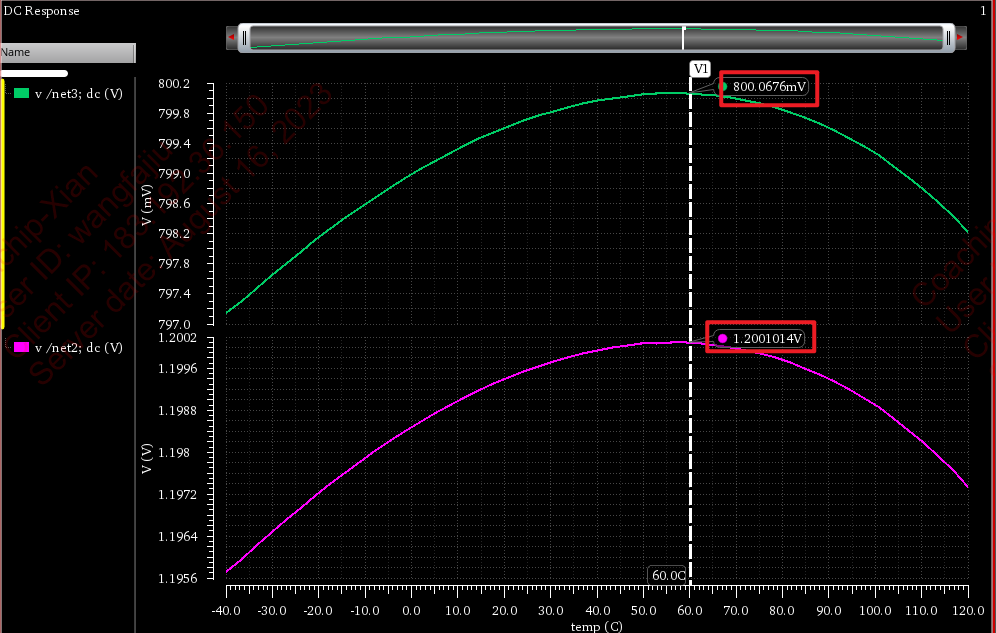

2. 查看温度曲线

3. 调节温度系数和电流

调节 R2 与 R1 可以调节温度特性,也可以调节电流大小,减少R2提高电流,R3相应比例变化

R3 = R4 = 121.55K ,R2 = 12.855K

七、仿真

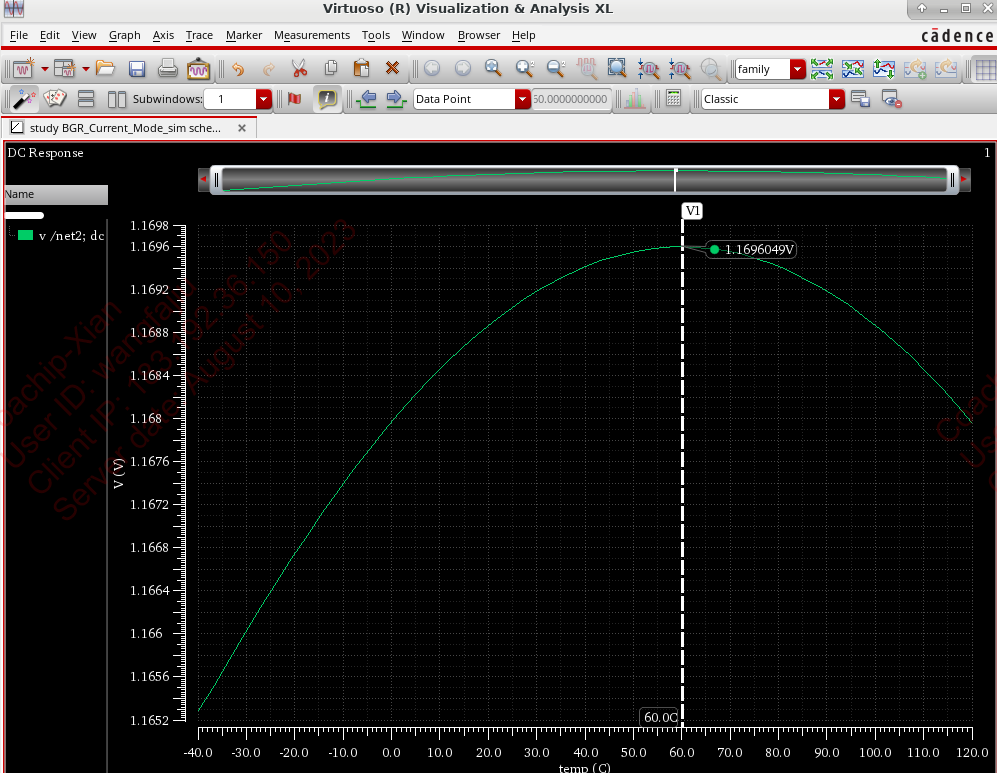

1. 直流仿真

在60°电压将不受温度影响

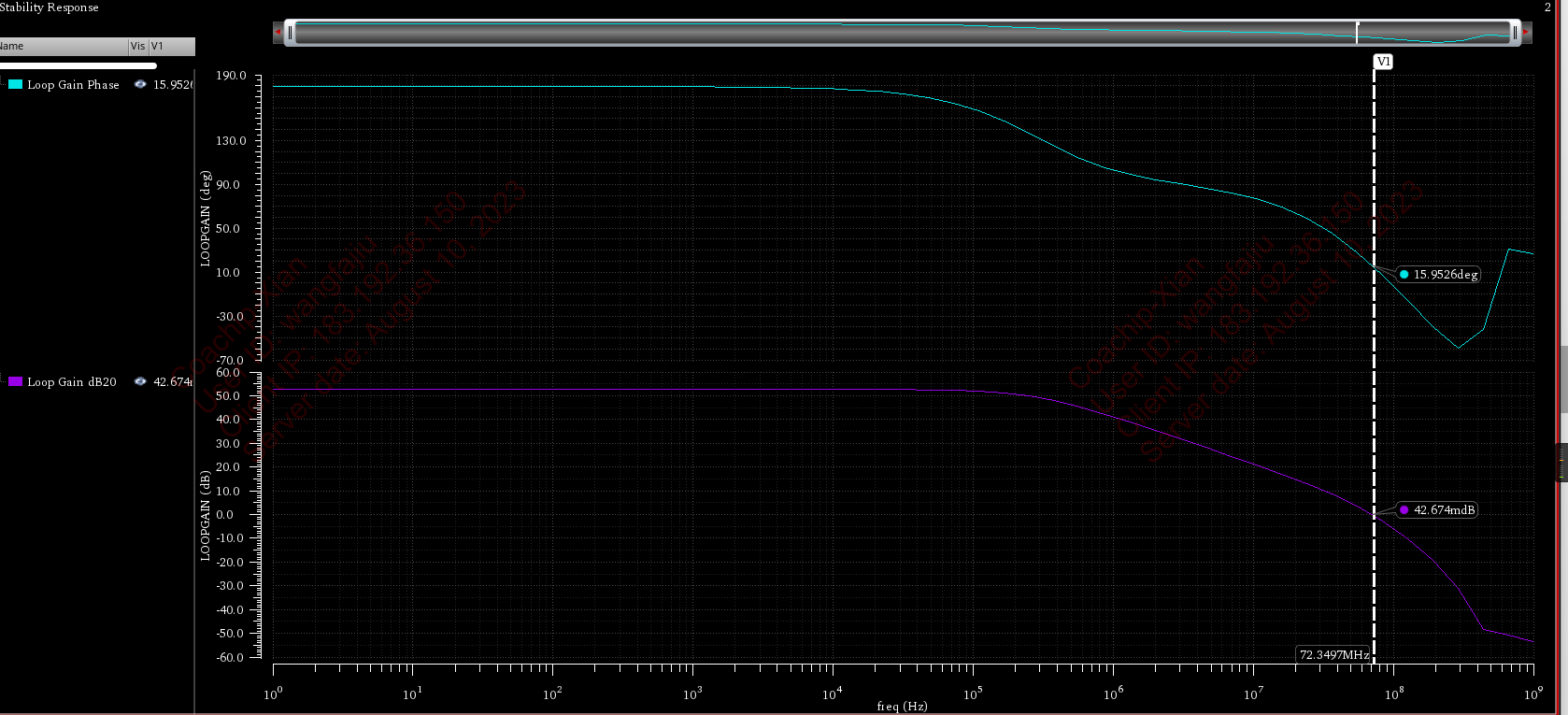

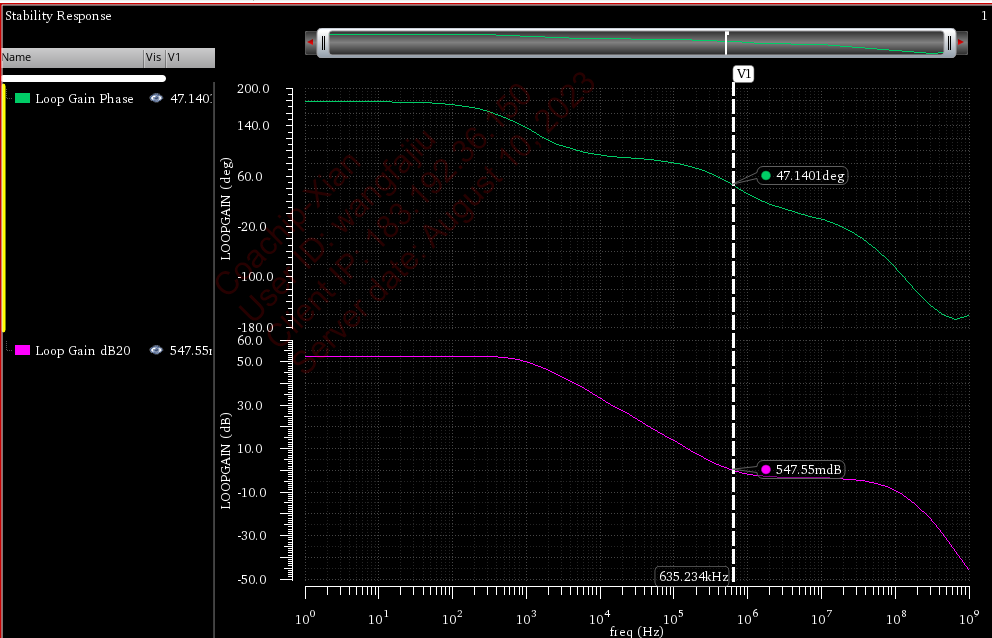

2. 稳定性仿真

相位裕度太低了,加一个补偿电容,米勒补偿效果并不是很好,其实调节gm1更加有效,可以使得第二极点变大

3. 添加启动电路

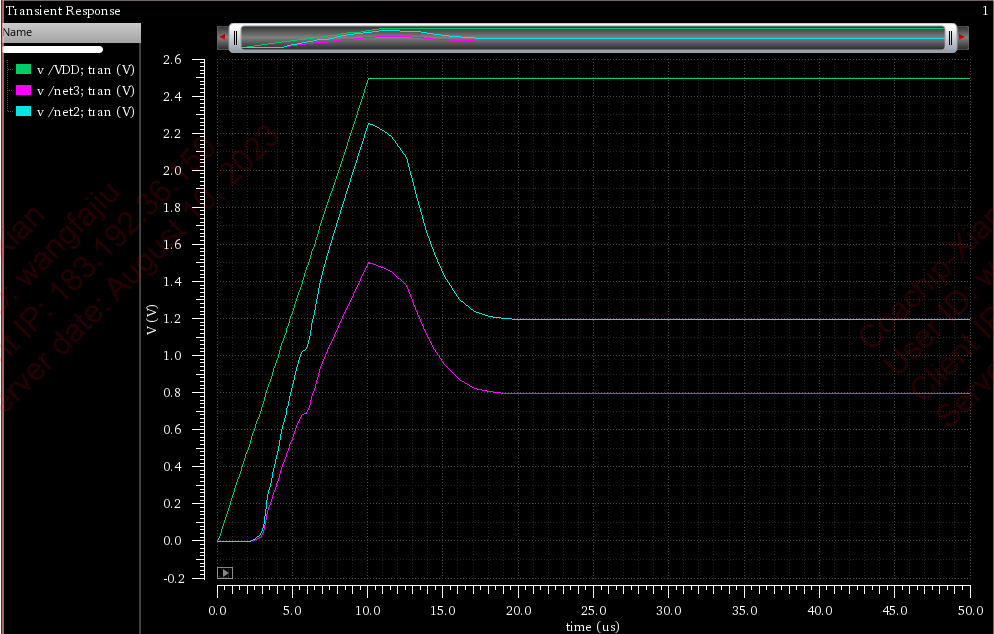

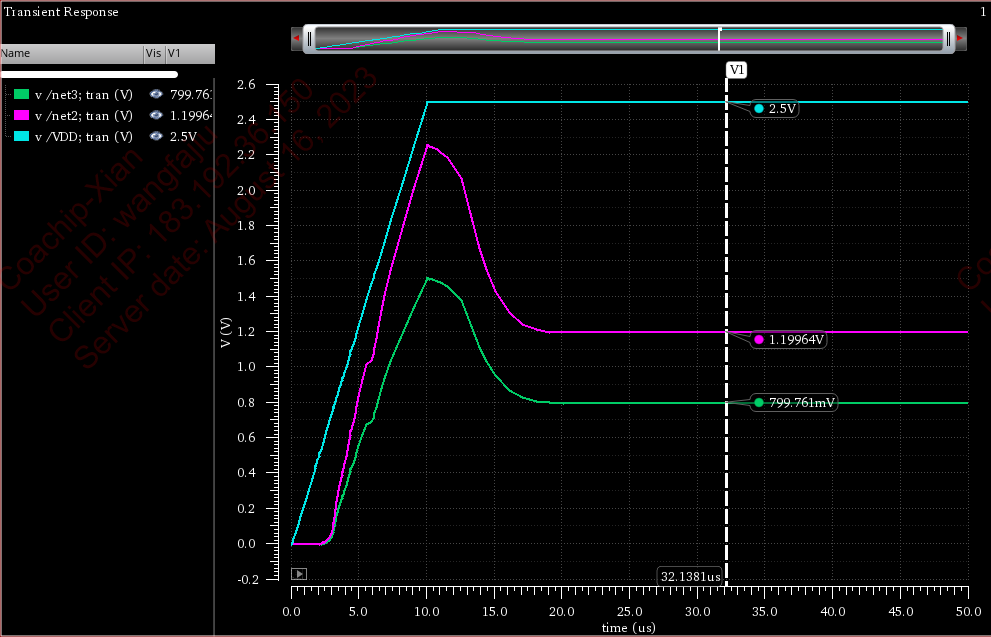

4. 上电仿真

七、总结

这个只是简单的进行了设计,有很多地方有待优化,放大器的增益与相位裕度,偏置电路,启动电路都有待优化。

469

469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?