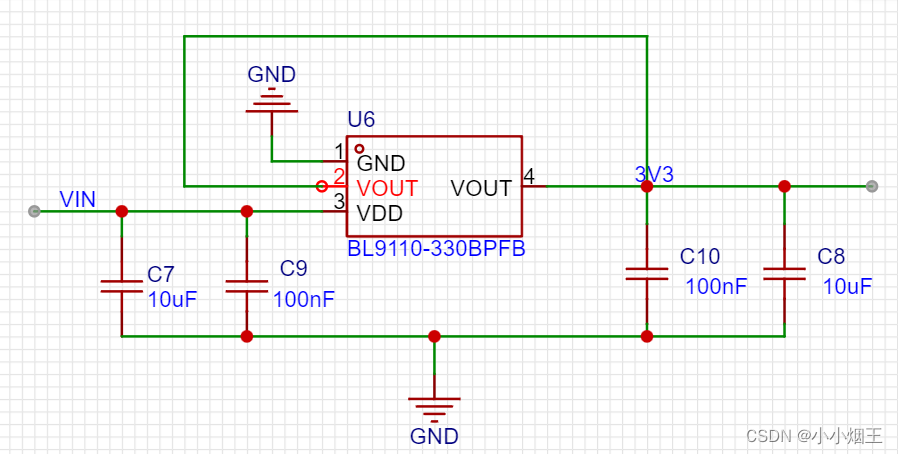

在设计原理图的时候会看到并联的旁路电容,有时是双电容(一大一小),有时是三电容(三个小),例如下图中的一个10uF和一个0.1uF:

在查阅资料的时候看到的解释通常是:芯片供电需要稳定,但是实际电路中会有干扰,10uF滤除低频干扰信号,0.1uF滤除高频干扰信号,二者并联提高滤波的带宽和效果。

但是根据我们学习的理论知识,电容的阻抗是:

电容的阻抗是和容值C成反比的,那10uF的对高频干扰信号的阻抗应该低于0.1uF,那为什么需要一个小电容去滤除高干扰呢?

是因为实际电容模型的问题:实际的电容其实并非只有电容,其更准确的等效模型如下:

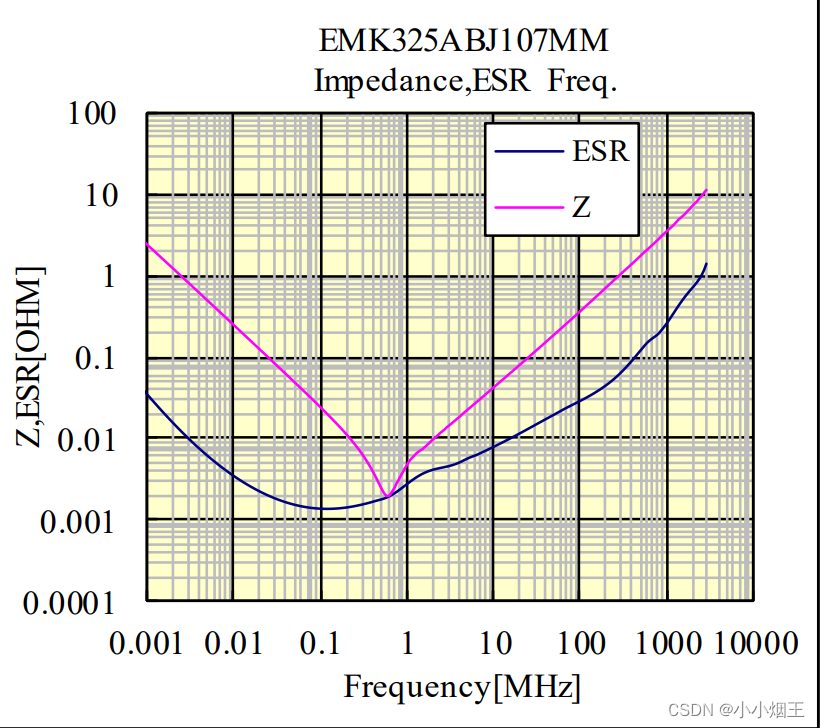

模型中的电感和电阻是由于电容的制造工艺而引入的,无法去除,所以导致实际电容的阻抗曲线是由电容区和电感区组成的,这里以Taiyo Yuden的EMK325ABJ107MM电容为例,打开其数据手册可以看到他的阻抗曲线如下:

可以看到在谐振频率左侧,阻抗呈容性的;在谐振频率右侧,阻抗呈感性,而谐振频率是随着C的增大而减小,也就是说10uF电容的谐振频率是要低于0.1uF的,所以在0.1uF的工作频段,10uF是呈感性的,并不能起到滤波的效果。

记录一下,欢迎批评指正!

文章讨论了在电路设计中并联电容,特别是大小电容并联用于滤波的原因。尽管大电容如10uF对低频干扰有良好过滤效果,但由于实际电容的等效模型包含电感和电阻,其在高频段可能呈现感性,无法有效滤除高频干扰。因此,0.1uF的小电容用于滤除高频干扰,两者结合可以提升滤波性能。电容的谐振频率与容值有关,小电容的谐振频率更高,更适合工作在高频段。

文章讨论了在电路设计中并联电容,特别是大小电容并联用于滤波的原因。尽管大电容如10uF对低频干扰有良好过滤效果,但由于实际电容的等效模型包含电感和电阻,其在高频段可能呈现感性,无法有效滤除高频干扰。因此,0.1uF的小电容用于滤除高频干扰,两者结合可以提升滤波性能。电容的谐振频率与容值有关,小电容的谐振频率更高,更适合工作在高频段。

404

404

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?