目录

在数字电路中,通常将信号通过电阻连接到电源定义为上拉,将通过电阻连接到地为下拉。

如果我们想要引入多个变量时,上拉和下拉的互补关系不能变,即为希望采用互补的关系,当上拉关闭时,下拉应该打开,反之亦然。

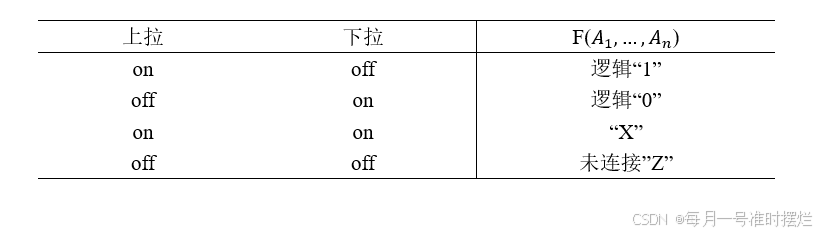

在电路中,上拉和下拉导通或者截止时有不同的情况,如下所示:

在上图中on表示导通,off表示截止。当上拉和下拉都截止时,处于未连接状态,此时处于高阻态,高阻态意味着物理连接上是连接的,但是呈现出来是断开状态。当上拉和下拉都导通时,是电路中一定会出现的现象,这种状态需要在稳定时避免,稳点电路时上拉和下拉必须是一个导通一个截止。

1 各种逻辑功能的CMOS门电路

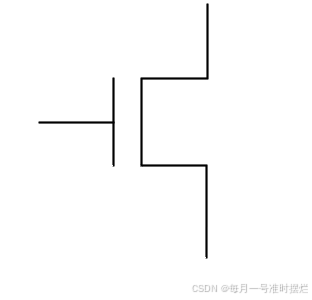

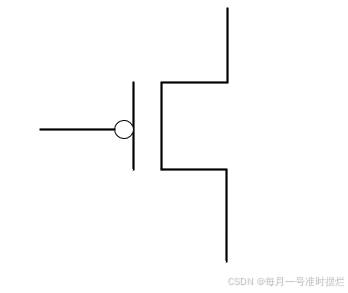

CMOS管中NMOS和PMOS是互补关系,即当NMOS导通时,PMOS管截止;当PMOS导通时,NMOS管截止。

(1)当只有一个变量时,栅源电压()为高电平时,NMOS管导通,PMOS管截止:

当栅源电压()为低电平时,NMOS管截止,PMOS管导通:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2734

2734

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?