针对上一篇复位中出现的一些相关概念进行补充,作为了解学习。

一、复位恢复时间和复位解除时间

复位恢复时间(reset recovery time)

复位恢复时间: 解除复位信号时,复位边沿(当从有效变成无效的跳变时刻,通常是0->1那个时间点)与下一个有效时钟沿之间的这段时间(最小间隔)。对应建立时间

复位解除时间: 解除复位信号时,复位边沿与上一个有效时钟沿之间的这段时间(最小间隔)。对应保持时间

异步复位的复位信号必须满足一定的恢复时间和解除时间,否则没法确定时钟沿是否起作用了,即判断不了时钟沿到时是复位了还是没复位。D触发器如果不复位,那么输出就是输入的数据。

1)不满足复位恢复时间或者撤离时间,可能会导致亚稳态问题。(注意是可能)因为如果输出本身就是复位后的值,即使当前时钟沿不能判断是否复位,输出也是复位值,这时候就不会产生亚稳态,因为已经是复位态了。

2)不满足复位恢复时间或者撤离时间可能会导致不同FF复位状态不一致的问题。复位信号和时钟信号一样,通过复位网络到达各个触发器。复位网络具有非常大的扇出和负载,到达不同的触发器存在不同的延时,不满足复位恢复或者解除时间的情况下,就有可能在不同的触发器的不同时钟周期内进行解复位。注意,这里的假设条件是复位树和时钟树已经做成立平衡状态,不再考虑复位树和时钟树没做好的情况。

二、复位树

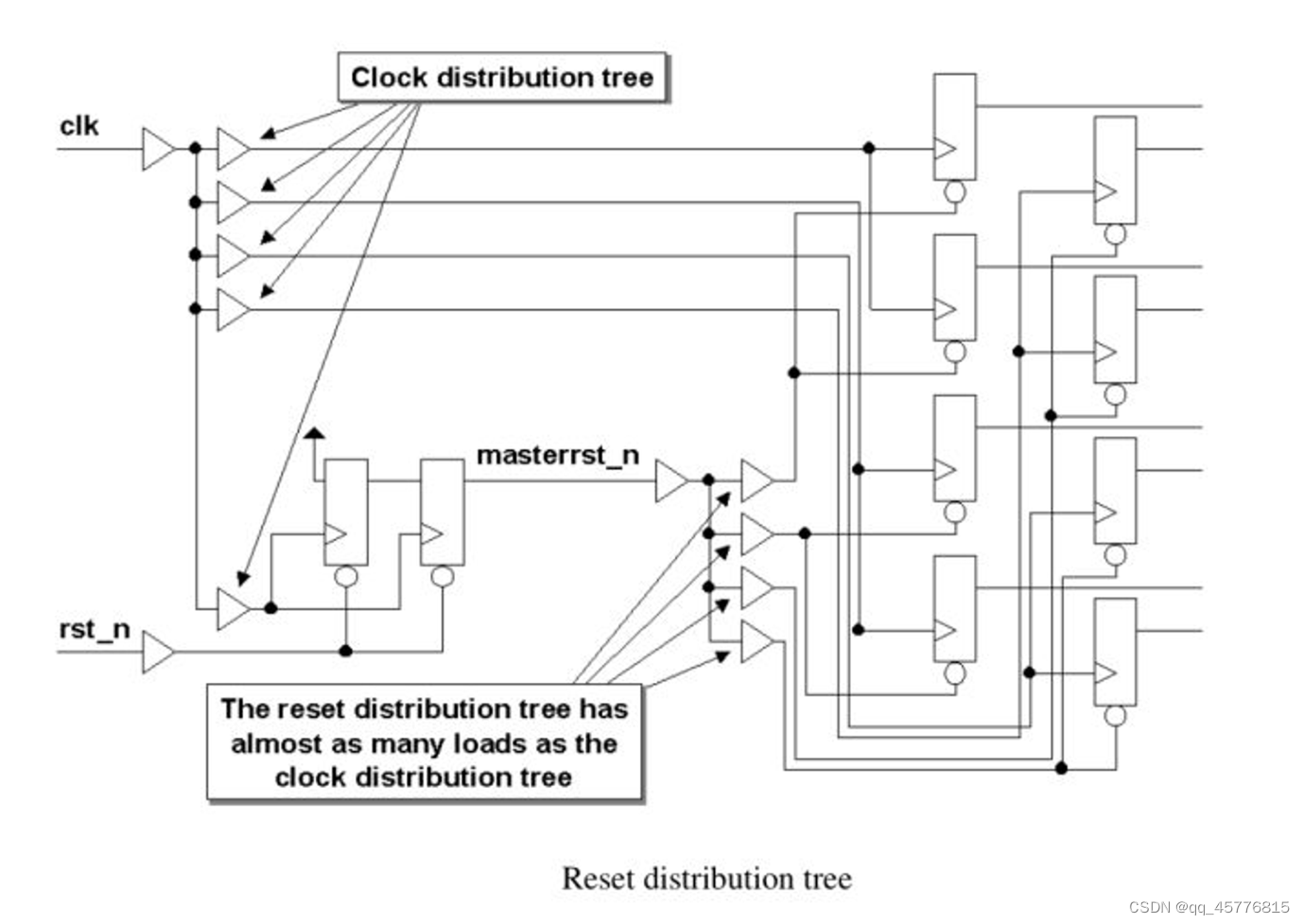

典型复位树:

时钟分布树和重置分布树之间的一个重要区别是时钟树需要紧密平衡分布重置之间的偏差(skew)。与时钟信号不同,只要与复位信号相关的延迟足够短,允许在一个时钟周期内传播所有复位负载,并且仍然满足所有目标寄存器和触发器的恢复时间,那么复位信号之间的偏差(skew)就不是关键。

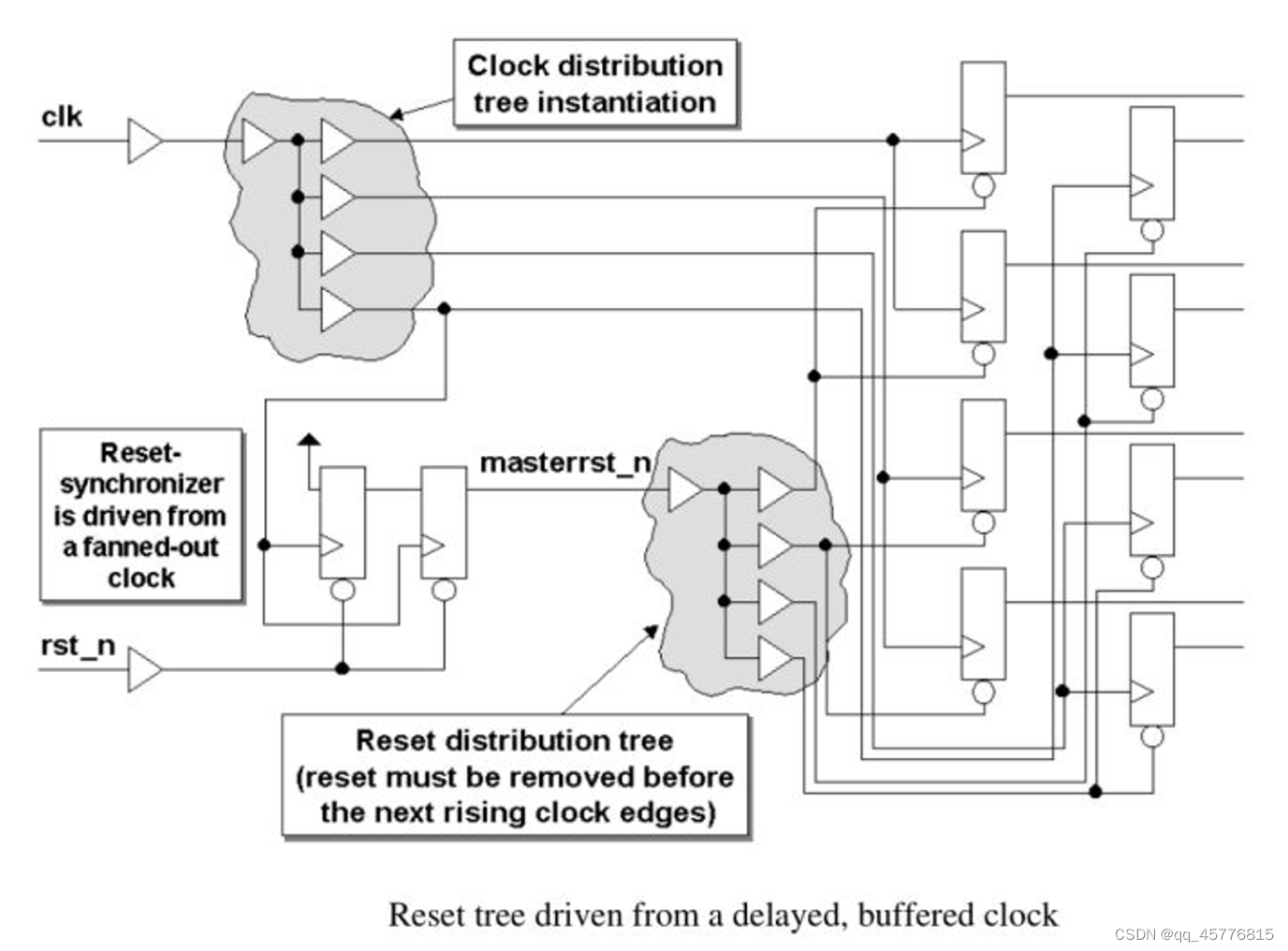

另外一个需要考虑的问题是,时钟树和复位树之间的关系。到底用哪个时钟来驱动复位树的FF呢?如果能够用分支clock来驱动master reset的FF那最好了,但是在大多数情况下,没有足够的时间让时钟脉冲遍历时钟树、时钟复位驱动触发器,然后让复位遍历复位树,所有这些都在一个时钟周期内完成。这种情况如下图所示:

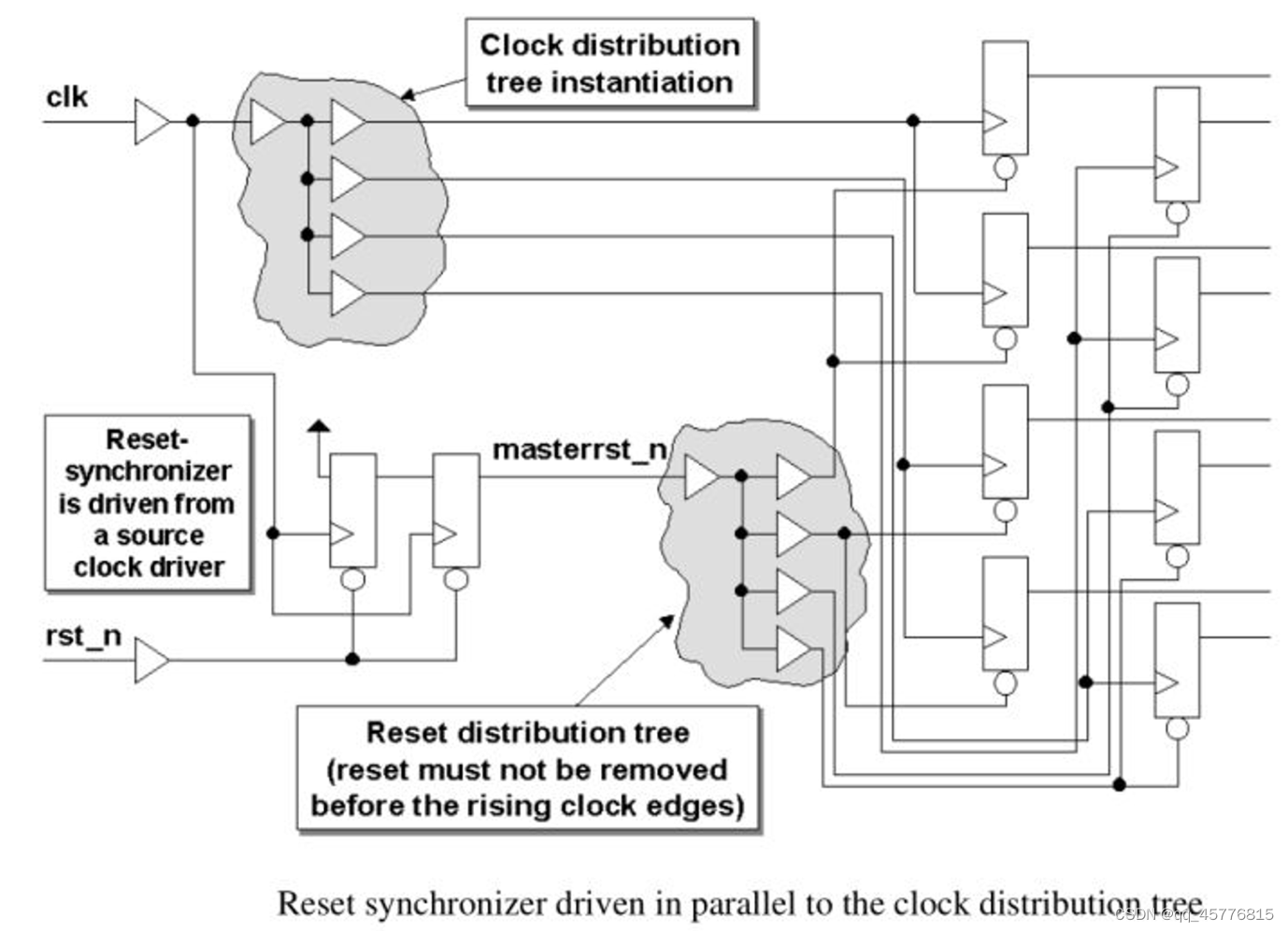

为了能让reset到达所有逻辑的速度更快,更好的方式是用一个更早的clock来驱动reset FF,即用源时钟来驱动。必须进行Post layout timing分析,以保证复位同步器的FF不会出现setup/hold违例。通常情况下,两个tree之间详细的时序调整必须等到 layout完成才能进行。电路结构如下图所示:

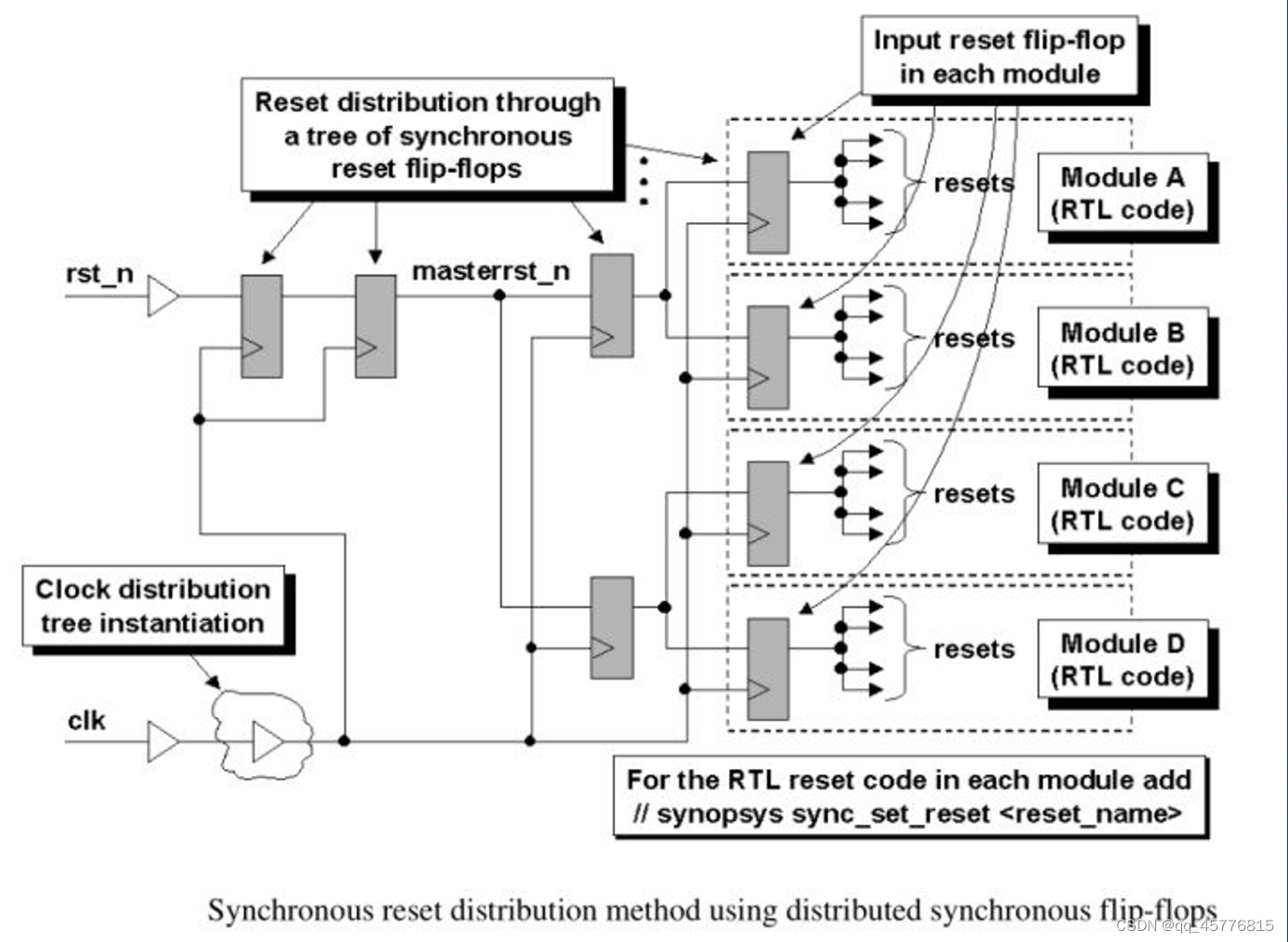

2.1 同步复位树

对同步复位,一种技术是通过插入FF来实现复位树。这样reset不需要在一个时钟周期内到达所有的FF,但是需要几个时钟才能把整个设计复位掉。每个模块都需要包含如下代码:

input reset_raw;

// synopsys sync_set_reset "reset"

always @(posedge clk)

reset <= reset _raw;

同步复位时钟树如下所示:

采用这种技术,同步复位信号可以像其他数据信号一样处理,设计中每个模块的timing分析都很容易,复位树的每个阶段都有合理的扇出。

2.2 异步复位树

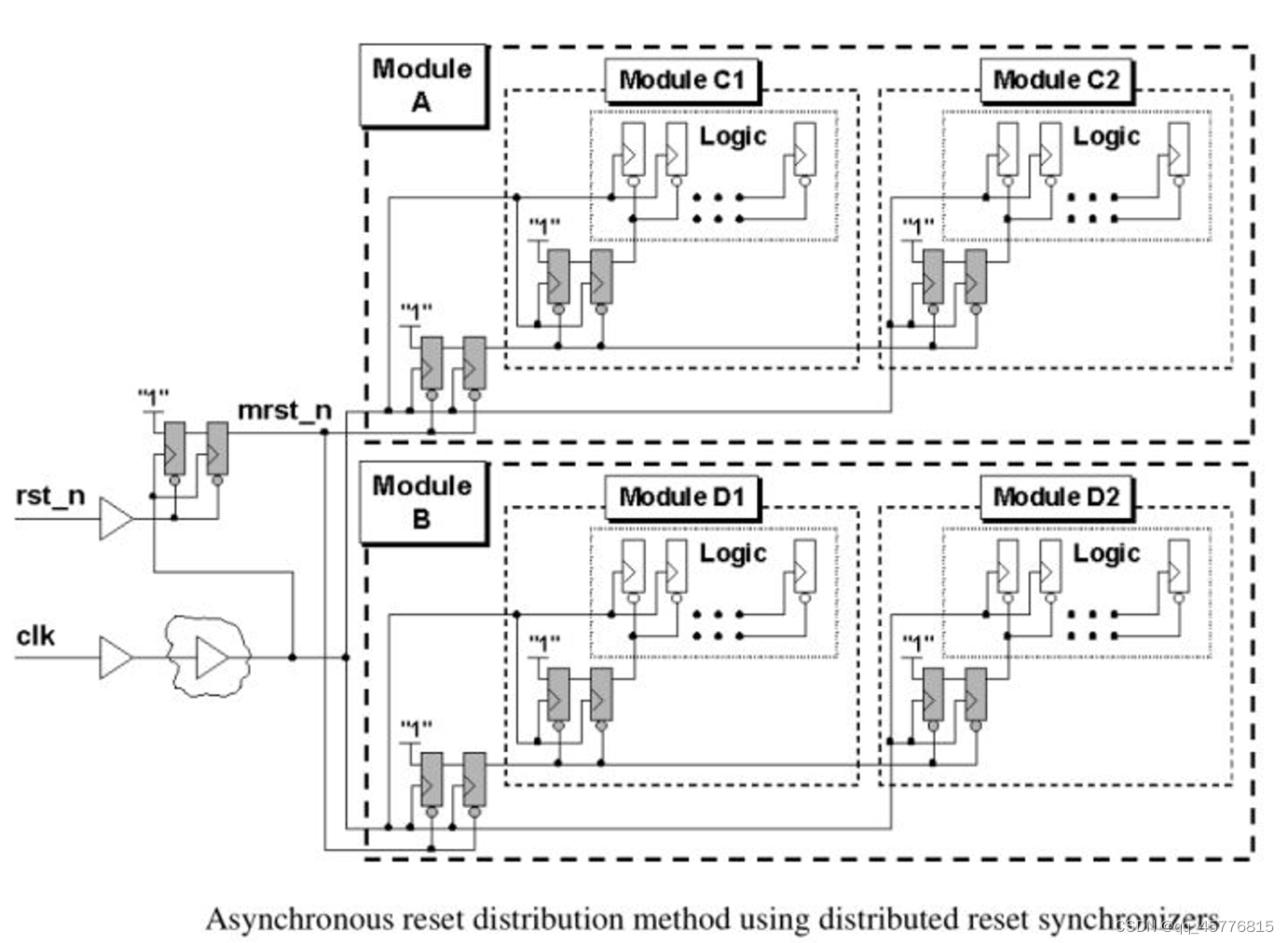

对异步复位,是通过复位同步器来完成复位树的建立。即每个层级都加上一个异步复位同步器。如下图所示:

异步复位树和同步复位树有点相似,但是这里的异步复位同步器是两级的FF。这种异步复位树,复位时可以所有的FF都同时复位,但是解复位必须要几个cycle才能完成。

这种结构的问题就是,不同层级解复位的时间点可能是不一样的。如果设计要求整个芯片在同一个cycle来解复位,那么就需要对复位同步器做平衡设计,保证到达每个复位终点是同一个时钟。同步时钟树也存在这个问题。

使用这种结构的好处是,不用等到P&R之后才去手动调整timing,完全可以交给综合工具(DC/PT)去插入buffer。

在使用异步重置时,至关重要的是,设计人员要在DC和PT中使用设置为适当设置的适当变量,以确保从复位同步触发器的q-output驱动的异步复位得到缓冲(如果需要的话)和timed。DC和PT都可以并且将时间按照本地时钟进行异步复位输入,如果设置了以下变量:

pt_shell> set timing_disable_recovery_removal_checks "false"

dc_shell> enable_recovery_removal_arcs "true"

这些设置应该是Synopsys的默认设置(只要确保它们是环境设置)。正确设置这些标志和使用分布式复位同步器后,就可以不用类似时钟树去构建缓冲复位树了。

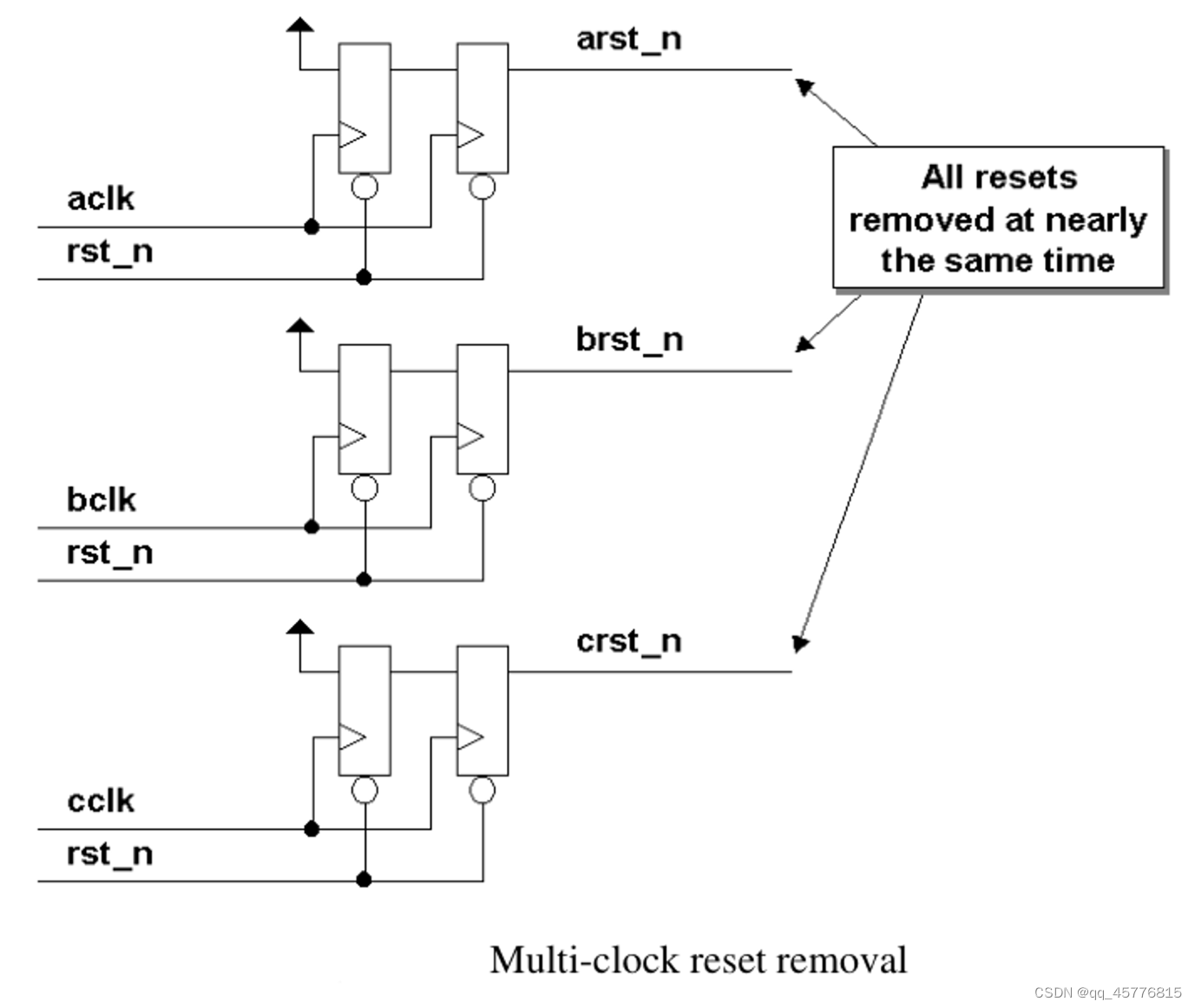

三、多时钟域复位

对于多时钟域的设计,每个时钟域必须有自己单独的复位同步器和分布式复位树。这样才能保证reset能满足不用时钟域的reset recovery time。如下图所示:

对于多个时钟域的解复位顺序有两种情况:

1)大部分多时钟域的设计,解复位的顺序并没有特殊要求。即当前时钟域解复位的时间点,在另一个时钟域的精确时间点并不重要。通常来说,跨时钟域的设计,本身就会带来延时的不确定性。这种情况下,上面的单独建立不同时钟域的复位结构就足够了。

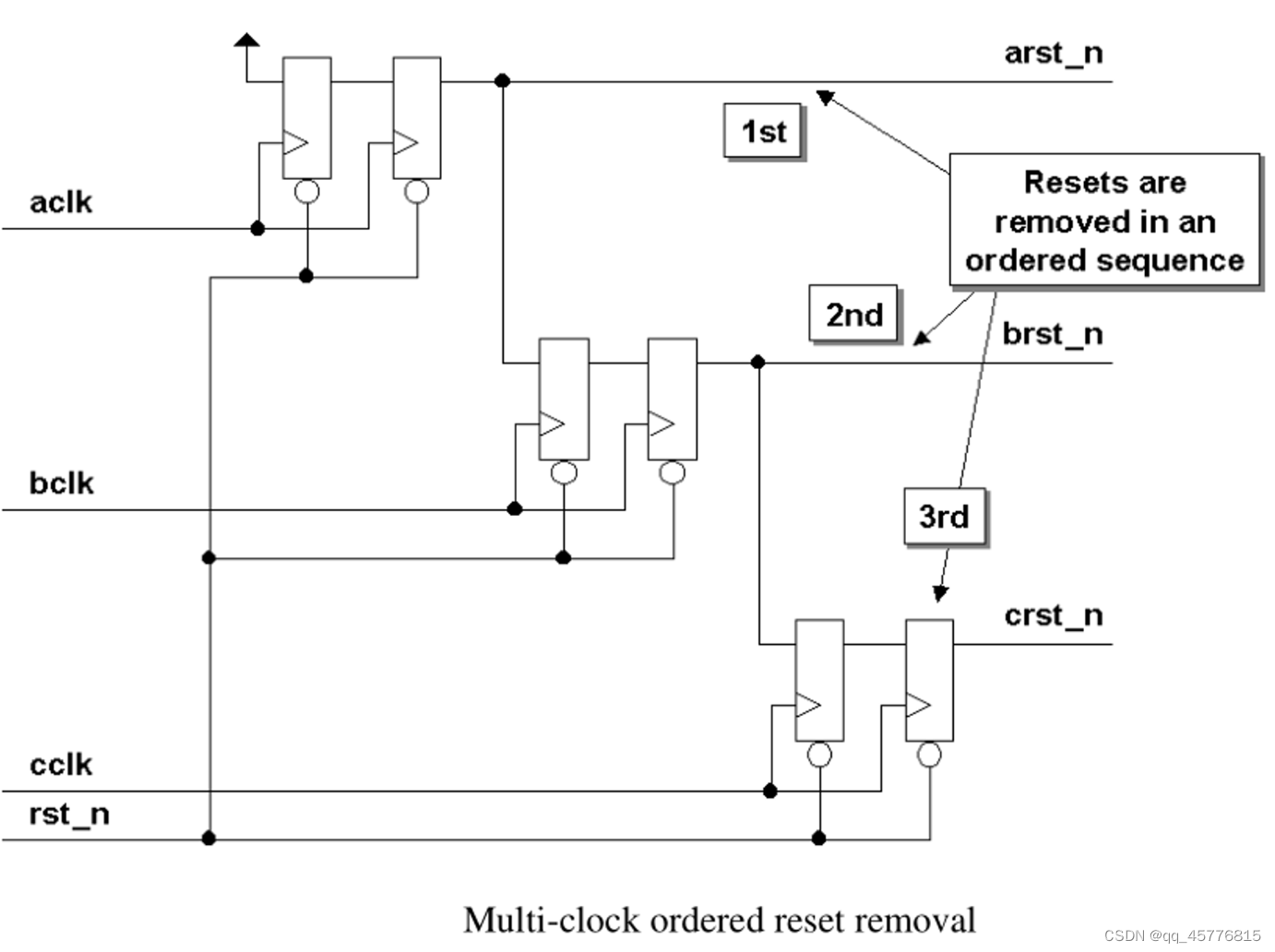

2) 有些多时钟设计,复位解除必须按顺序进行。这种设计,可以使用优先级的复位结构如下所示:

注:

高扇出:

高扇出指的是一个逻辑单元驱动的逻辑单元过多。常见于寄存器驱动过多的组合逻辑单元。至于驱动多少逻辑单元算过多,需要根据工艺,后端实现情况以及芯片本身类型来决定。一般来说如果驱动逻辑大于10K以上,算是比较多的了。

2947

2947

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?