目录

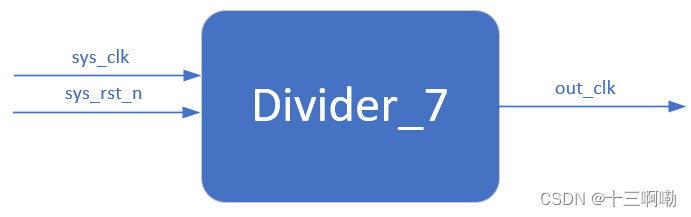

使用Verilog语言设计一个分频器电路,能够对输入时钟进行7分频。

一、逻辑设计

1.端口设计

模块的输入端口包含系统时钟sys_clk、复位信号sys_rst_n;输出端口包含7分频后的输出时钟信号out_clk。

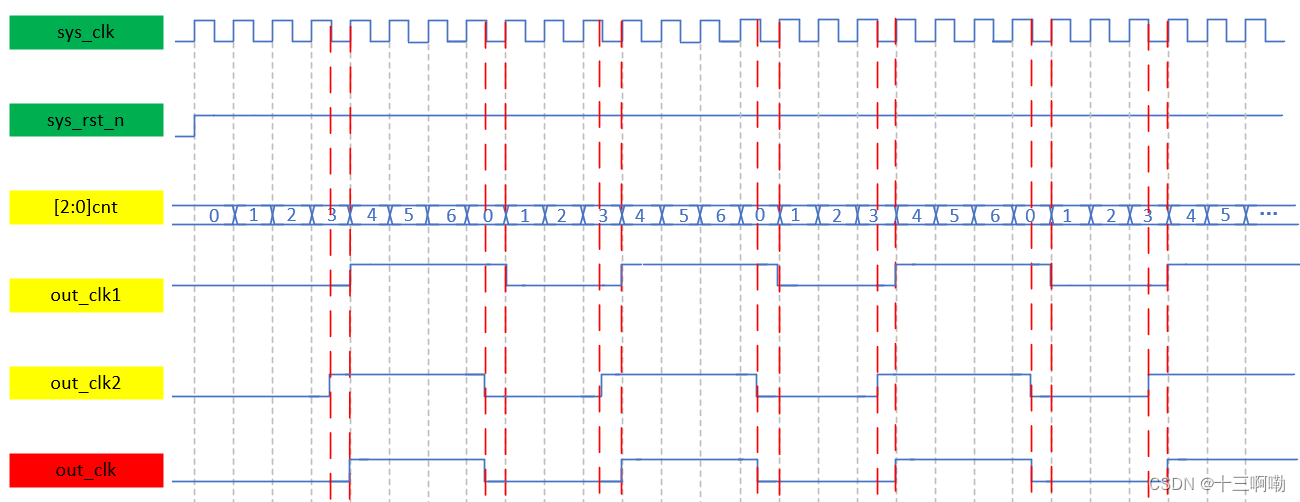

2.波形图绘制

奇数分频实现原理:

假设我们需要分频的倍数为N(奇数)分频(波形图中为7分频),就需要定义一个个数为N的cnt。当cnt=0时out_clk1在 sys_clk的上升沿拉低,当 cnt计数到N/2(7分频时,7/2=3)时 out_clk1在 sys_clk 的上升沿进行翻转;而out_clk2 则在 cnt=0 时的 sys_cllk下降沿进行拉低,当 cnt 计数到 N/2=3时,out_clk2 在 sys_clk 下降沿进行翻转。最后将 out_clk1和out_clk2 的波形相与,就得到了我们分频后输出的out_clk。

二、程序设计

根据波形图使用Verilog编写分频器(divider_7.v)代码

1.分频器代码

代码如下:

// 奇数分频器,实现7分频

module divider_7(

input sys_clk, // 系统时钟输入

input sys_rst_n, // 系统复位信号,低电平有效

output out_clk // 输出时钟

);

//修改N的值和计数器的位宽可以实现其他奇数分频

parameter N = 7; // N(偶数)分频,计数到 N-1,N = 7

parameter EDGE = N/2; //out_clk1和out_clk2翻转边沿数

reg [2:0] cnt ;

reg out_clk1;

reg out_clk2;

//计数器

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) // 复位状态

cnt <= 3'd0;

else if (cnt == N - 1'b1)

cnt <= 3'd0;

else

cnt <= cnt + 3'd1;

end

//out_clk1在上升沿进行翻转

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

out_clk1 <= 1'b0;

else if (cnt == EDGE)

out_clk1 <= ~out_clk1;

else if(cnt == 1'b0)

out_clk1 <= 1'b0;

end

//out_clk1在下降沿进行翻转

always @(negedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

out_clk2 <= 1'b0;

else if (cnt == EDGE)

out_clk2 <= ~out_clk2;

else if(cnt == 1'b0)

out_clk2 <= 1'b0;

end

assign out_clk = out_clk1 & out_clk2; //将out_clk1和out_clk2取相与作为输出时钟

endmodule

2.仿真代码

代码如下:

`timescale 1ns / 1ns

module tb_divider_7();

reg sys_clk ;

reg sys_rst_n ;

wire out_clk;

// 初始化

initial begin

sys_clk = 1'b1; // 初始化系统时钟为高电平

sys_rst_n <= 1'b0; // 复位信号

#201;

sys_rst_n <= 1'b1;

end

// 时钟周期性翻转

always #10 sys_clk = ~sys_clk;

// 实例化

divider_7 divider_7_inst(

.sys_clk (sys_clk ),

.sys_rst_n(sys_rst_n),

.out_clk (out_clk )

);

endmodule

3.仿真结果

out_clk相邻两个上升沿间隔140ns,对应频率为,对sys_clk系统时钟的7分频,与绘制的波形图一致。

总结

在FPGA的设计中,由于板卡的晶振一般是固定的,而对于一些工程而言晶振时钟并不是都能满足设计需求,所以在项目设计中我们经常使用分频器对输入时钟进行分频,本文主要针对奇数分频器的进行设计。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?