目录

边沿检测指的是检测一个信号的上升沿或者下降沿,即产生一个脉冲信号。边沿检测电路根据检测边 沿的类型一般分为上升沿检测电路、下降沿检测电路和双沿检测电路。

一、逻辑设计

1.端口设计

模块的输入端口包含系统时钟sys_clk、复位信号sys_rst_n、检测输入信号signal;输出端口包含上升沿指示信号signal_posedge、下降沿指示信号signal_negedge、双边沿指示信号signal_edge。

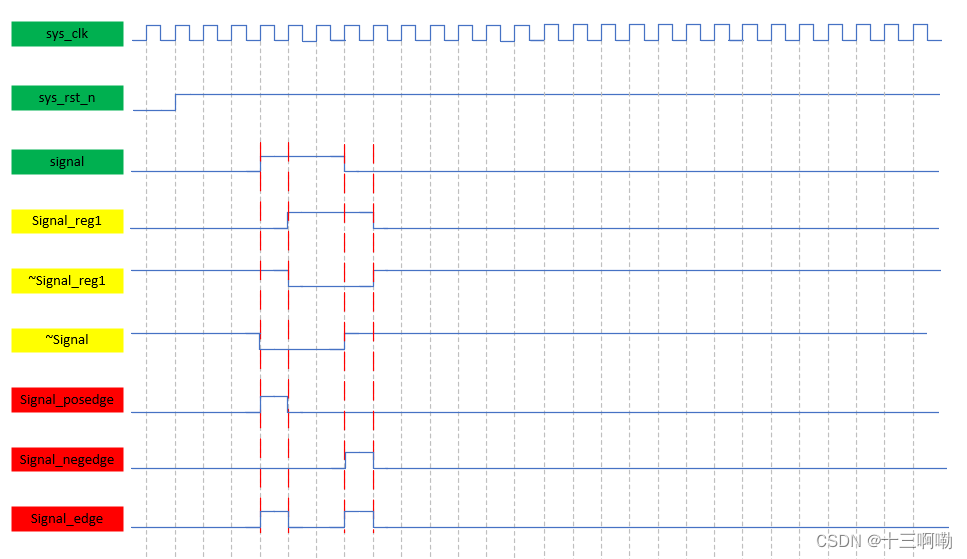

2.波形图绘制

1.上升沿检测电路:

signal信号是一个持续3个时钟周期的信号,我们首先把signal信号寄存一拍,得到signal_reg1信号。我们再用 signal信号和signal_reg1取反再相与,得到一个持续1个时钟周期的脉冲信号signal_posedge 信号,就是信号signal的上升沿指示信号。

2.下降沿检测电路:

signal信号是一个持续3个时钟周期的信号,我们首先把signal信号寄存一拍,得到signal_reg1信号,我们再把 signal信号取反,用signal取反的信号和signal_reg1相与,就可以得到一个持续1个时钟周期的脉冲信号,这个signal_negedge 信号就是signal的下降沿指示信号。

3.双边沿检测电路:

signal信号的上升沿和下降沿也就是signal_edge双边沿检测信号,从图上可以看出,取双边沿的时机正好符合异或门的逻辑,signal_edge信号刚好是 signal和 signal_reg1信号不同的地方为高电平, signal和 signal_reg1异或的结果就是 signal_edge信号,这个信号在signal的上升沿持续一个时钟周期,然后在signal的下降沿后又持续一个时钟周期。

二、程序设计

根据波形图使用Verilog编写边沿检测电路(edge_test.v)代码

1.边沿检测电路代码

代码如下:

module edge_test(

input sys_clk, // 系统时钟信号

input sys_rst_n, // 系统复位信号

input signal, // 待检测的信号

output signal_posedge, // 信号上升沿指示

output signal_negedge, // 信号下降沿指示

output signal_edge // 信号边沿指示

);

reg signal_reg1; // 存储上一时刻的信号值

// 将信号寄存延迟一拍

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

signal_reg1 <= 1'b0; // 复位时信号寄存器清零

else

signal_reg1 <= signal; // 存储当前信号值

end

// 检测信号的上升沿

assign signal_posedge = signal & ~signal_reg1;

// 检测信号的下降沿

assign signal_negedge = ~signal & signal_reg1;

// 检测信号的边沿(包括上升沿和下降沿)

assign signal_edge = signal ^ signal_reg1;

endmodule

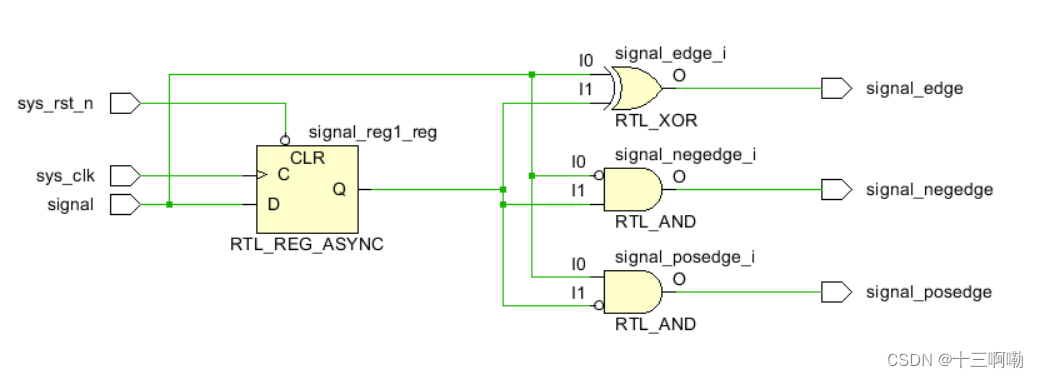

从RTL视图可以看出,signal_reg1是a寄存一拍的结果,signal_posedge 是上升沿检测输出(signal和signal_reg1取反相与),signal _negedge是下降沿检测输出(signal取反和signal_reg相与),signal_edge是双沿检测输出(异或门)。

2.仿真代码

代码如下:

`timescale 1ns / 1ns

module tb_edge_test();

reg sys_clk ;

reg sys_rst_n ;

reg signal ;

wire signal_posedge;

wire signal_negedge;

wire signal_edge ;

// 初始化

initial begin

sys_clk = 1'b1; // 初始化系统时钟为高电平

sys_rst_n <= 1'b0; // 复位信号

signal <= 1'b0; // 初始化待检测信号为低电平

#201;

sys_rst_n <= 1'b1;

#20

signal <= 1'b1; // 改变待检测信号为高电平

#60 // 假设3个周期的高电平信号

signal <= 1'b0;

end

// 时钟周期性翻转

always #10 sys_clk = ~sys_clk;

// 实例化边沿检测模块

edge_test edge_test_inst(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.signal (signal ),

.signal_posedge(signal_posedge),

.signal_negedge(signal_negedge),

.signal_edge (signal_edge )

);

endmodule

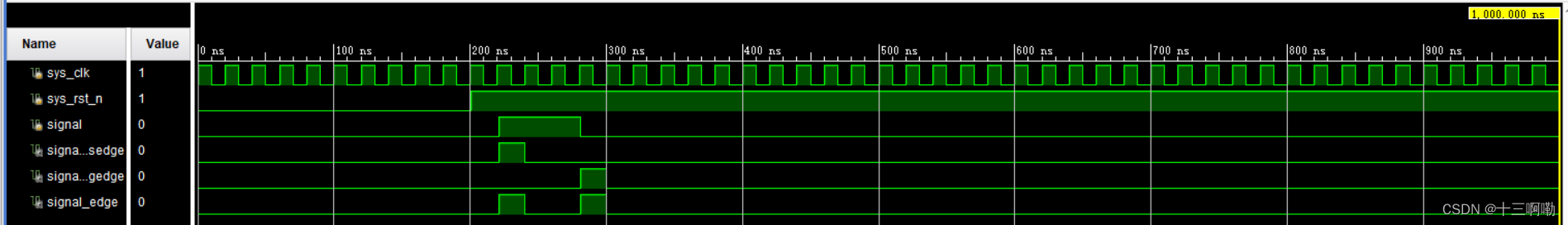

3.仿真结果

仿真波形与我们绘制的波形图一致

总结

在复杂的逻辑设计中,很多情况我们都需要检测信号的跳变。如果一个信号发生跳变,则逻辑给出一 个指示,这个指示用来控制其他信号的动作,这种情况就需要有一个边沿检测电路,本文主要采用组合逻辑设计思想来设计边沿检测电路。

7510

7510

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?