波形文件

常见波形文件格式:

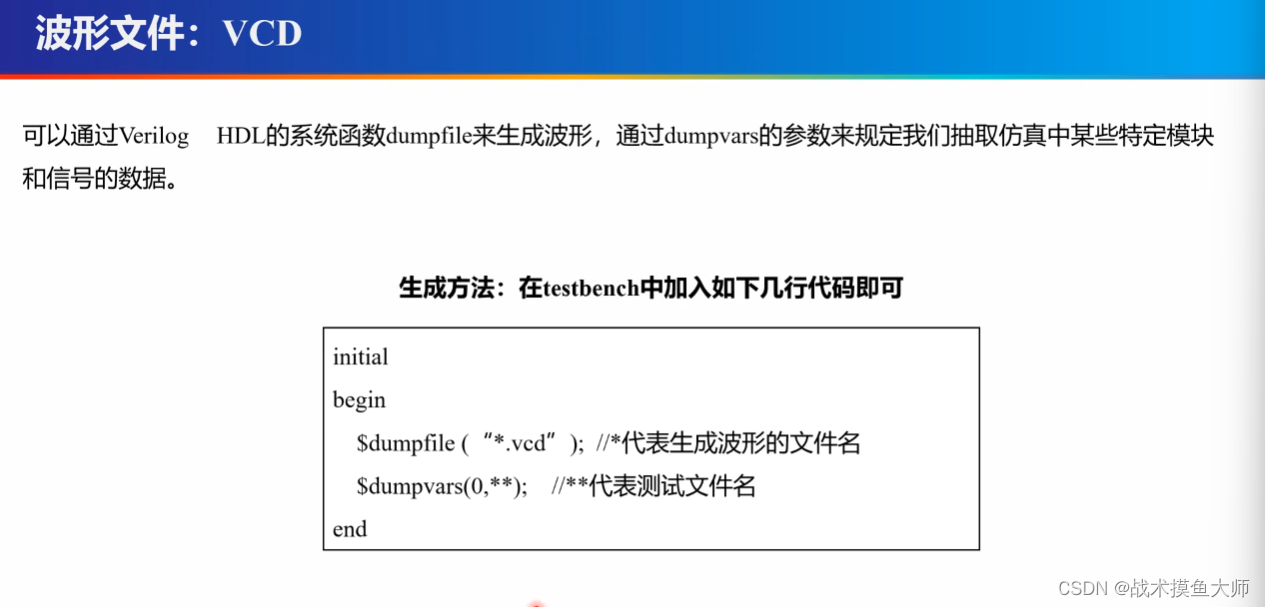

- VCD(Value Change Dump),Verilog HDL语言标准的一部分,标准波形文件,所有仿真器都支持。记录了所有仿真信息,信息最全但是缺点就是体积较大

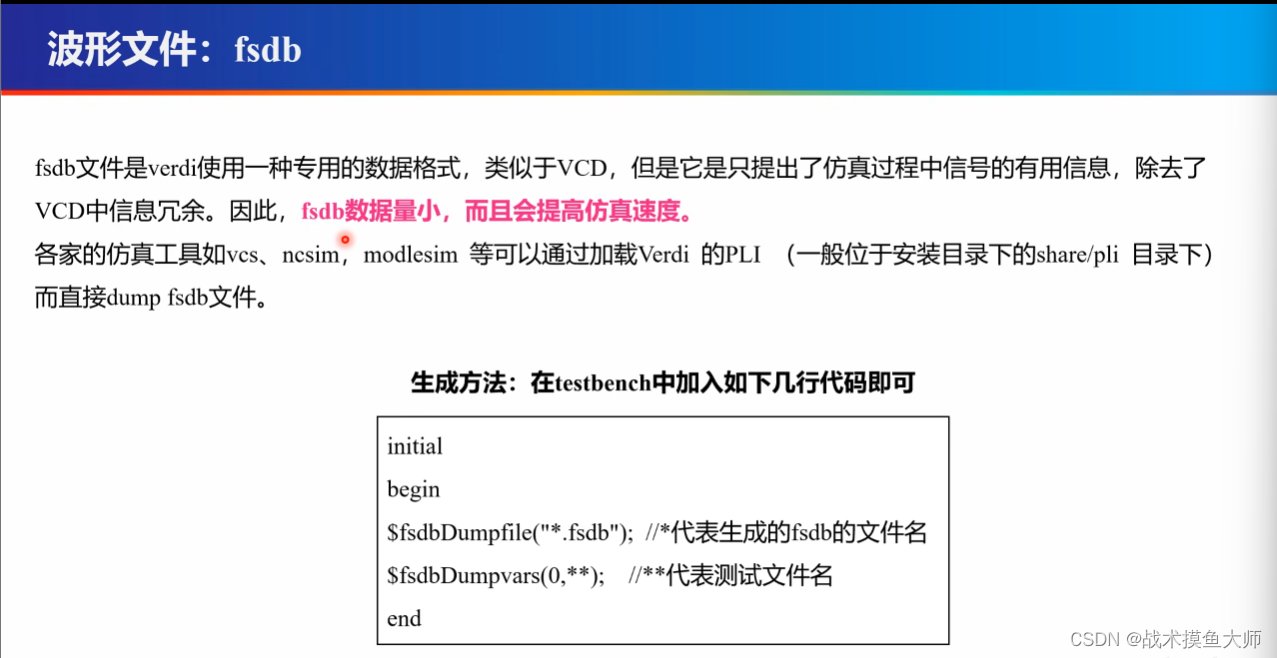

- fsdb(Fast Signal DataBase),Verdi支持

- WLF(Wave Log File),modelsim产生

各家的波形文件不互通,但是都可以由VCD文件转化

推荐调试方法:使用仿真器完成仿真后生成fsdb波形,然后使用verdi进行查看波形与调试【Verdi功能非常强大】

initial

begin

$dumpfile("*.vcd"); //*代表生成波形的文件名

$dumpvars(0,**); //**代表测试文件名

end

initial

begin

$fsdbDumpfile("*.vcd"); //*代表生成波形的文件名

$fsdbDumpvars(0,**); //**代表测试文件名

end

仿真验证方法:开源工具

iverilog+gtkwave

- 开源iverilog 仿真工具

- gtkwave 可以查看标准的vcd、evcd文件,以及其他的一些格式的波形文件

7260

7260

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?