10.9-10.8 其他论题——值变转储文件(VCD)、指定程序块、强度、竞争状态

10.9 值变转储文件

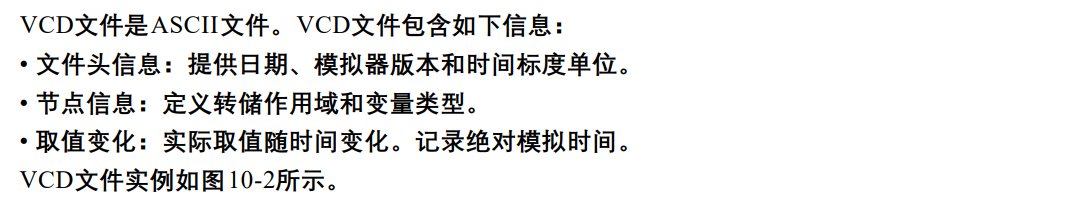

值变转储(V C D)文件包含设计中指定变量取值变化的信息。它的主要目的是为其它后

处理工具提供信息。

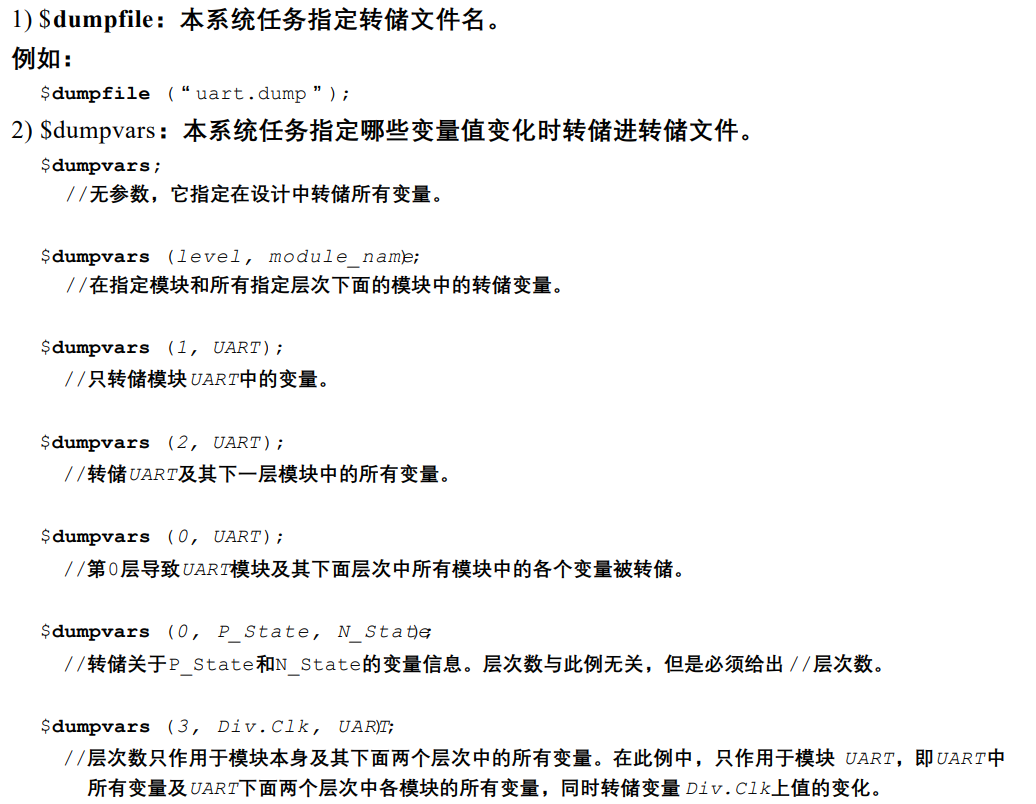

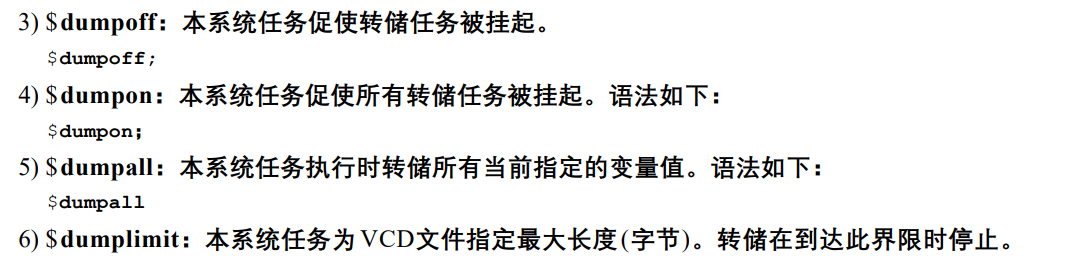

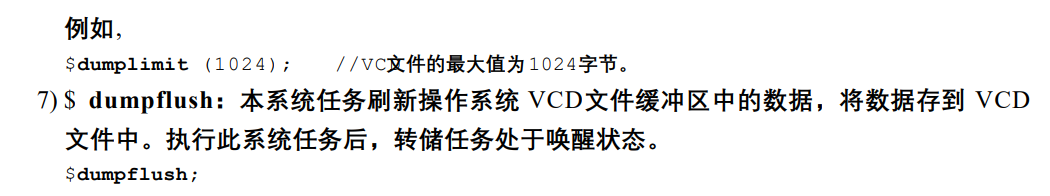

下面的系统任务用于创建和将信息导入 V C D文件。

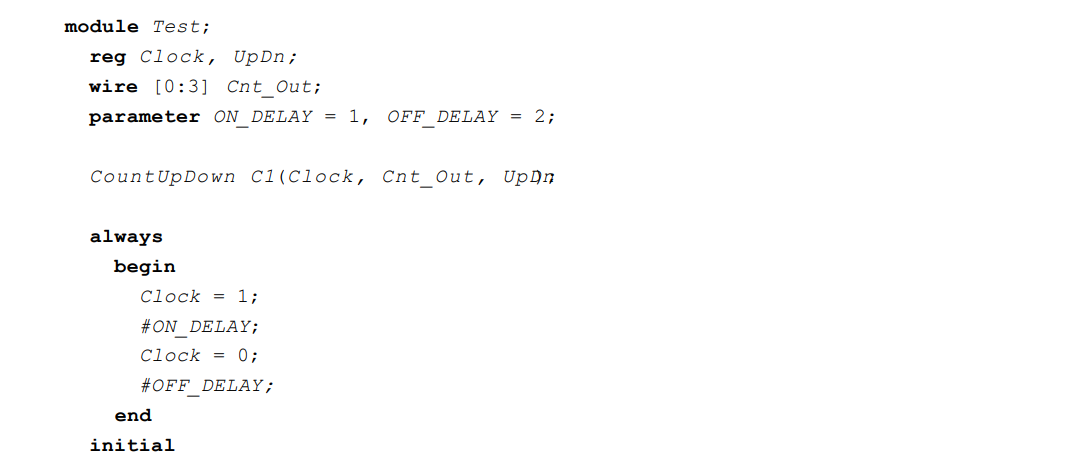

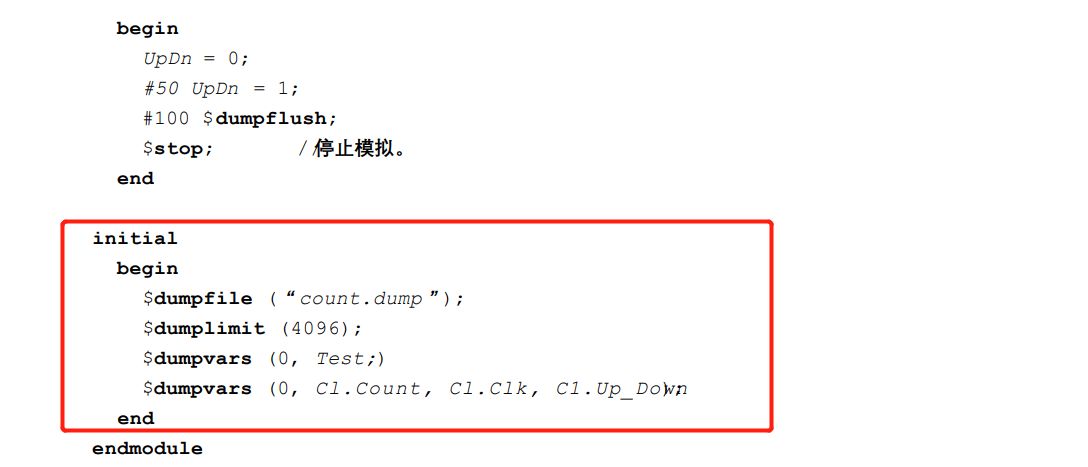

10.9.1 举例

10.9.2 VCD文件格式

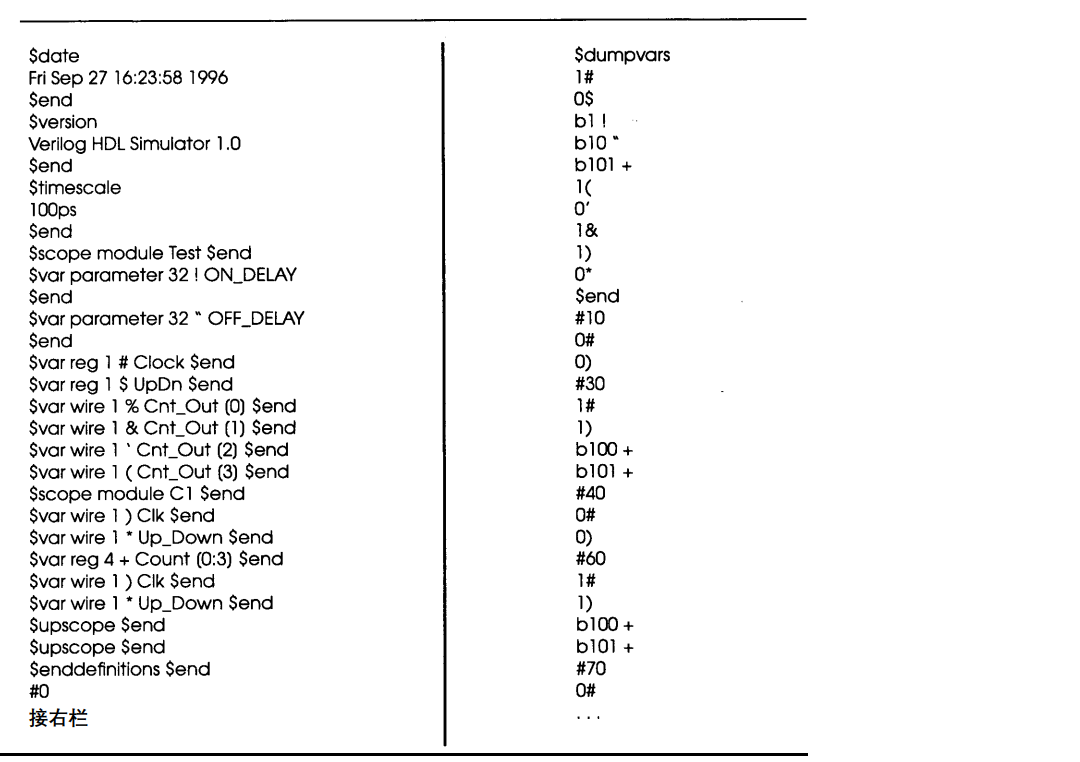

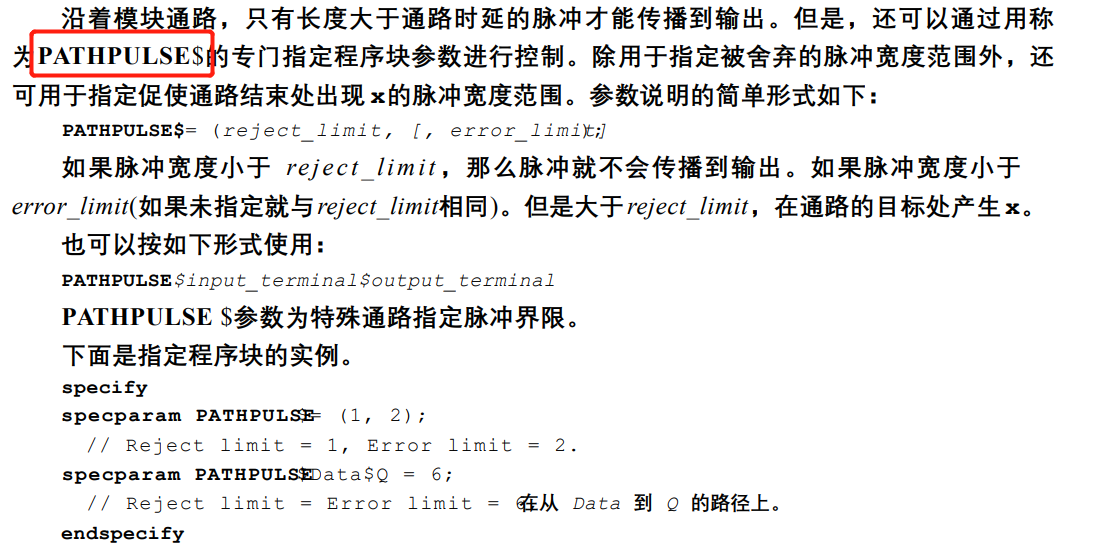

10.10 指定程序块

迄今为止,我们讨论的时延,如门时延和线网时延,都是分布式时延。模块中关于路径

的时延,称为模块路径时延,可以使用指定程序块来指定。通常,指定程序块有如下用途:

1) 指定源和目的之间的通路。

2) 为这些通路分配时延。

3) 对模块进行时序校验。

指定程序块出现在模块说明内。形式如下:

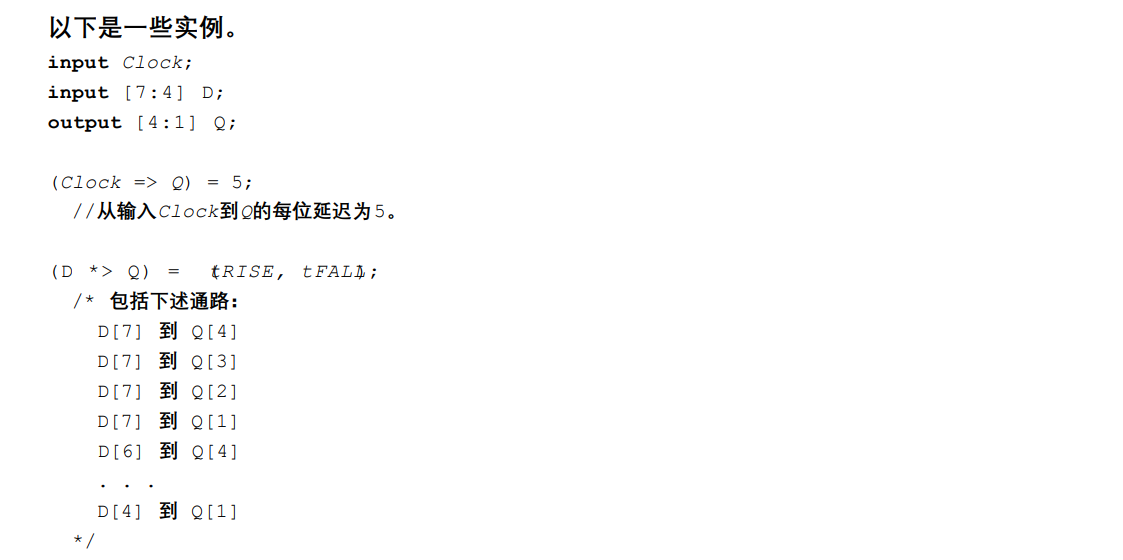

简单通路

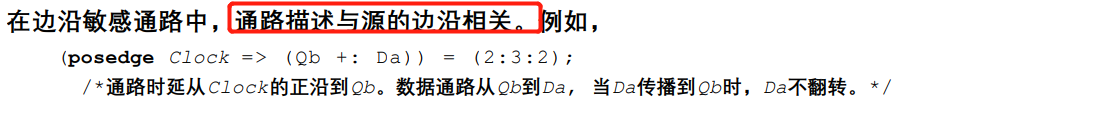

边沿敏感通路

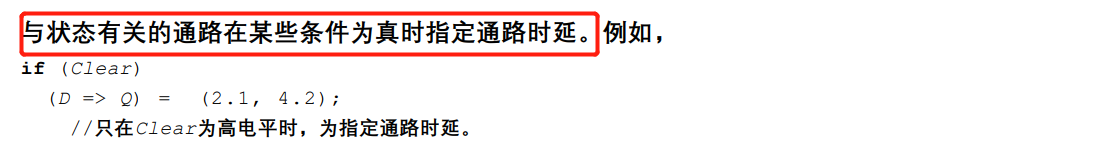

与状态有关的通路

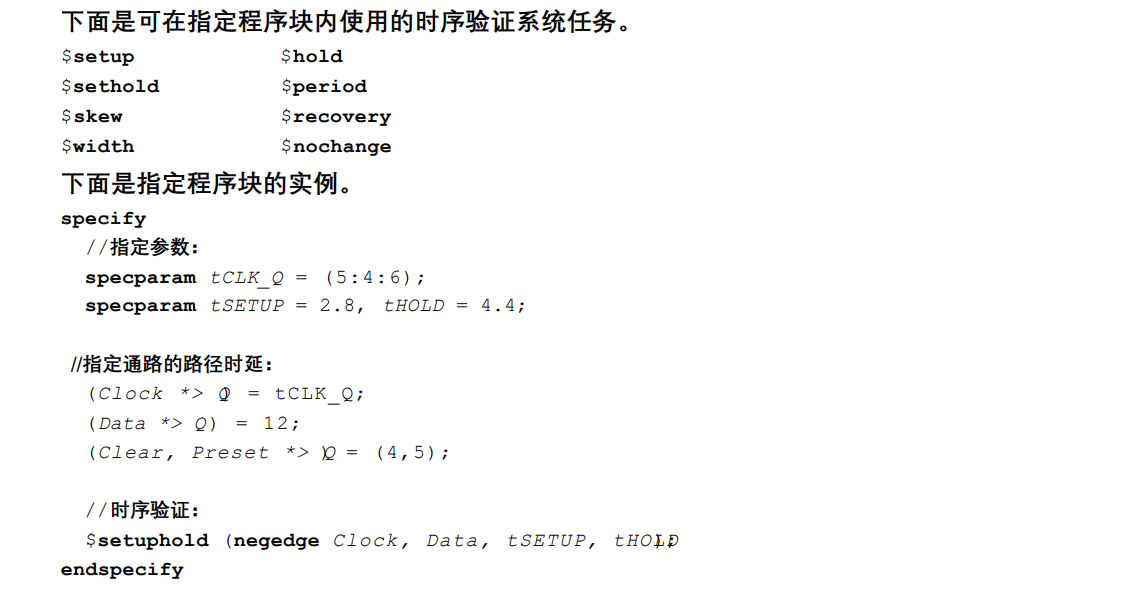

时序验证系统任务

10.11 强度

在Verilog HDL中除了指定四个基本值0、1、 x和z外,还可以对这些值指定如驱动强度和

电荷强度等属性。

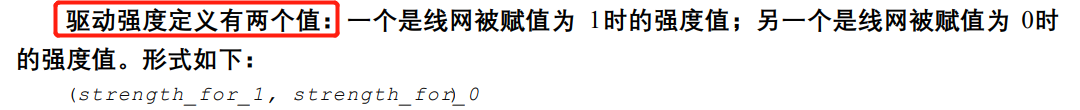

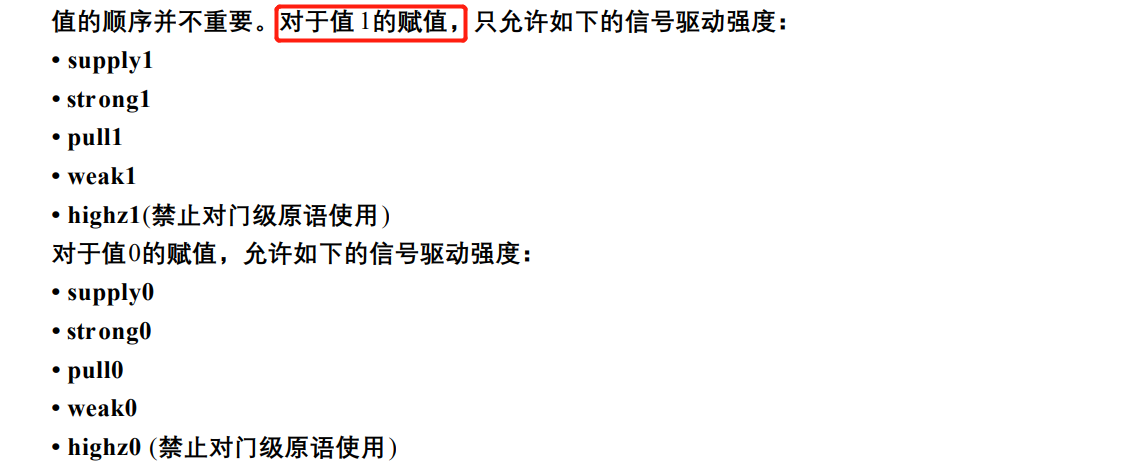

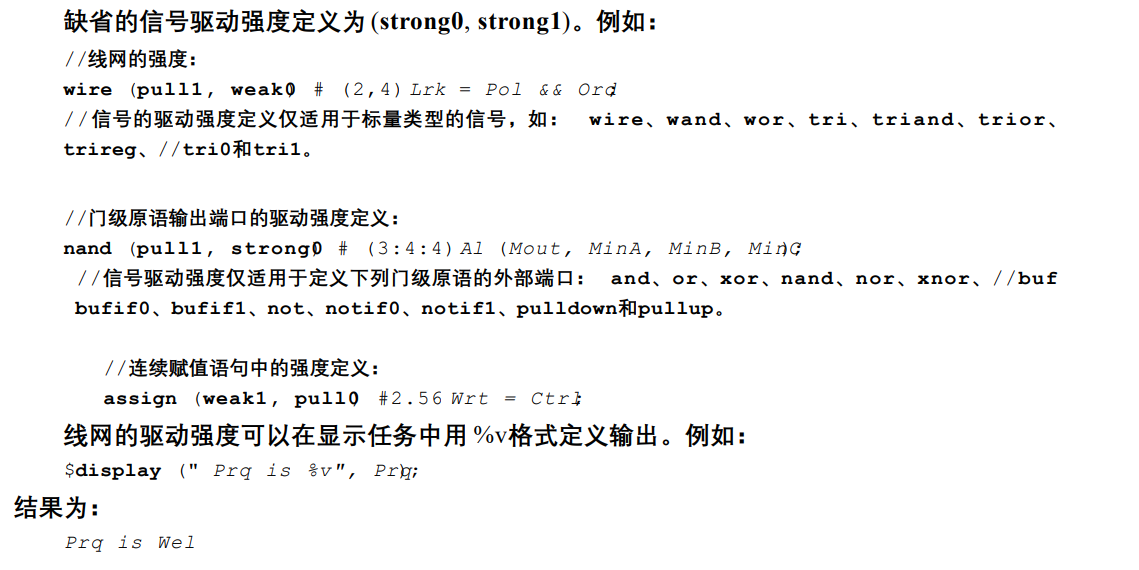

10.11.1 驱动强度

驱动强度可以在如下情况中指定:

1) 在线网说明中带赋值的线网。

2) 原语门实例中的输出端口。

3) 在连续赋值语句中。

10.11.2 电荷强度

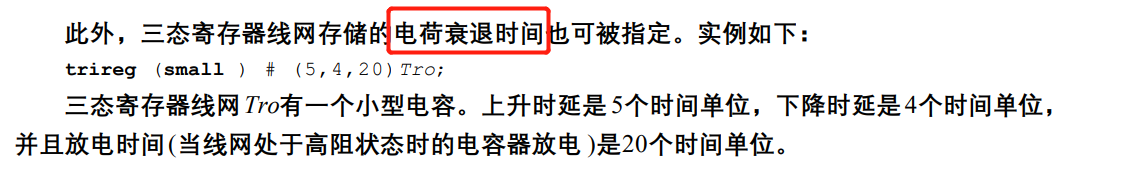

三态寄存器线网也能有选择地规定其存储的电荷强度。三态寄存器线网存储的电荷强度

与三态线网相关的电容大小有关。电荷强度分为三类:

• 小型

• 中型(如果没有特别强调,则为缺省值)

• 大型

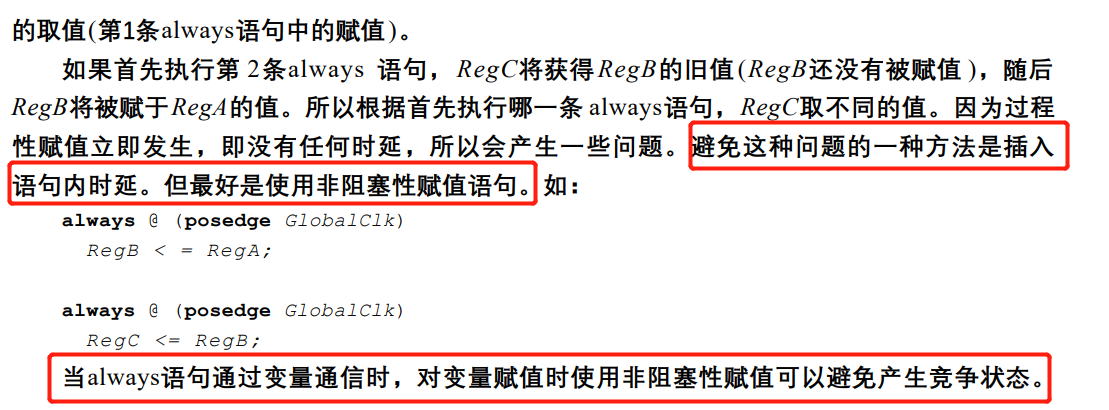

10.12 竞争状态

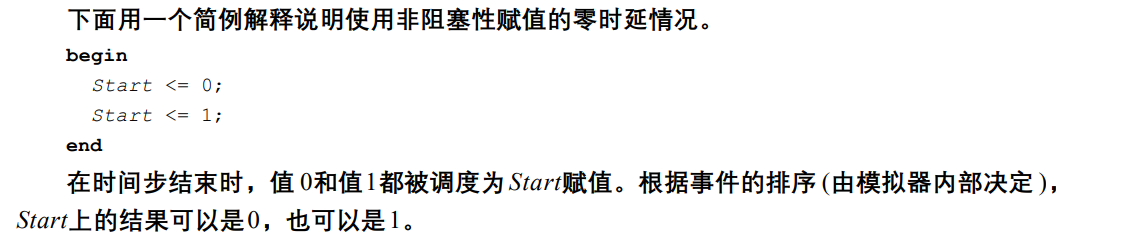

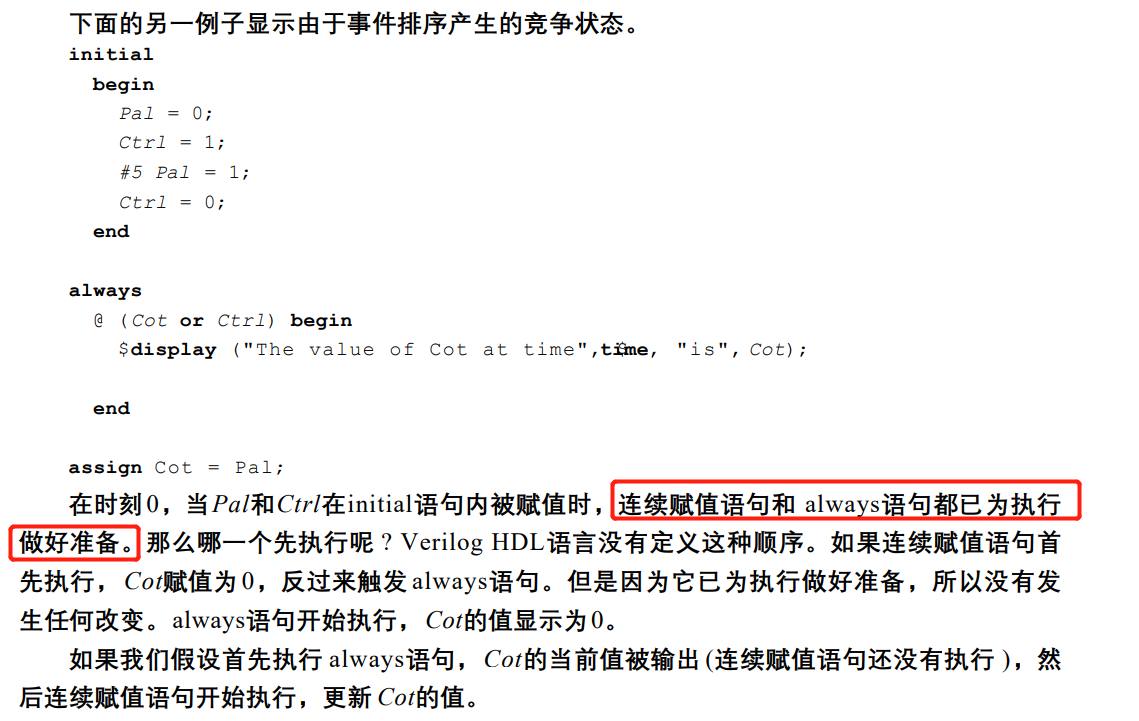

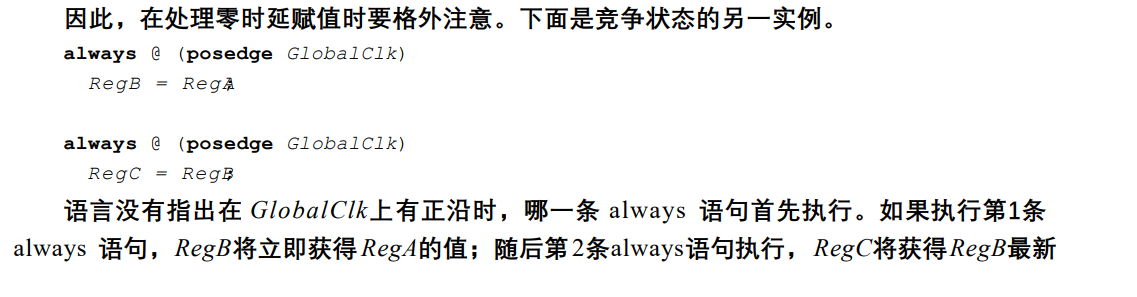

如果在连续赋值或 always 语句中未使用时延,即是零时延时,会产生竞争状态。这是因

为Verilog HDL没有定义同时发生的事件的模拟顺序。

2640

2640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?