对应实验手册请参阅《LoongArch CPU设计实验》。

NOTE:

- minicpu_env/miniCPU/目录下的代码功能不全,是有意为之,无需提issue修正。

- mycpu_env/myCPU/目录下的代码有功能错误,亦是有意为之,无需提issue修正。

================================================================================

实验安排简介

// dc_env

exp1 : 跑马灯实验。熟悉Vivado和FPGA实验环境基本使用技能。

exp2 : 寄存器堆仿真;

exp3 : 同步、异步 RAM 仿真、综合实现;

exp4 : 数字逻辑电路的设计与调试。

// minicpu_env

exp5 : 5条指令单周期CPU,跑斐波那契数程序,给RTL填空方式。

// mycpu_env - soc_dram i/f (distributed ram interface)

exp6 : 20条指令单周期CPU,测试规模缩减版func的n1~n20,给RTL找错误并修正。

// mycpu_env - soc_bram i/f (block ram interface)

exp7 : 20条指令五级流水CPU,不考虑hazard,测试插NOP的func的n1~n20,增量开发。

exp8 : 20条指令五级流水CPU,cancel解决control hazard,阻塞解决data hazard,测试

func的n1~n20,增量开发。

exp9 : 20条指令五级流水CPU,forward优化data hazard处理,测试func的n1~n20,增量

开发。

exp10 : 增加用户态运算类指令,测试func的n1~n36,增量开发。

exp11 : 增加用户态转移指令和除了ll.w、sc.w之外的用户态访存指令,测试func的n1~n46,

增量开发。

exp12 : 支持syscall例外,测试func的n1~n47,增量开发。

exp13 : 支持更多例外,测试func的n1~n58,增量开发。

// mycpu_env - soc_hs_bram i/f (handshaking block ram interface)

exp14 : CPU采用带握手机制的接口,测试func的n1~n58,增量开发。

// mycpu_env - soc_axi i/f (AXI bus interface)

exp15 : CPU采用AXI接口,外部固定延迟响应,测试func的n1~n58,增量开发。

exp16 : CPU采用AXI接口,外部随机延迟响应,测试func的n1~n58,增量开发。

exp18 : CPU集成TLB模块后并支持TLB相关指令和CSR,测试func的n1~n70,增量开发。

exp19 : CPU支持TLB MMU功能,测试func的n1~n72,增量开发。

exp21 : CPU实现指令Cache,测试func的n1~n72,增量开发。

exp22 : CPU实现数据Cache,测试func的n1~n72,增量开发。

exp23 : CPU支持CACOP指令,测试func的n1~n79,增量开发。

// mycpu_env - module_tlb

exp17 : TLB模块设计,非func测试,单独开发。

// mycpu_env - module_cache

exp20 : Cache模块设计,非func测试,单独开发。

5条指令

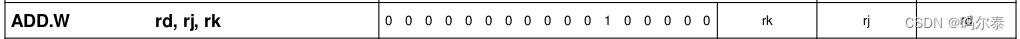

1. add_w

指令概述

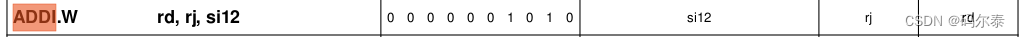

2. addi_w

指令概述

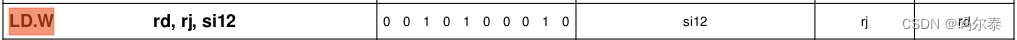

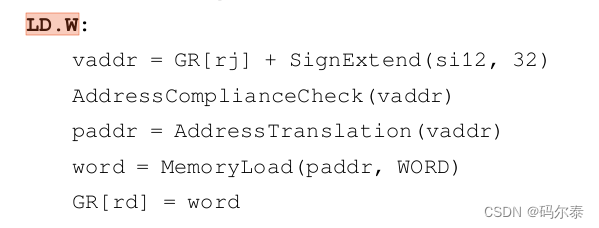

3. ld_w

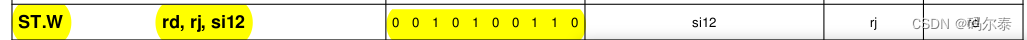

4. st_w

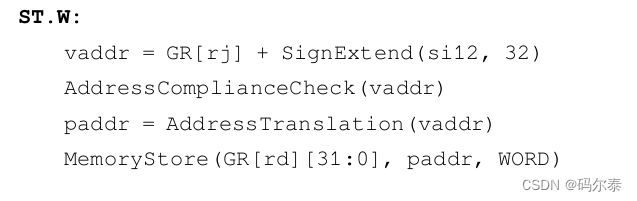

5. bne

填充代码

第一处代码

assign inst_add_w = op_31_26_d[6'h00] & op_25_22_d[4'h0] & op_21_20_d[2'h1] & op_19_15_d[5'h00];

assign inst_addi_w = op_31_26_d[6'h00] & op_25_22_d[4'ha];

assign inst_ld_w = op_31_26_d[6'h0a] & op_25_22_d[4'h2];

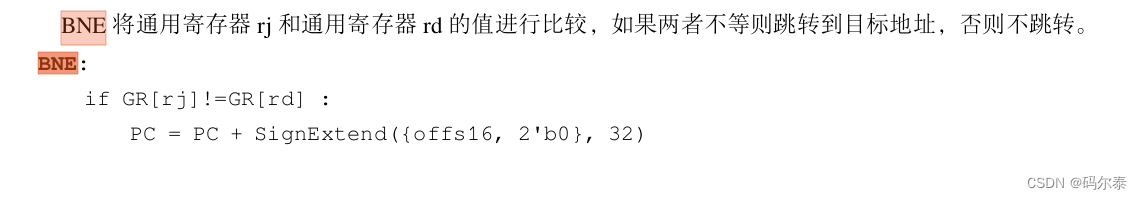

assign inst_st_w = op_31_26_d[6'h0a] & op_25_22_d[4'h6];//在这里实现inst_st_w指令的译码

assign inst_bne = op_31_26_d[6'h17];

第二处代码,这里不确定正确

assign src2_is_imm = inst_bne|inst_addi_w|inst_ld_w|inst_st_w;//在这里实现立即数选择信号

assign res_from_mem = inst_ld_w;

assign gr_we = inst_add_w | inst_ld_w | inst_addi_w;

assign mem_we = inst_st_w;

assign src_reg_is_rd = inst_bne | inst_st_w;

第三处代码

regfile u_regfile(

.clk (clk ),

.raddr1 (rf_raddr1 ),

.rdata1 (rj_value),

.raddr2 (rf_raddr2 ),

.rdata2 (rkd_value),

.we (gr_we ),

.waddr (rf_raddr2 ),

.wdata (rf_wdata )

);//在空出的括号里完成引脚匹配

第四处代码

assign br_offs = {i16[13:0],{18{1'b0}}};//在这里完成br_offs信号的生成

assign br_target = pc + br_offs;

assign rj_eq_rd = (rj_value == rkd_value);

assign br_taken = valid && inst_bne && !rj_eq_rd;

assign nextpc = br_taken?br_target:pc+{32'h0_0_0_4};//在这里实现nextpc信号的生成

assign imm = {{20{i12[11]}},i12[11:0]};

assign alu_src1 = rj_value;

assign alu_src2 = rkd_value;//在这里实现alu_src2信号

assign alu_result = alu_src1+alu_src2;

第五处代码

assign alu_result = alu_src1+alu_src2;

assign data_sram_we = mem_we;

assign data_sram_addr = alu_result;

assign data_sram_wdata = rkd_value;

assign rf_wdata = alu_result;//在这里完成写回寄存器值的选择

3393

3393

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?