文章目录

一、存储器分类

存储器:存放二进制表示的程序和数据,由大量的存储基元组成。即存放指挥计算机工作的程序、计算机处理的中间数据及最终数据。

1-1 内部存储器(内存或主存)

①CPU可直接访问内存

②存放系统软件和正执行的程序及使用的数据

③容量小,存取速度快

1-1-1 随机存取存储器(RAM)

具有易失性

(1)双极性

(2)MOS型

- 静态(SRAM)

用两个双极型晶体管或基于6个MOS场效应管的双稳态电路构成基本存储单元,电路结构复杂,集成度较低,功耗也大,但存取速度很快,访问时间可小于十ns。主要用作高速缓存。 - 动态(DRAM)

①用MOS开关管控制电容的充放电来存储信息,电路简单,但存取速度慢。

②容量大,价格便宜,pc机上的内存都采用DRAM,而且做成内存条,便于扩充内存容量。

1-1-2 只读存储器(ROM)

- 掩膜ROM(MROM)

①不可编程。

②适合大批量生产。 - 可编程ROM(PROM)

①一次性编程。

②只用于大批量生产。 - 可擦除ROM(EPROM)

采用紫外光照射便能擦除芯片的内容,可以反复编程。 - 电可擦除ROM(EEPROM)

用TTL电平信号控制起其写入和擦除。 - 闪速存储器(Flash Memory)

①能不加电而长期保存信息,抗干扰能力强。

②能在线进行快速电擦除。

③价格已低于DRAM,容量则接近于DRAM。

1-2 外部存储器(外存或辅存)

①存放暂不执行或还未被处理的程序或数据。

②容量大,存取速度慢。

-

磁盘

硬盘

软盘 -

磁带

-

光盘

-

闪存盘,卡

1-3 存储器的性能指标

-

存储容量:地址单元*位数

▶ \blacktriangleright ▶ 8086用20根地址线寻址1MB。

▶ \blacktriangleright ▶ 地址单元—取决于存储器地址线的位数n;

▶ \blacktriangleright ▶ 位数——取决于存储器数据线位数m。

▶ \blacktriangleright ▶ 常用单位:KB、MB、GB、TB其中:1KB= 2 10 2^{10} 210B

1MB= 2 10 2^{10} 210kB= 2 20 2^{20} 220B

1GB= 2 10 2^{10} 210MB = 2 30 2^{30} 230B

1TB= 2 10 2^{10} 210GB 2 40 2^{40} 240B -

存取速度

常用存取时间来衡量存储器的存取速率。 -

功耗

有效功耗

待机功耗 -

可靠性

体现在对温度变化,电磁干扰等的抗干扰能力上 -

性价比

外层要求容量极大,内存的容量和速度都很重要,而高速缓存则要求速度非常快。

二、随机存取存储器RAM

2-1 静态RAM(SRAM)

(1)SRAM存储数据原理

- 特点:

①内部管子较多,功耗大,策成度低。

②工作稳定.存取速度快,不需要刷新电路。

③工作电源失去.保存的信息全部消失。 - 包含6个MOS晶体管:

▶ \blacktriangleright ▶ T 1 T_1 T1 T 2 T_2 T2:双稳态触发器

AB=01为信息0

AB=10为信息1

▶ \blacktriangleright ▶ T 3 T_3 T3 T 4 T_4 T4:负载管

▶ \blacktriangleright ▶ T 5 T_5 T5 T 6 T_6 T6:控制管

行选X高电平 T 5 T_5 T5 T 6 T_6 T6导通

列选Y高电平 T 7 T_7 T7 T 8 T_8 T8导通

XY均高,选中,可读/写

(2)SRAM芯片6116(2K×8位)

-

6264(8K×8)

-

6116只需11根数据线( A 10 A_{10} A10~ A 0 A_0 A0)

-

8根双向数据线(I/ O 7 O_7 O7~I/ O 0 O_0 O0),在两个方向上都有三态门缓冲器,不对芯片读/写时,三态门都处在高阻态,使芯片与数据总线“脱离关系”。

-

有三个读/写控制信号:片选信号 C S ‾ \overline{CS} CS,写入允许命令 W E ‾ \overline{WE} WE,读出允许 O E ‾ \overline{OE} OE

C S ‾ \overline{CS} CS O E ‾ \overline{OE} OE W E ‾ \overline{WE} WE 工作方式 0 0 1 读 0 1 0 写 1 × × 未选

2-2 动态RAM

(1)DRAM存储数据原理

- 存储单元由1个MOS管和1个小电容C构成。C充满电荷便保存了信息1,无电荷为0。

- 数据输入输出端连数据总线的某一位 D 1 D_1 D1(位线)。

- 行选信号X是对低位地址信号(如 A 7 A_7 A7~ A 0 A_0 A0)译码产生的,列选信号Y是对高位地址信号(如 A 15 A_{15} A15~ A 8 A_8 A8)译码形成-只有X、Y都高时.该单元才被选中。

- 写操作时,X=1, Y=1,Q和T管均导通,要写入值(0或1)从 D 1 D_1 D1加到C上。根据要写入的值,C很快完成充电(1)或放电(0)过程。

- 读操作时,Q和T同样导通,存储在C上电荷通过Q、刷新放大器和T输出到 D 1 D_1 D1。

- 放大器的灵敏度和增益都很高,能将C上电荷量转换成0或1的逻辑电平,确保读出信息的正确性。

(2)DRAM芯片2164

- 除了正常的读写操作外,DRAM还要定时刷新及充电,即补充电容上的电荷,刷新间隔一般为两毫秒,按存储器阵列的行逐行进行全部刷新一遍。刷新期间,DRAM不能被读写。

- 一个刷新周期可实现512个单元的刷新单元的刷新,用128个刷新周期。

三、只读存储器ROM

3-1 可编程可擦除ROM(EPROM)

(1)基本存储单元

- 存储信息

浮栅管的栅极周围被二氧化硅绝缘层包围,所以原始状态下浮栅不带电荷,因而不导通,位线D上是高电平,即存储了信息1。 - 编程

在其漏极D和源极S之间,加上25V的高电压和编程脉冲,D、S间被瞬时雪崩击穿,大量电子通过绝缘层注入到浮栅,使浮栅管导通,它存储的信息就变为0。由于浮栅被绝缘层包围,注人的电子不会泄露,保存的信息也就不会丢失。 - 擦除

存储单元中的浮栅管浮栅上的电荷﹐会形成光电流泄露,使它们又恢复成原始状态1,从而擦除了所有信息。擦除后的EPROM还可以重新编程。 - EPROM的显著优点是可以多次编程,但不能在线编程。

编程过程总是从头到尾,对一块芯片的全部单元进行重写,因此不能对芯片中的部分内容(哪怕是一个字节)实现修改。

(2)Intel27178EPROM芯片 - Intel27178是一种16K×8的EPROM芯片

- 芯片的内部结构:

▶ \blacktriangleright ▶存储阵列:由128K×1个带浮动栅的 MOS管构成,总共可保存16K×8位二进制信息;

▶ \blacktriangleright ▶X译码器:即行译码器,对7位行地址( A 6 A_6 A6~ A 0 A_0 A0)进行译码;

▶ \blacktriangleright ▶Y译码器:即列译码器,对7位行地址( A 13 A_{13} A13~ A 7 A_7 A7)进行译码;

▶ \blacktriangleright ▶输出允许、片选和编程逻辑:对输入的控制信号 C E ‾ \overline{CE} CE、 O E ‾ \overline{OE} OE和 P G M ‾ \overline{PGM} PGM进行逻辑组合,实现片选并控制信息的读/写;

▶ \blacktriangleright ▶数据输出缓冲器:8位,每1位都有三态门,读出的1字节数据经过它缓冲后,从数据总线传给CPU。

3-2 电可擦除可编程ROM(EEPROM)

- EEPROM即电可擦除PROM,也称 E 2 P R O M E^2PROM E2PROM。

- 特点:

▶ \blacktriangleright ▶单电源供电

▶ \blacktriangleright ▶按字节擦除和改写

▶ \blacktriangleright ▶在线编程

▶ \blacktriangleright ▶兼有ROM和RAM的特点

四、存储器与CPU的连接

4-1 设计接口应考虑的问题

- CPU总线的负载能力

- CPU的时序与存储器存取速度之间的配合

- 存储器地址分配和存储器容量的扩展

- 控制信号的连接

4-2 存储接口的设计

-

地址译码器

-

存储空间的扩展

可以采用位扩展、字扩展和字位扩展三种方法。

▶ \blacktriangleright ▶位扩展:(不需地址线),用8片64K×1的DRAM芯片并联,就可以实现这种从1位宽度到1字节宽度的扩展。

▶ \blacktriangleright ▶字扩展:“字”的含义就是内存中存放的一个数据,可以是8、16或32位宽度。

▶ \blacktriangleright ▶字位扩展:存储器芯片的容量和位都需要进行扩展。 -

形成片选信号的三种方法

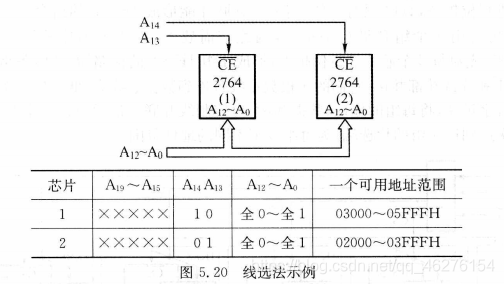

▶ \blacktriangleright ▶线选法:

▶ \blacktriangleright ▶全译码法:

它让全部高位地址都参与译码,这样每个存储单元的地址便都是唯一的,不存在地址重叠问题,但译码电路要复杂些。

▶ \blacktriangleright ▶部分译码法:这种方法只对高位地址线中的某几位译码,生成片选信号。对被选中的芯片而言,未参与译码的高位地址信号可以是0或1,因此每个存储单元将对应多个地址。编程时一般将未用的地址位设为0。部分译码能简化译码电路,但与线选法一样会出现重叠地址,浪费地址空间。

1320

1320

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?