流程

- 打开 Vivado 同时打开 Tcl Console 窗口

- 打开将要存放新建工程的路径

-

cd d:/proj_workspace/tcl_bram - 新建工程

-

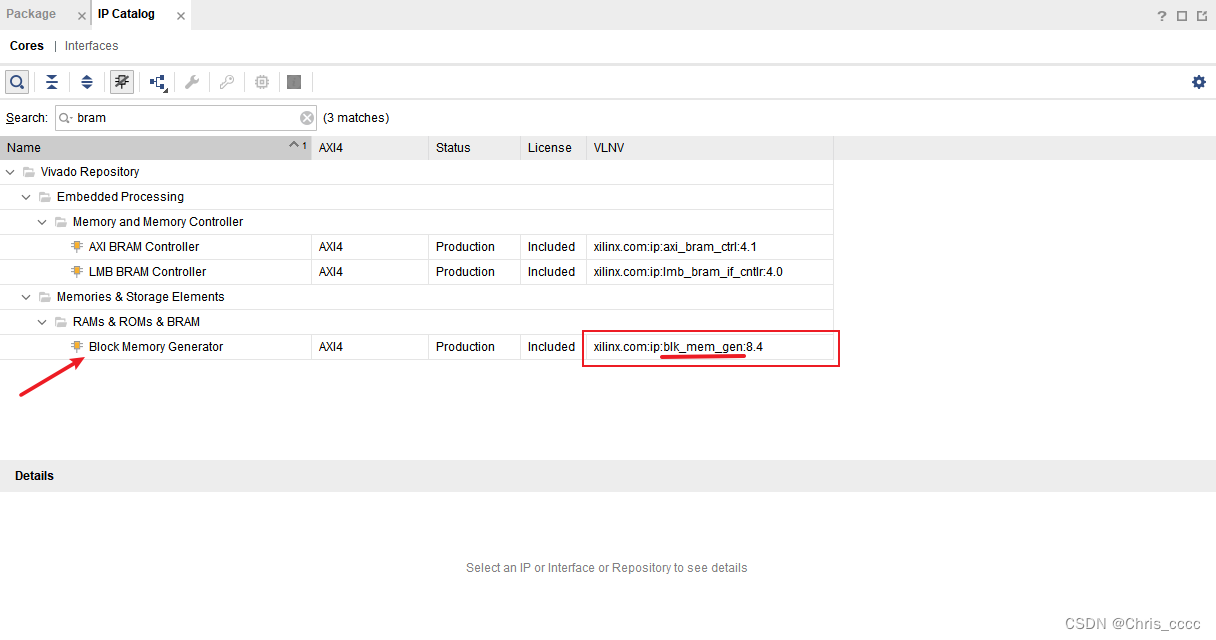

create_project \ #"\"为换行符 -name tcl_bram_routines #工程命名 - 在IP Catalog中找到需要添加的IP

- 添加 IP 并设置相关参数

-

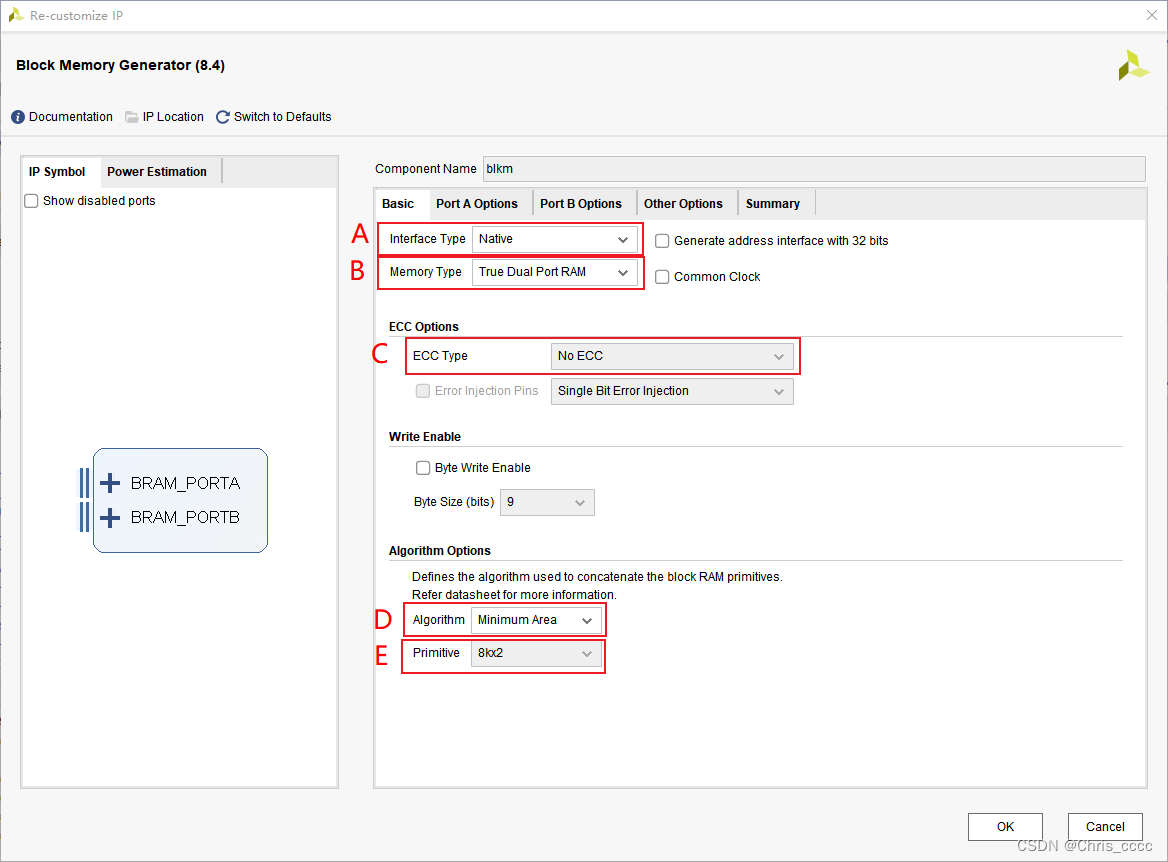

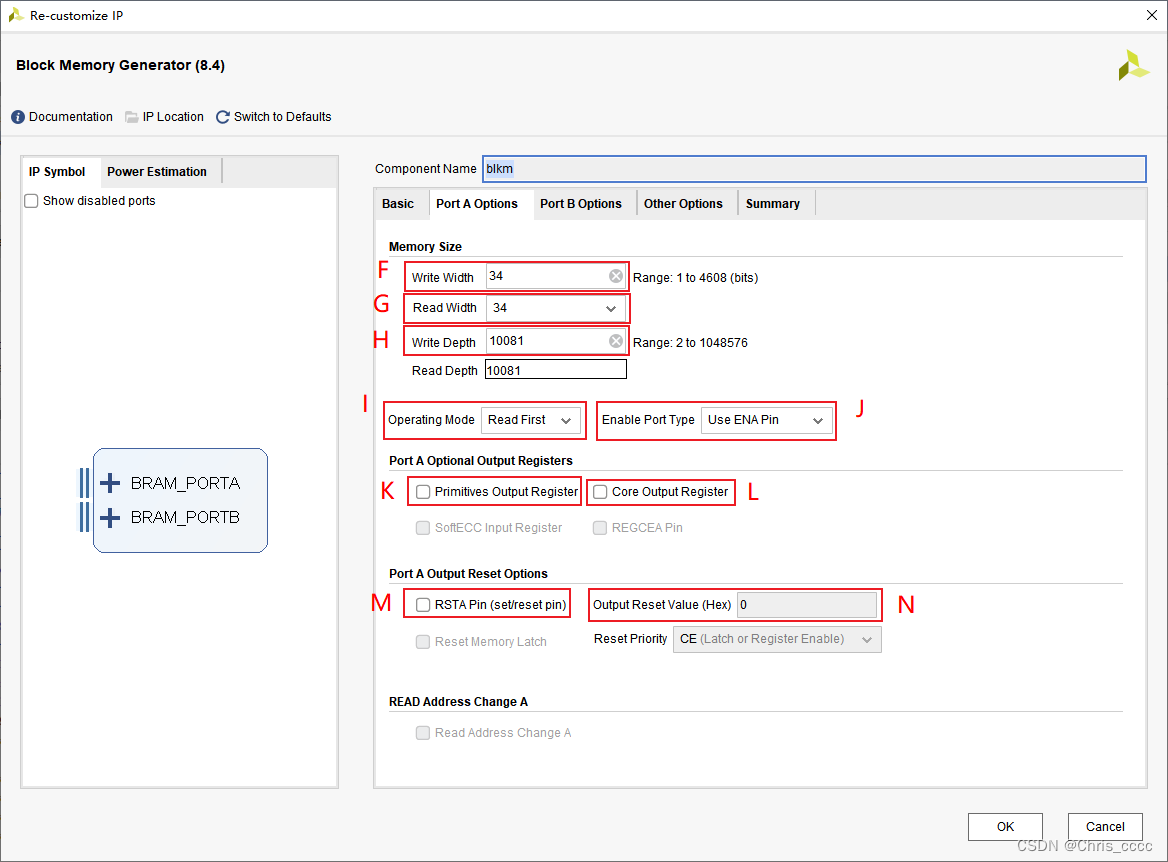

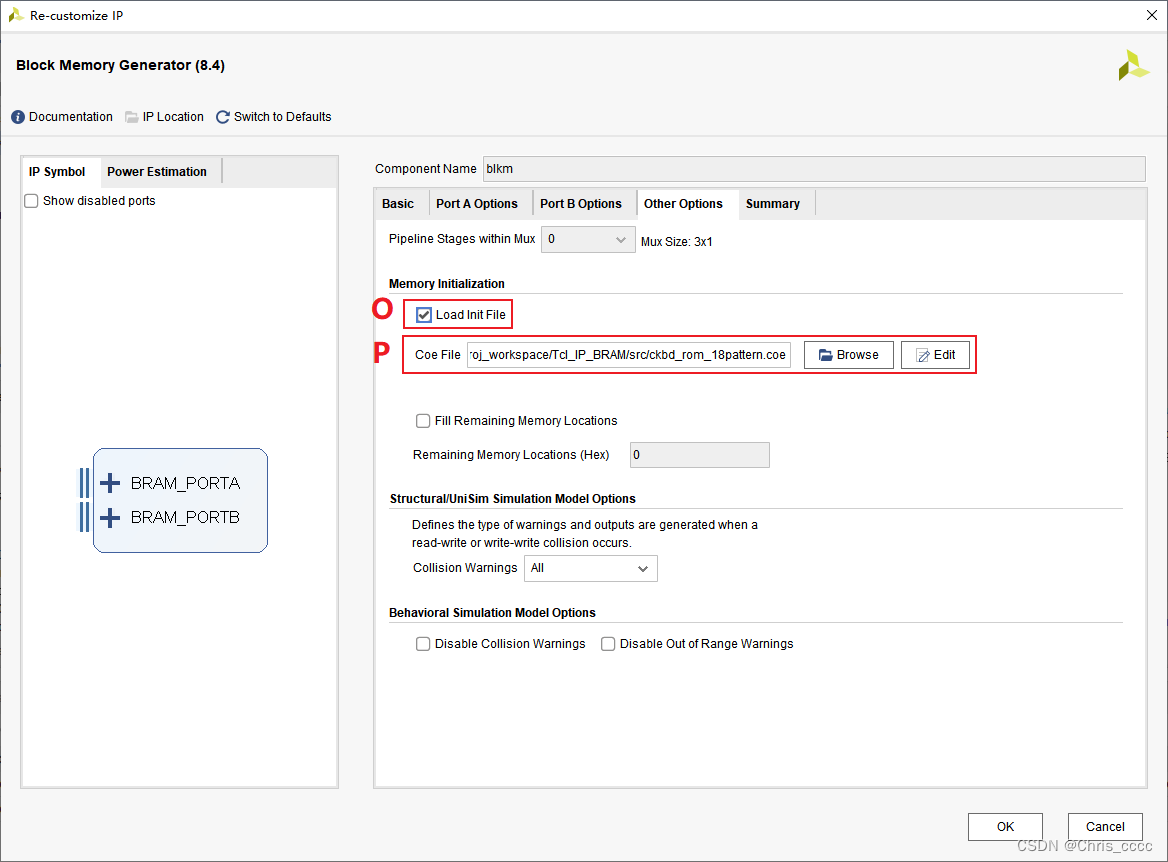

create_ip \ -name blk_mem_gen \ #上一步骤中找到的IP名称 -vendor xilinx.com -library ip \ -module_name blkm \ # verilog中module命名 set_property -dict [list \ CONFIG.Interface_Type {Native} \ #A CONFIG.Memory_Type {True_Dual_Port_RAM} \ #B CONFIG.ecctype {No_ECC} \ #C CONFIG.Algorithm {Minimum_Area} \ #D CONFIG.Primitive {8kx2} \ #E CONFIG.Write_Width_A {34} \ #F CONFIG.Read_Width_A {34} \ #G CONFIG.Write_Depth_A {10081} \ #H ## 此属性只用配置这一个 则A的读深度和B的读写深度都确定了 CONFIG.Operating_Mode_A {READ_FIRST} \ #I CONFIG.Enable_A {Use_ENA_Pin} \ #J CONFIG.Register_PortA_Output_of_Memory_Core {false} \ #K CONFIG.Register_PortA_Output_of_Memory_Primitives {false} \ #L CONFIG.Use_RSTA_Pin {false} \ #M CONFIG.Output_Reset_Value_A {0} \ #N CONFIG.Load_Init_File {true} \ #O CONFIG.Coe_File {d:/proj_workspace/tcl_bram/src/ckbd_rom_18pattern.coe} \ #P ] [get_ips blkm] - 下列为一般方法添加 IP 的步骤,参数设置与 TCL 代码一一对应

- IP BRAM 添加完成

411

411

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?