笔记三是简单介绍ROM IP核的使用,ROM是只读存储器,它是将已经存储的好的数据读取出来,读取的文件格式是coe文件,本次笔记是按照顺序地址读取数据。

1.coe文件的生成

利用MATLAB将余弦波波形数据转换成coe格式

%% 生成正弦或余弦函数的coe文件

clear all ; % 清除变量

clc ; % 清屏

N = 4096 ; % 数据深度也就是数据点数

y = zeros(N , 1) ; % 生成N行1列的全为1的列向量

% 生成N行1列取值为cos(2*pi*x/N)的列向量

% 最大值为255,因此数据位宽为8bit,因为2^8=256

for i = 1:1:N

x = i ;

%y(i,1) = ceil( 127*sin(x*2*pi/N) ) + 127 ;

y(i,1) = ceil( 127*cos(x*2*pi/N) ) + 127 ;

end

plot(y); % 绘制图像

hold on; % 保留之前的图,实现多图共存

fid = fopen('cos_4096.coe','wt'); % 以写的形式创建文件,文件名为cos_4096.coe

% 文件格式保存为十进制,以换行隔开

fprintf( fid, 'MEMORY_INITIALIZATION_RADIX = 10;\n');

fprintf( fid, 'MEMORY_INITIALIZATION_VECTOR =\n');

% 将上面的cos值写入文件

for i = 1:1:N

fprintf(fid,'%d,\n',y(i,1));

end

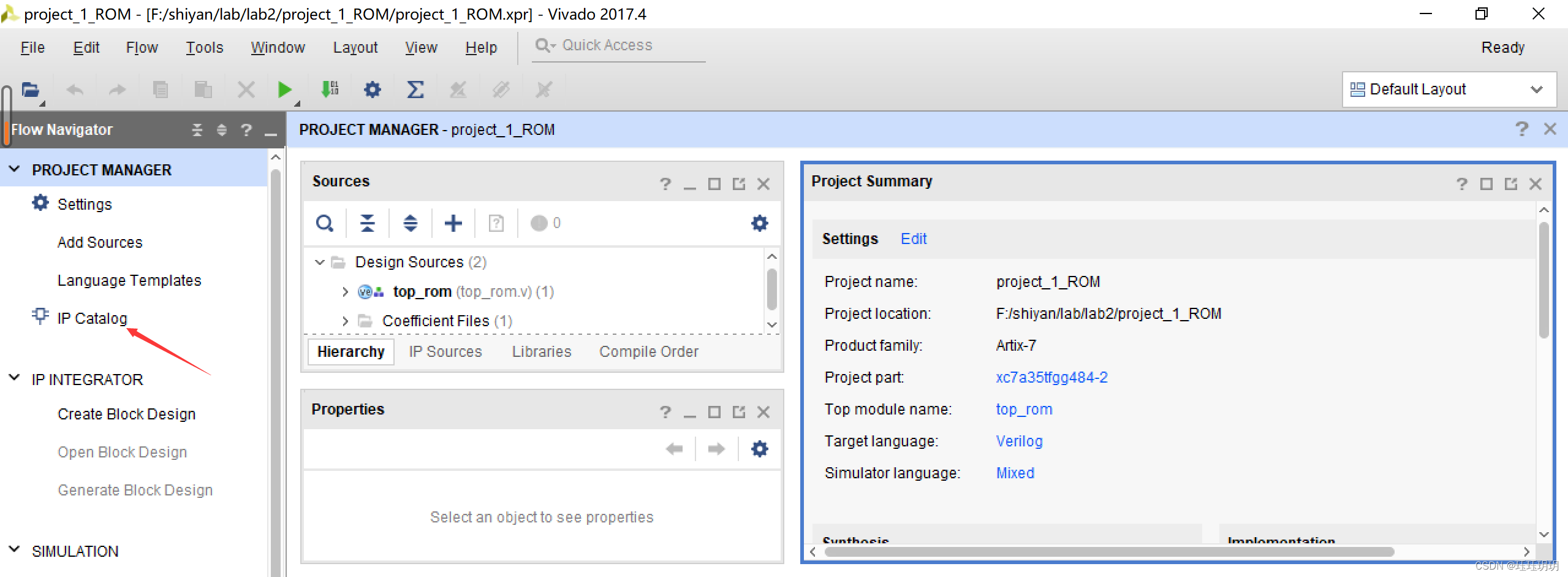

fclose(fid); % 关闭文件2.打开VIVADO,点击IP Catalog.

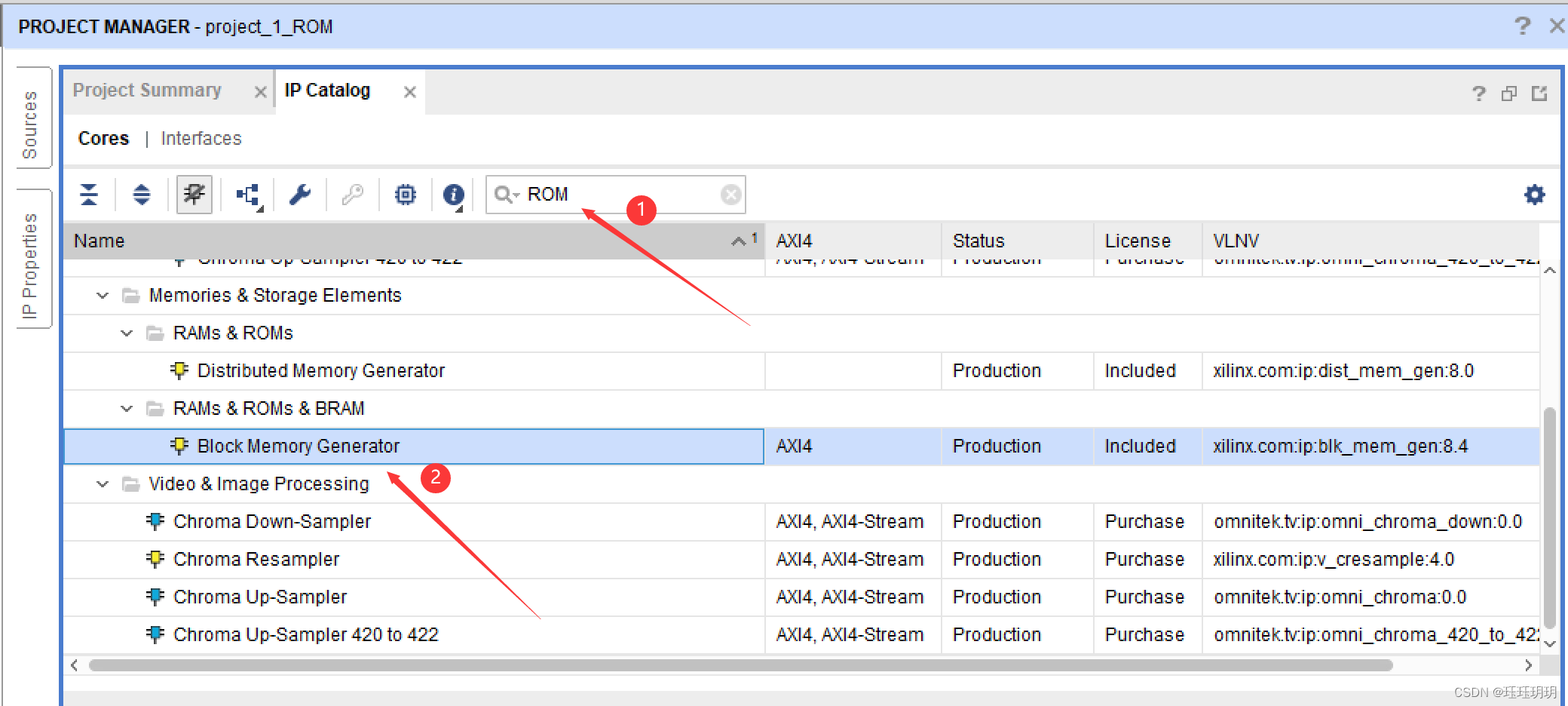

3.搜索ROM,选择Block Memory Generator

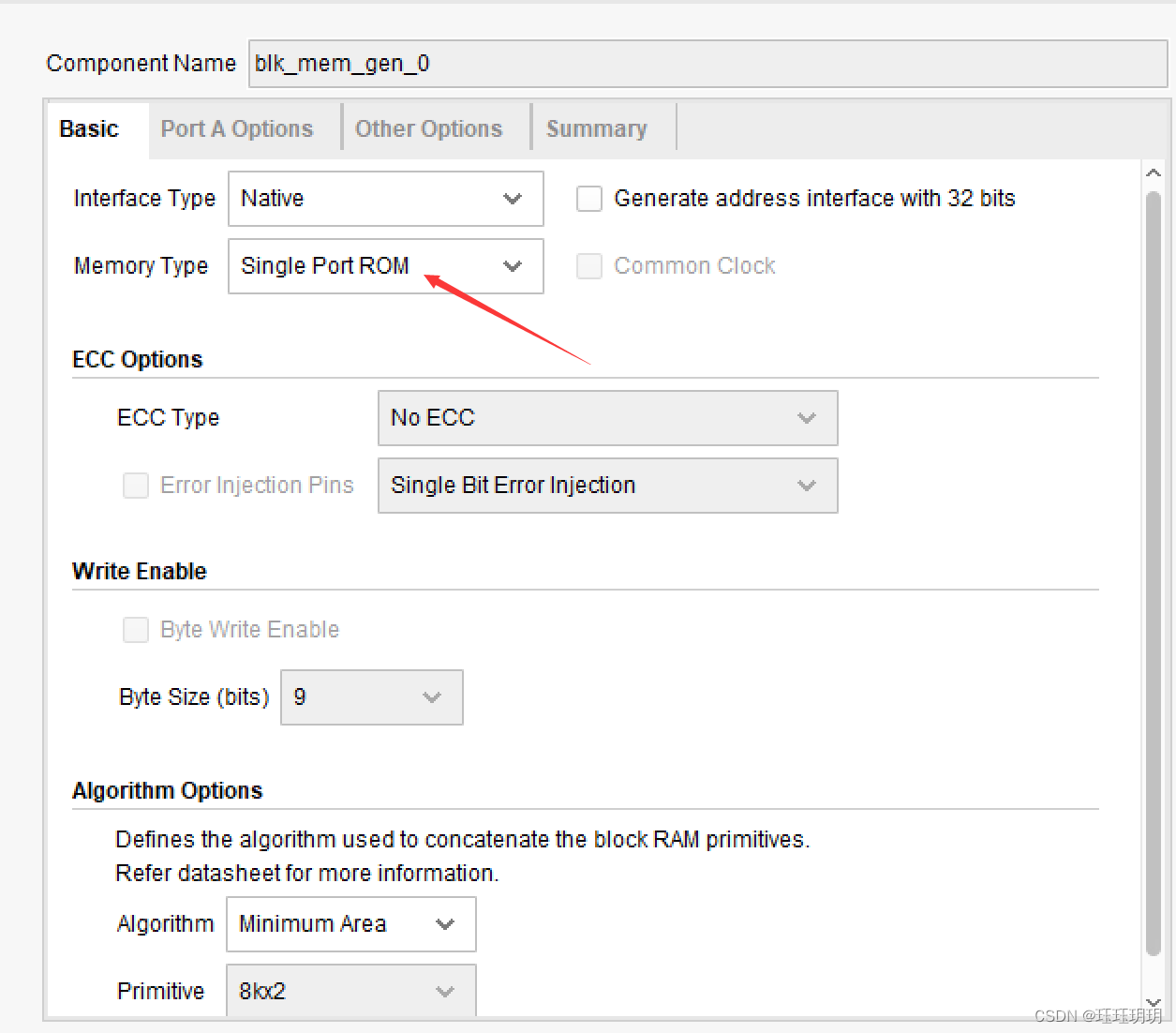

4. 参数配置

(1) 选择 Single Port ROM

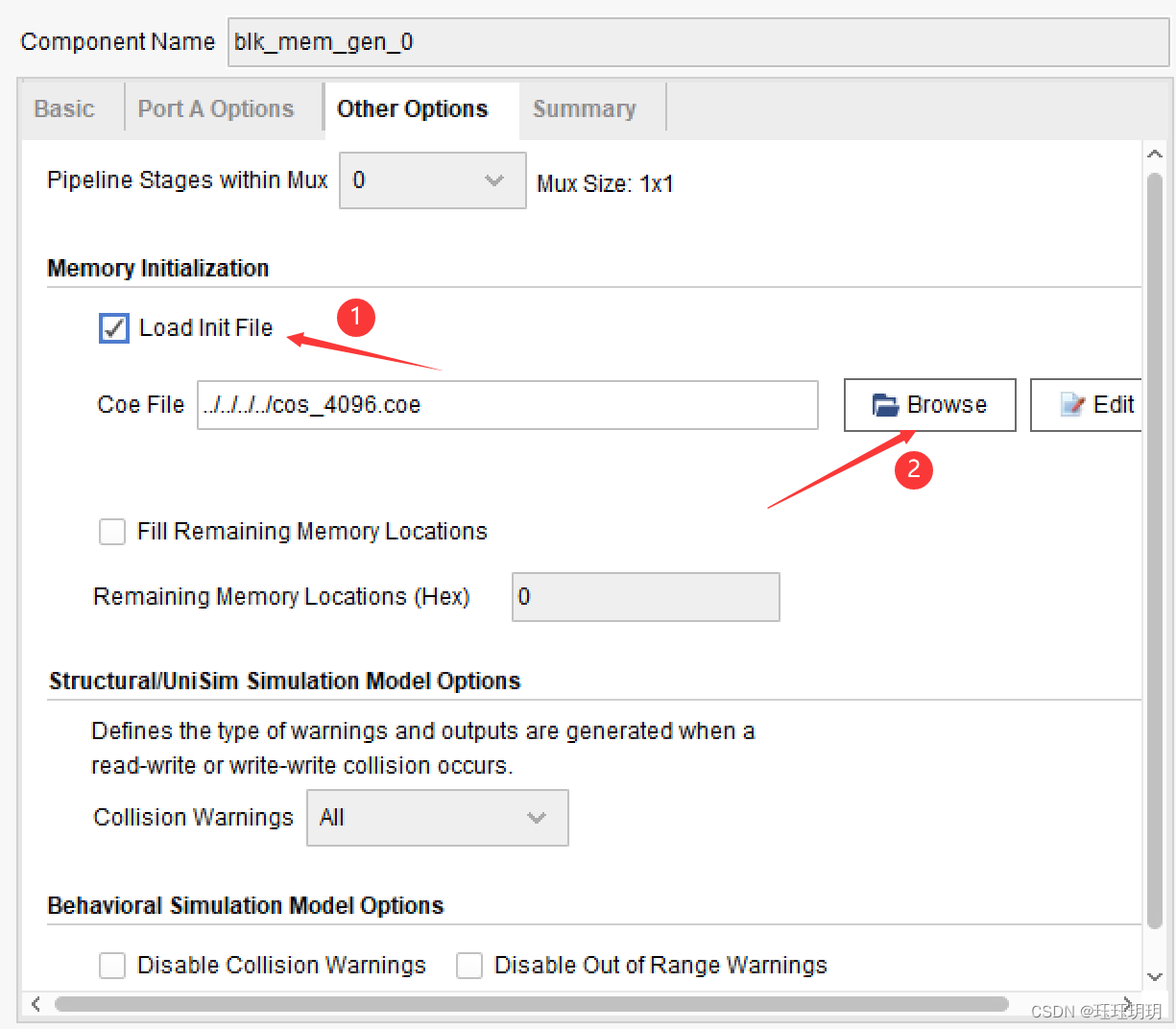

(2) 选择加载的coe文件的位宽和深度,据加载文件而定。

(3) 将coe文件加载进去

5.顶层文件

ROM IP核的输入是时钟clk,复位rst_n,使能信号ena_reg,还有地址addr_reg;在使能信号为高电平的时候读取数据,依据地址依次读取,如果改变地址顺序,读取的数据顺序也将改变。

module top_rom(

input clk, // 输入clk

input rst_n, // 输入复位

output [7:0] dout // 输出8位波形,数据宽度

);

reg ena_reg; // ROM使能信号

// 复位值为0时,使能信号为0,复位值为1时,使能信号为1

always@(posedge clk or negedge rst_n)

begin

if(~rst_n)

ena_reg <= 0;

else

ena_reg <= 1;

end

reg [11:0] addr_reg; // ROM的地址变量,4096数据深度,12bit

//地址变量从0开始增加到4095,然后又回到0,循环往复

//coe文件存储的4096个值对应4096个地址

always@(posedge clk or negedge rst_n)

begin

if(~rst_n)

addr_reg <= 12'd0;

else

addr_reg <= addr_reg + 1;

end

// ROM的例化

blk_mem_gen_0 U1 (

.clka(clk), // input wire clka

.addra(addr_reg), // input wire [11 : 0] addra

.ena(ena_reg),

.douta(dout) // output wire [7 : 0] douta

);

endmodule6.测试文件

module rom_tb();

reg clk; // 输入clk

reg rst_n; // 输入复位

wire [7:0] dout; // 输出8bit波形数据

// 顶层文件的例化

top_rom u0 (

.clk(clk),

.rst_n(rst_n),

.dout(dout)

);

initial // 初始化

begin

clk = 1; // 初始clk为高电平

rst_n = 0; // 复位为低电平

#50 // 延时50ns

rst_n = 1; // 复位为高电平

end

always #10 clk = ~clk; // clk周期为20ns

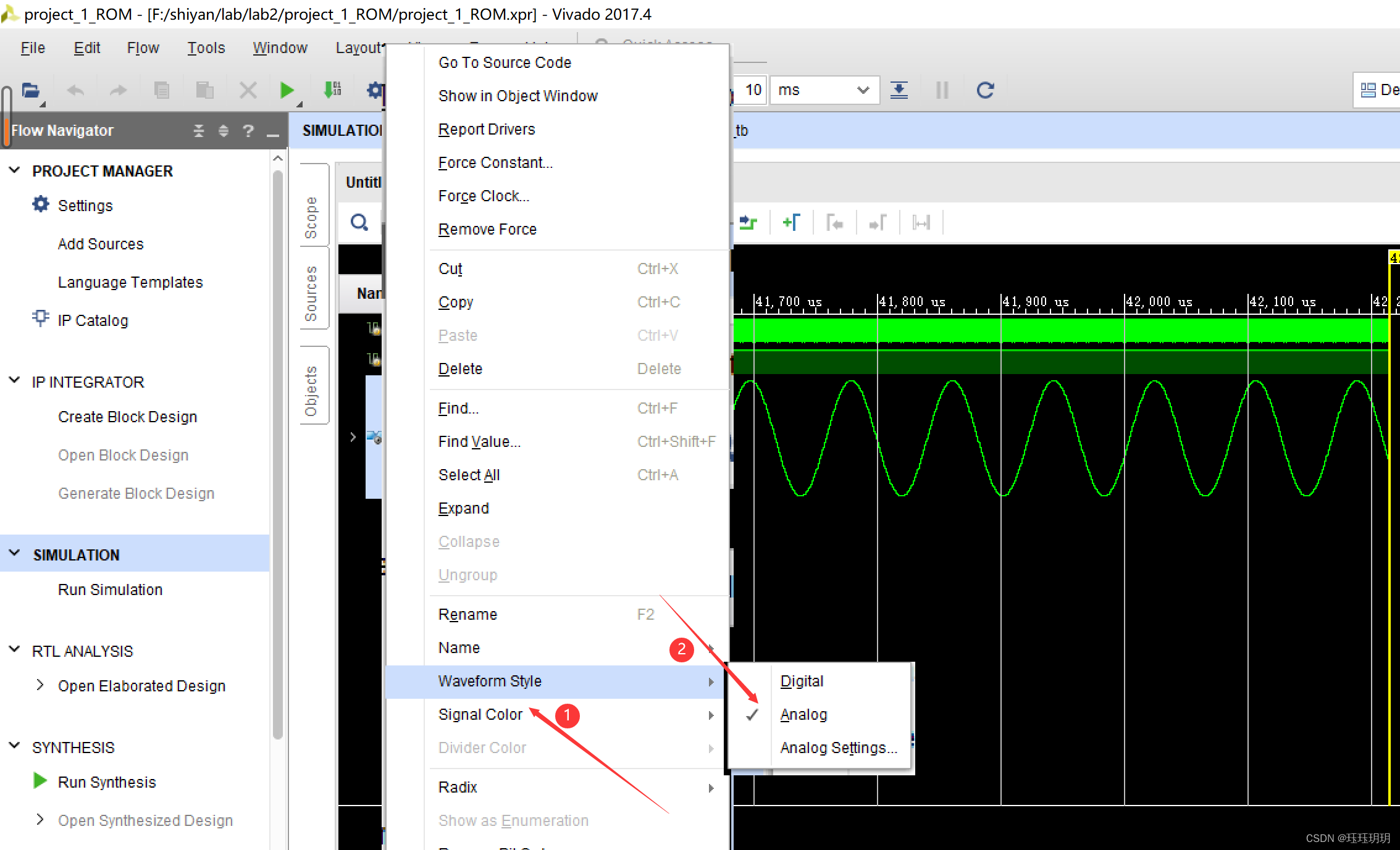

endmodule7. 成果展示

8.coe文件生成参考资料:(1条消息) 【FPGA】:matlab生成coe文件_夏凉秋落的博客-CSDN博客_matlab生成coe文件

940

940

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?