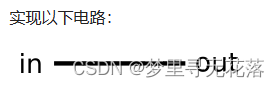

module top_module (

input in,

output out);

assign out = in;

endmodule

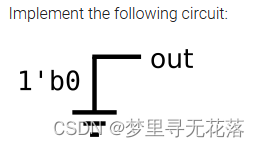

module top_module (

output out);

assign out = 1'b0;

endmodule

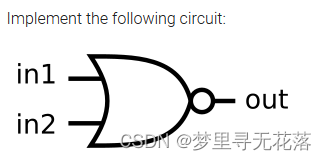

module top_module (

input in1,

input in2,

output out);

assign out = ~(in1||in2);

endmodule

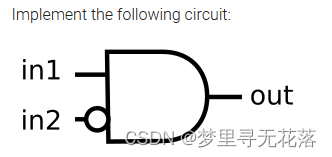

module top_module (

input in1,

input in2,

output out);

assign out = in1&&~in2;

endmodule

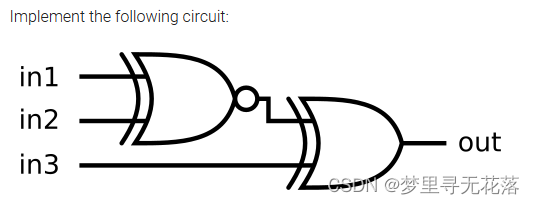

module top_module (

input in1,

input in2,

input in3,

output out);

assign out = (~(in1^in2)^in3);

endmodule

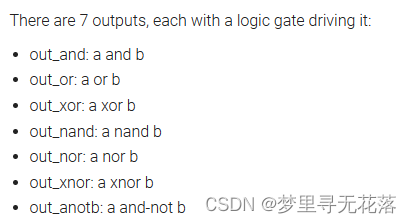

module top_module(

input a, b,

output out_and,

output out_or,

output out_xor,

output out_nand,

output out_nor,

output out_xnor,

output out_anotb

);

assign out_and = a&&b;

assign out_or = a||b;

assign out_xor = a^b;

assign out_nand = ~(a&b);

assign out_nor = ~(a|b);

assign out_xnor = ~(a^b);

assign out_anotb = a&(~b);

endmodule

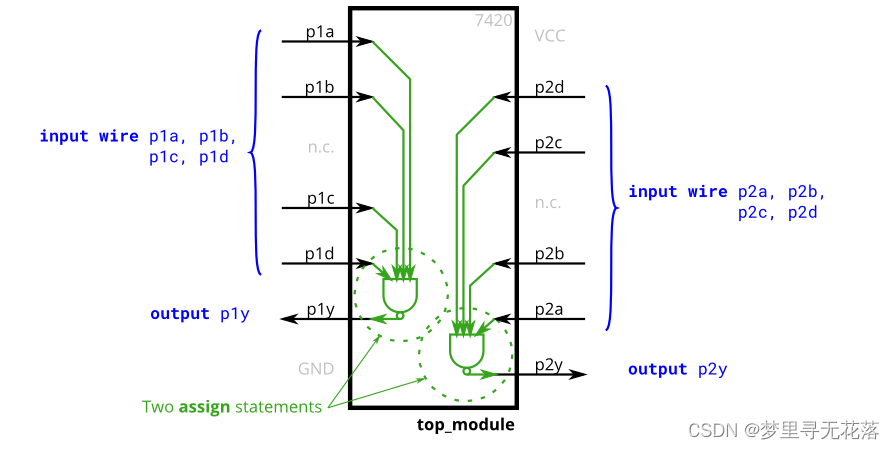

module top_module (

input p1a, p1b, p1c, p1d,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y = ~(p1a&p1b&p1c&p1d);

assign p2y = ~(p2a&p2b&p2c&p2d);

endmodule

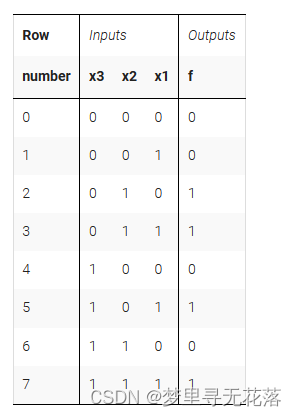

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);

assign f = (x2&~x3)|(x1&x3);

endmodule

创建一个具有两个 2 位输入 A[1:0] 和 B[1:0] 的电路,并产生一个输出 z。如果 A = B,则 z 的值应为 1,否则 z 应为 0。

module top_module ( input [1:0] A, input [1:0] B, output z );

assign z = (A===B)?1:0;

endmodule

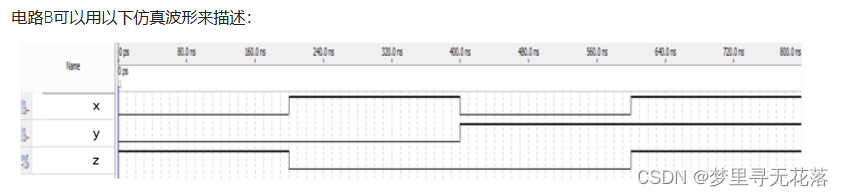

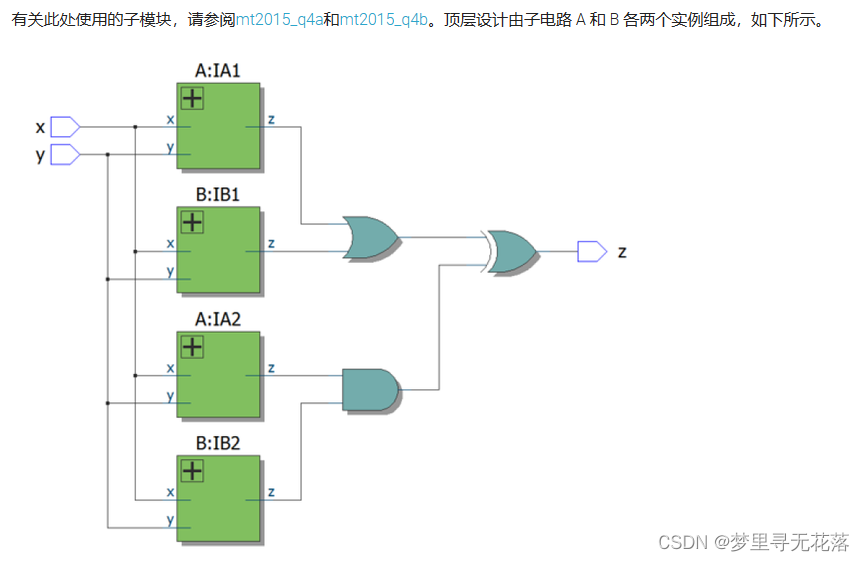

模块 A 应该实现函数 z = (x^y) & x。实现此模块。

module top_module (input x, input y, output z);

assign z = (x^y)&x;

endmodule

module top_module ( input x, input y, output z );

assign z = ~(x^y);

endmodule

module top_module (input x, input y, output z);

wire z1,z2;

assign z1 = (x^y)&x;

assign z2 = ~(x^y);

assign z = (z1|z2)^(z1&z2);

endmodule

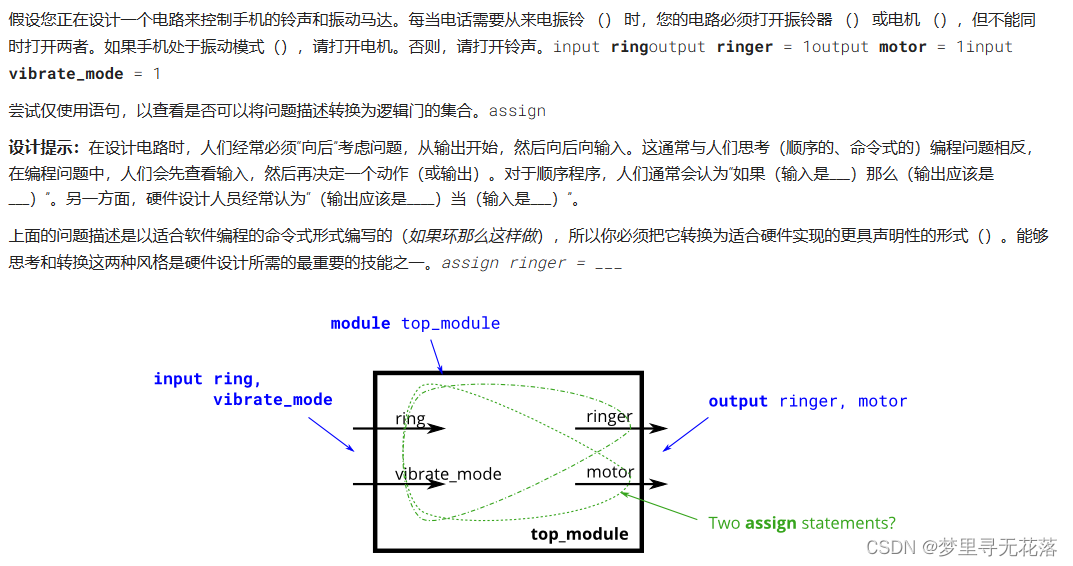

module top_module (

input ring,

input vibrate_mode,

output ringer, // Make sound

output motor // Vibrate

);

assign ringer = (ring&&(~vibrate_mode))?1:0;

assign motor = ((ring)&&(vibrate_mode))?1:0;

endmodule

加热/冷却恒温器控制加热器(冬季)和空调(夏季)。实施一个电路,该电路将根据需要打开和关闭加热器、空调和鼓风机风扇。

恒温器可以处于以下两种模式之一:加热 () 和冷却 ()。 在加热模式下,当太冷时打开加热器(),但不要使用空调。在冷却模式下,当空调过热时打开空调(),但不要打开加热器。当加热器或空调打开时,还要打开风扇以使空气循环。此外,即使加热器和空调关闭,用户也可以要求风扇打开()。mode = 1mode = 0too_cold = 1too_hot = 1fan_on = 1

尝试仅使用语句,以查看是否可以将问题描述转换为逻辑门的集合。assign

module top_module (

input too_cold,

input too_hot,

input mode,

input fan_on,

output heater,

output aircon,

output fan

);

assign heater = (too_cold&(mode))?1:0;

assign aircon = (too_hot&(~mode))?1:0;

assign fan = fan_on|heater|aircon;

endmodule

“总体计数”电路对输入向量中的“1”数进行计数。为3位输入向量构建一个群体计数电路。

module top_module(

input [2:0] in,

output [1:0] out );

assign out = in[1]+in[2]+in[0];

endmodule

在 [3:0] 中为您提供一个四位输入向量。我们想知道每个比特与其邻居之间的一些关系:

out_both:此输出向量的每个位都应指示相应的输入位及其左侧的相邻位(较高索引)是否为“1”。例如,out_both[2] 应指示 in[2] 和 in[3] 是否都是 1。由于in[3]的左边没有邻居,答案是显而易见的,所以我们不需要知道out_both[3]。

out_any:此输出向量的每个位都应指示是否有任何相应的输入位及其右侧的邻居为“1”。例如,out_any[2] 应指示 in[2] 或 in[1] 是 1。由于 in[0] 右边没有邻居,答案很明显,所以我们不需要知道 out_any[0]。

out_different:此输出向量的每个位都应指示相应的输入位是否与其左侧的相邻位不同。例如,out_different[2] 应指示 in[2] 是否与 in[3] 不同。对于这部分,将向量视为环绕,因此 in[3] 左侧的邻居在 [0] 中。

module top_module(

input [3:0] in,

output [2:0] out_both,

output [3:1] out_any,

output [3:0] out_different );

assign out_both[0] = in[1] & in[0] ;

assign out_both[1] = in[2] & in[1] ;

assign out_both[2] = in[3] & in[2] ;

assign out_any[1] = in[1] | in[0] ;

assign out_any[2] = in[2] | in[1] ;

assign out_any[3] = in[3] | in[2] ;

assign out_different[0] = in[0] ^ in[1] ;

assign out_different[1] = in[1] ^ in[2] ;

assign out_different[2] = in[2] ^ in[3] ;

assign out_different[3] = in[3] ^ in[0] ;

endmodule

您将获得 [99:0] 中的 100 位输入向量。我们想知道每个比特与其邻居之间的一些关系:

out_both:此输出向量的每个位都应指示相应的输入位及其左侧的相邻位是否为“1”。例如,out_both[98] 应该指示 in[98] 和 in[99] 是否都是 1。由于in[99]的左边没有邻居,答案是显而易见的,所以我们不需要知道out_both[99]。

out_any:此输出向量的每个位都应指示是否有任何相应的输入位及其右侧的邻居为“1”。例如,out_any[2] 应指示 in[2] 或 in[1] 是 1。由于 in[0] 右边没有邻居,答案很明显,所以我们不需要知道 out_any[0]。

out_different:此输出向量的每个位都应指示相应的输入位是否与其左侧的相邻位不同。例如,out_different[98] 应该指示 in[98] 是否与 in[99] 不同。对于这部分,将向量视为环绕,因此 in[99] 左侧的邻居在 in[0]。

module top_module(

input [99:0] in,

output [98:0] out_both,

output [99:1] out_any,

output [99:0] out_different );

integer i;

always@*

begin

for(i=0;i<=99;i=i+1)

begin

if(i<=98)

begin

out_both[i] = in[i]&in[i+1];

out_any[i+1] = in[i]|in[i+1];

out_different[i] = in[i]^in[i+1];

end

else

out_different[99] = in[99]^in[0];

end

end

endmodule

69

69

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?