这篇写一些高级CDR的架构原理

1.半速鉴相器

很明显,如过能用半速时钟替代全速时钟,这肯定是赚。另外,在高速场景下,(1)、高速时钟的相噪难以控制,(2)、高速时钟要组成时钟树,(3)、设计高速触发器。以上问题都不好搞,所以要设计半速架构

1.1半速BBPD

Ex1

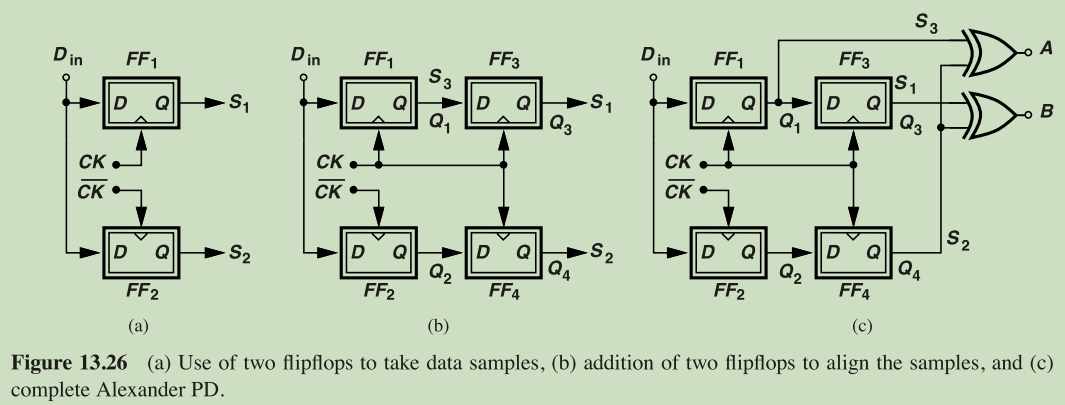

原先的半速亚历山大鉴相器,能否直接在半速时钟下工作?

答:很明显不大行,因为在原本的电路中,需要三个边沿工作,而现在变为半速时钟,直接少了一个采样点,所以很明显不行。

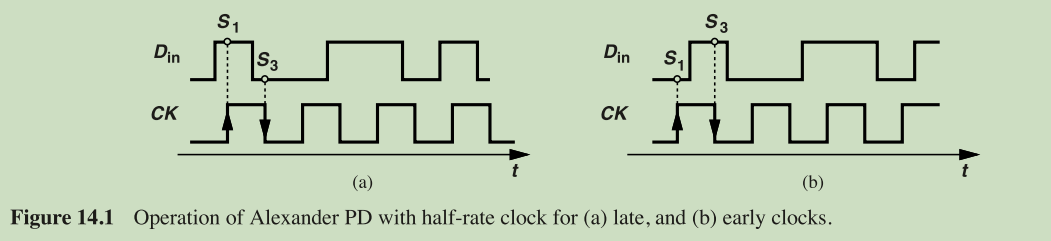

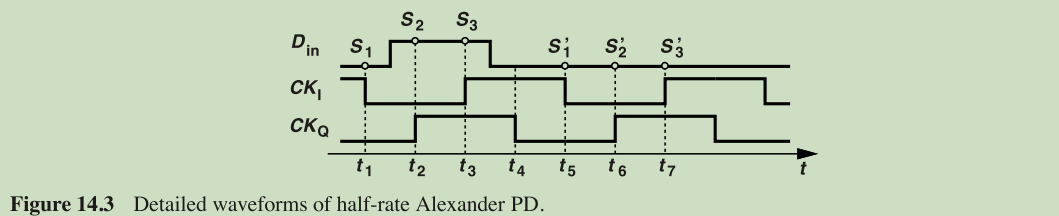

很明显,如果想在半速时钟下实现亚历山大结构,就需要一组正交时钟实现三点采样。

这里的FF1和FF3由互补的半速率时钟驱动,实际上充当了解复用器

EX2

图14.2(b)中的半速率相位检测器是否会清晰的采集每个数据边沿的信息?

答:并不会,因为CKq的下降沿并不采集信息,所以会丢失Din的下降沿信息。

为了补充上面所分析出的,会丢失下降沿的问题,我们可以额外增加一个触发器,并直接由CKq驱动,并做互补运算,如下图所示

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4191

4191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?