一、目的:

1、掌握Cadence Virtuoso快捷键技巧,学会使用Cadence进行原理图设计、版图设计、原理图仿真。

2.实验使用AMI 0.6u C5N工艺,了解NCSU Cadence设计套件(NCSU_Analog_Parts库)的使用,学会使用自行设计的元件设计功能型器件。

3.实现芯片焊盘及版图布局设计。

二、步骤:

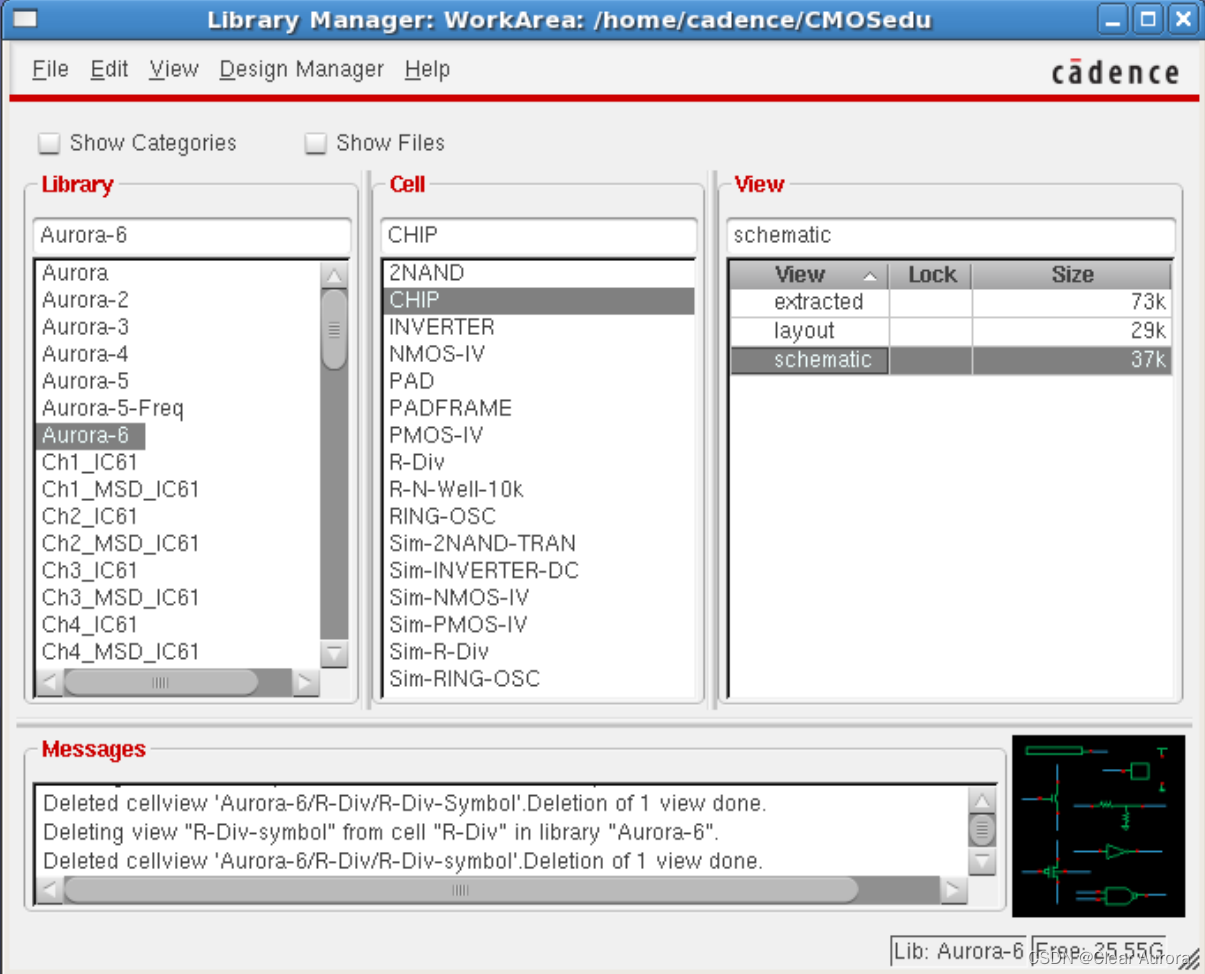

首先验证所设计的单一反相器的反应时间。在库管理器中添加一个库,为方便今后辨认,我添加的库名为Aurora-6,如图:

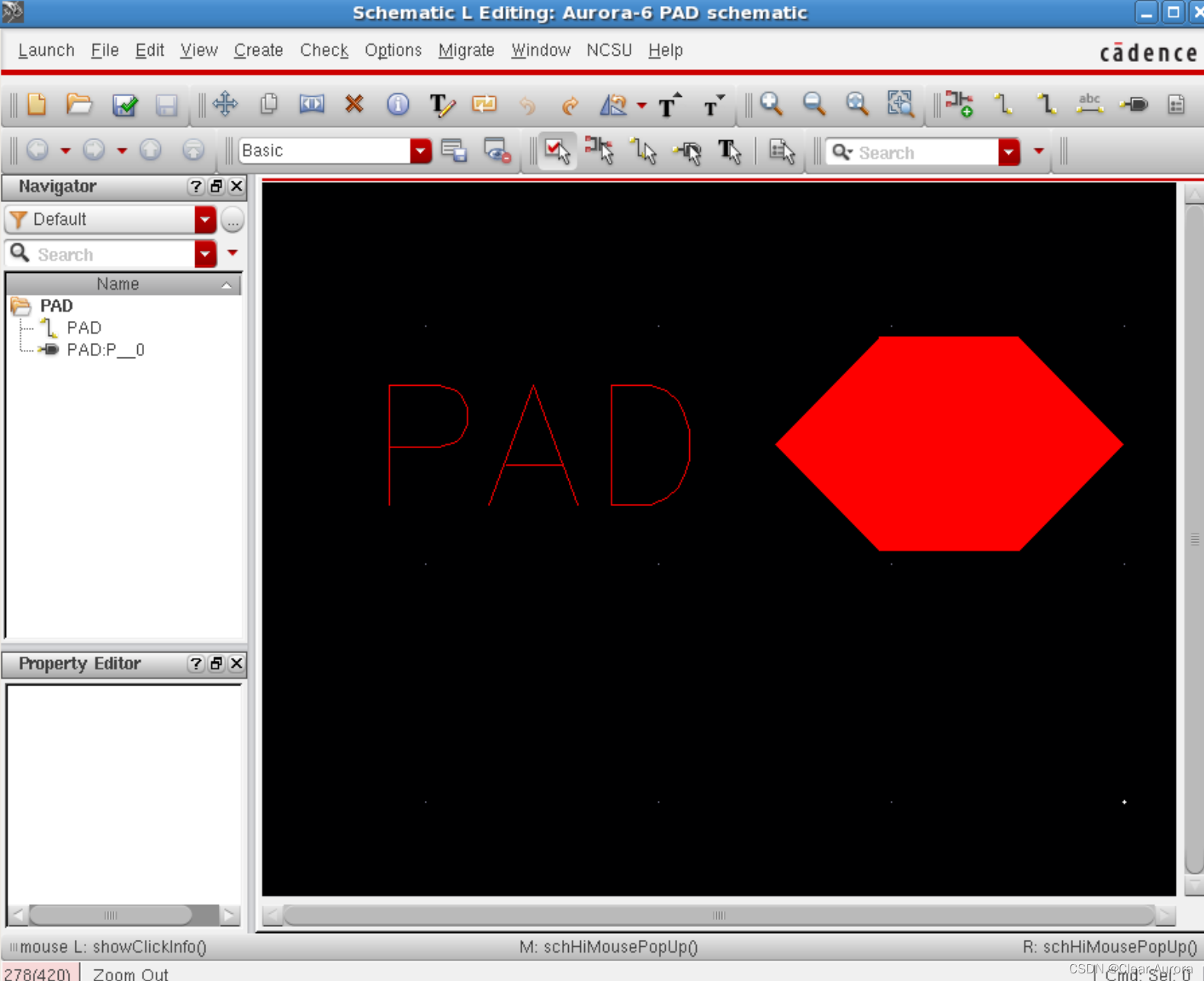

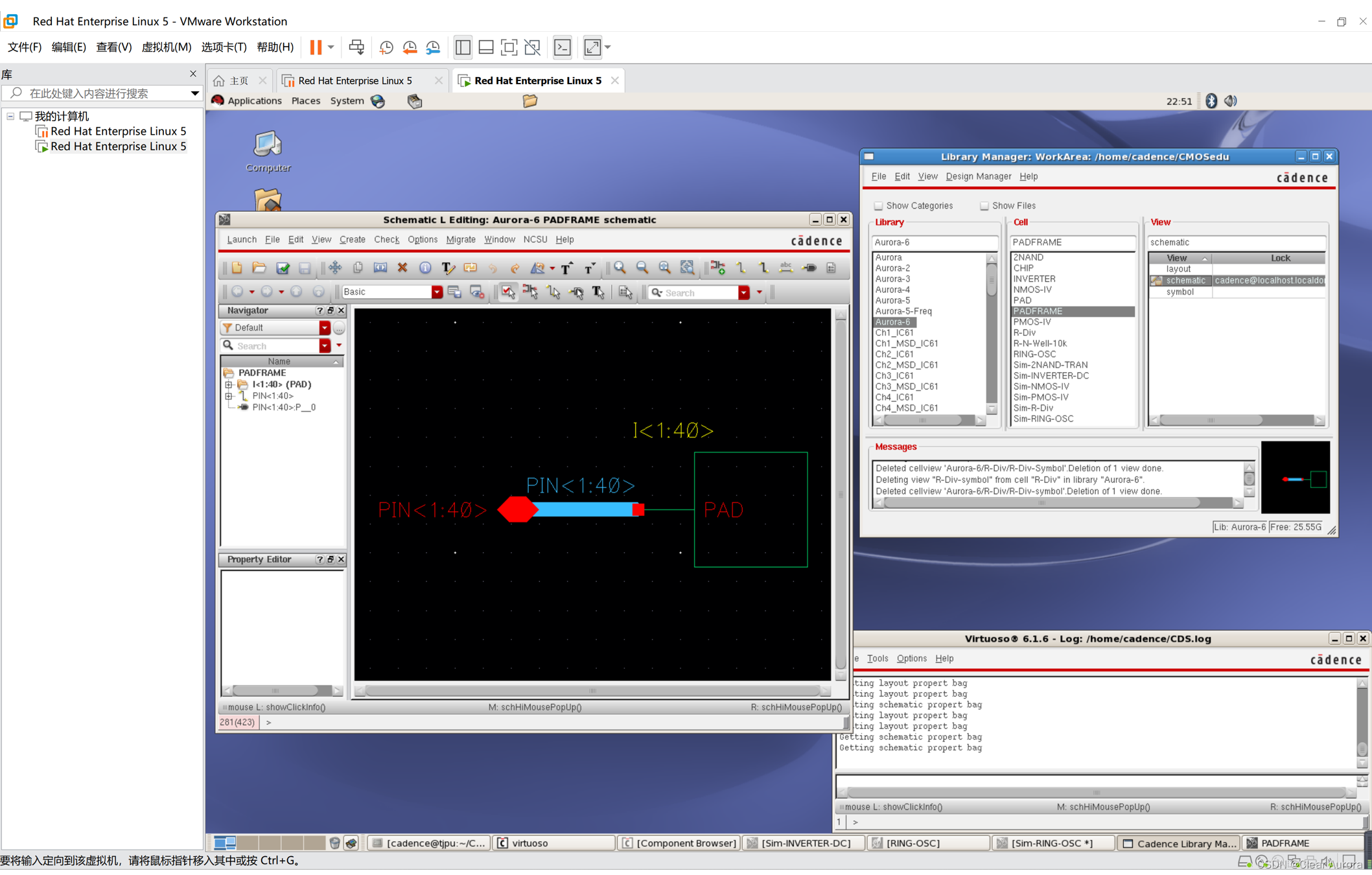

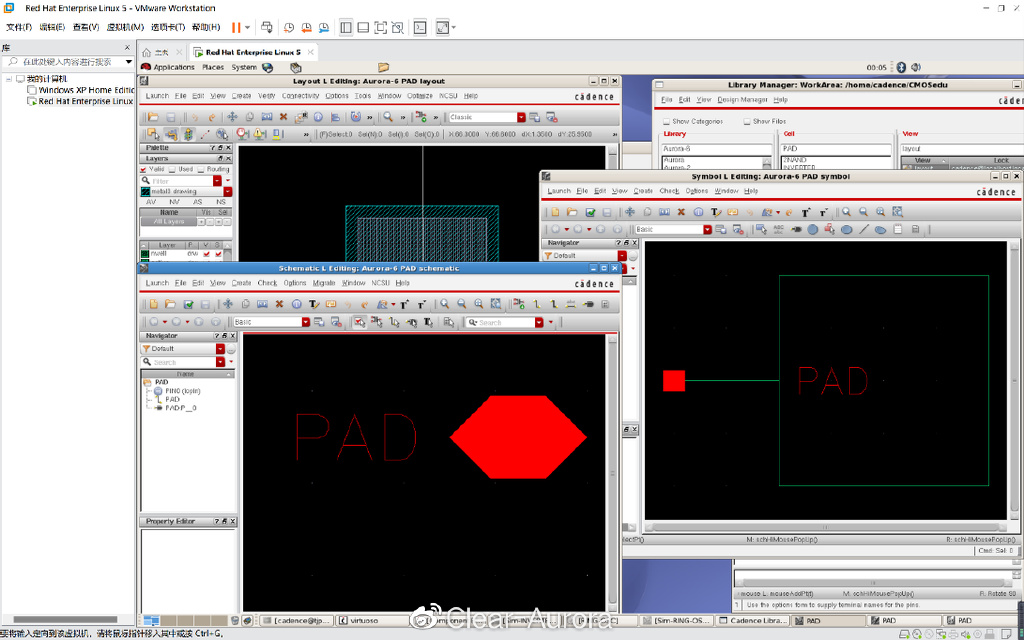

选择库管理器中的Aurora-6库,新建原理图,添加一个InputOutput引脚,绘制PAD原理图如图: 检查并保存”以后,进行PAD的Symbol绘制,在原理图界面选择Create—Cellview—From Cellview建立焊盘原理图的Symbol,绘制如下图:

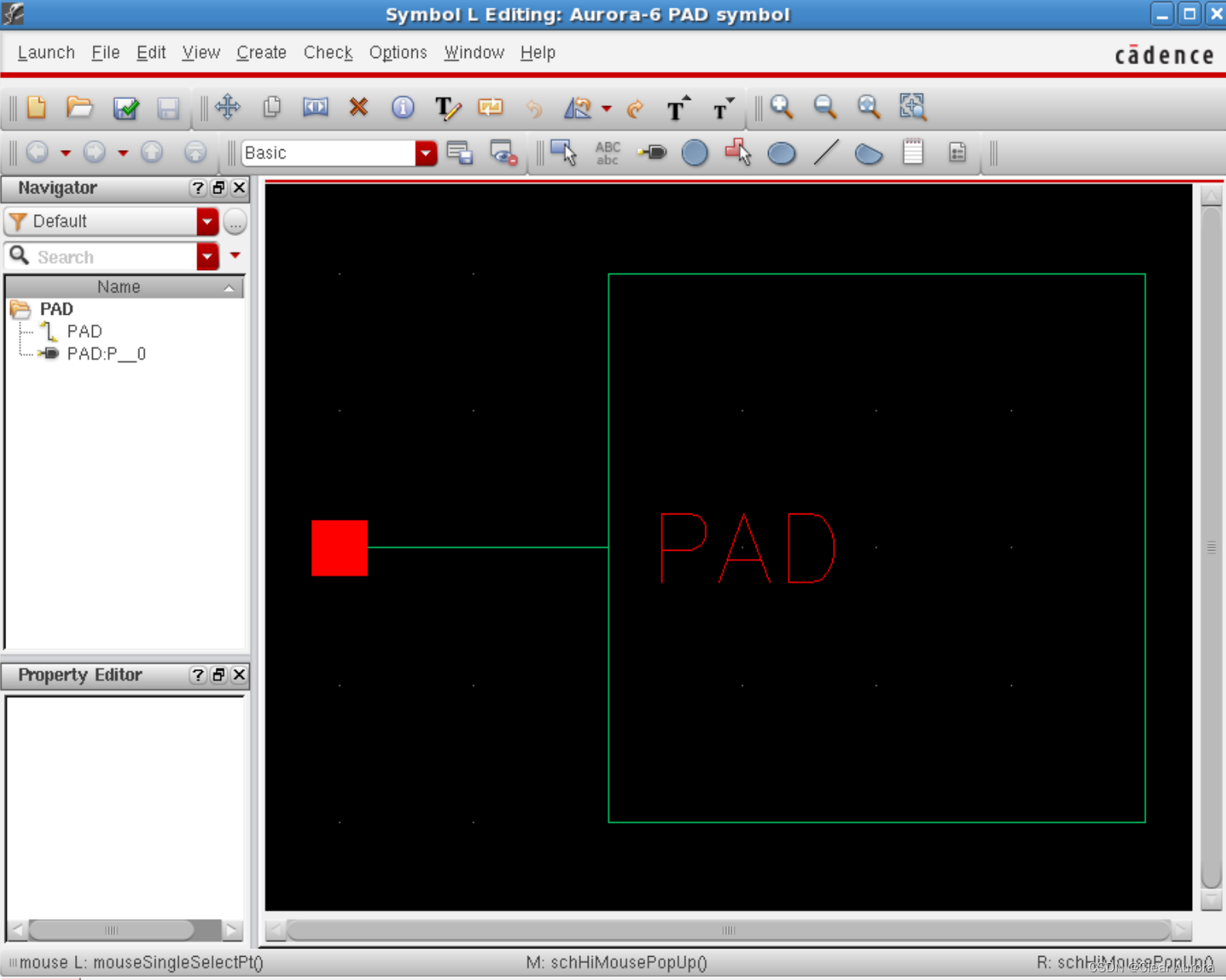

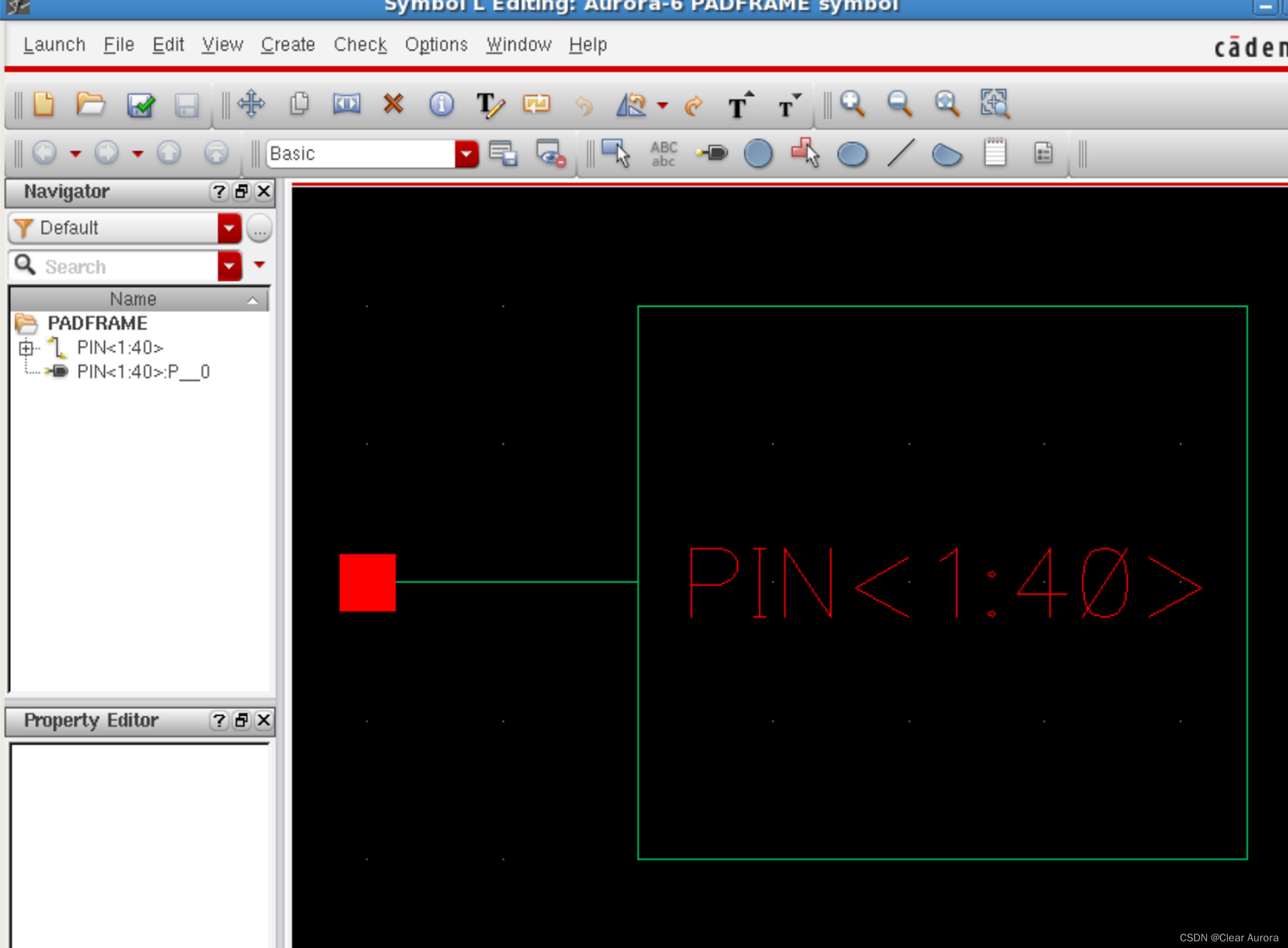

检查并保存”以后,进行PAD的Symbol绘制,在原理图界面选择Create—Cellview—From Cellview建立焊盘原理图的Symbol,绘制如下图:

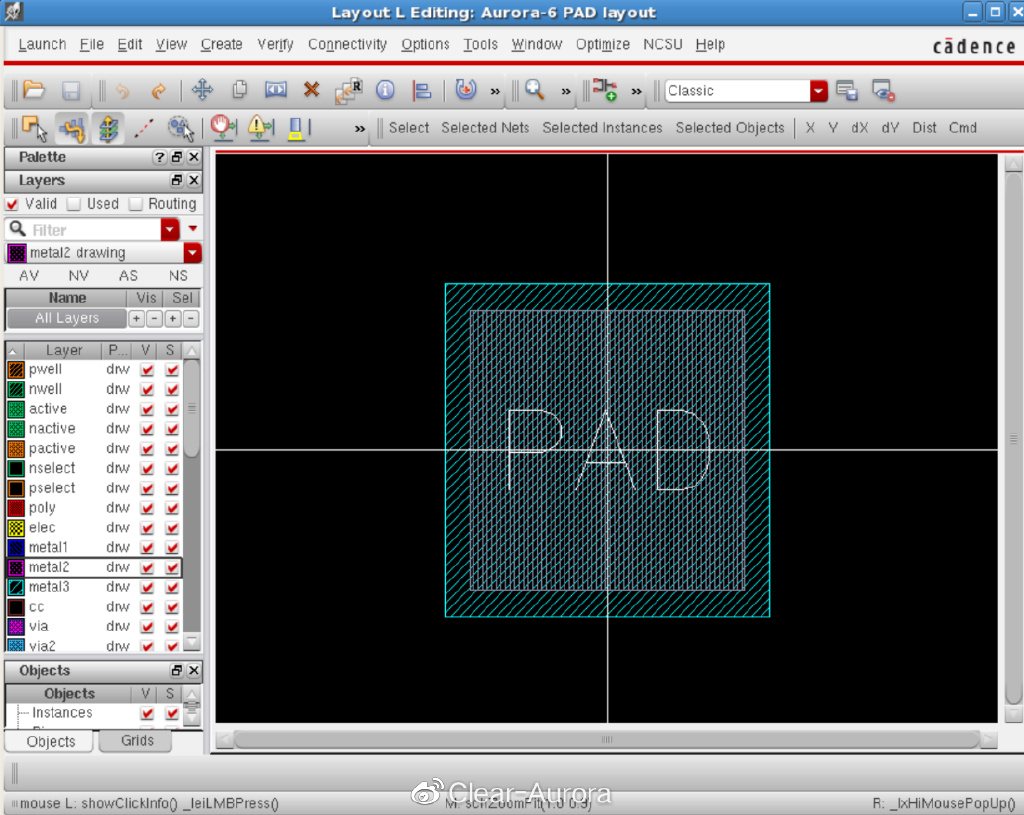

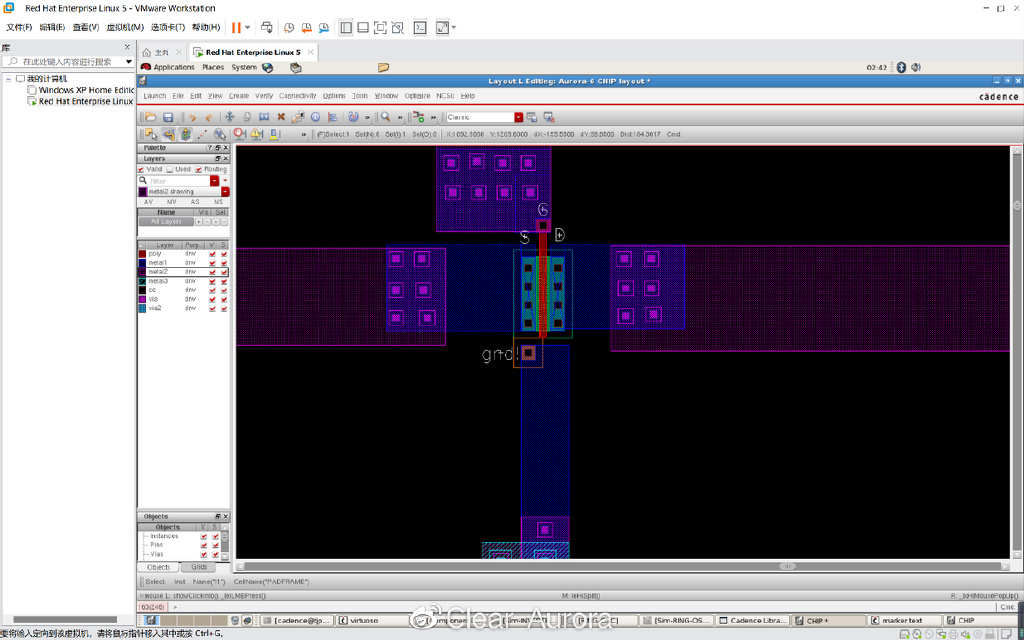

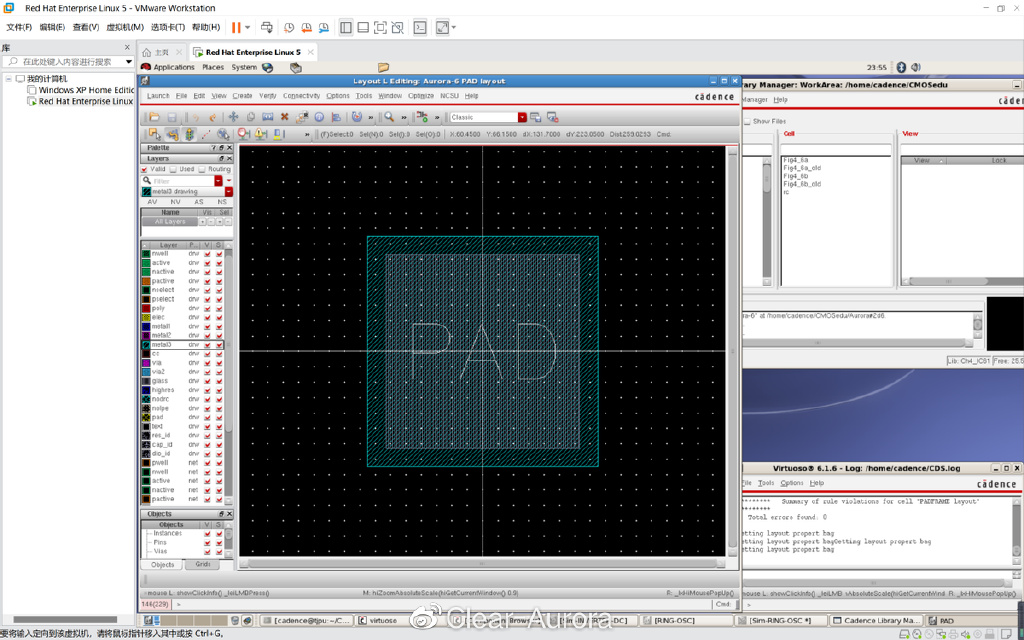

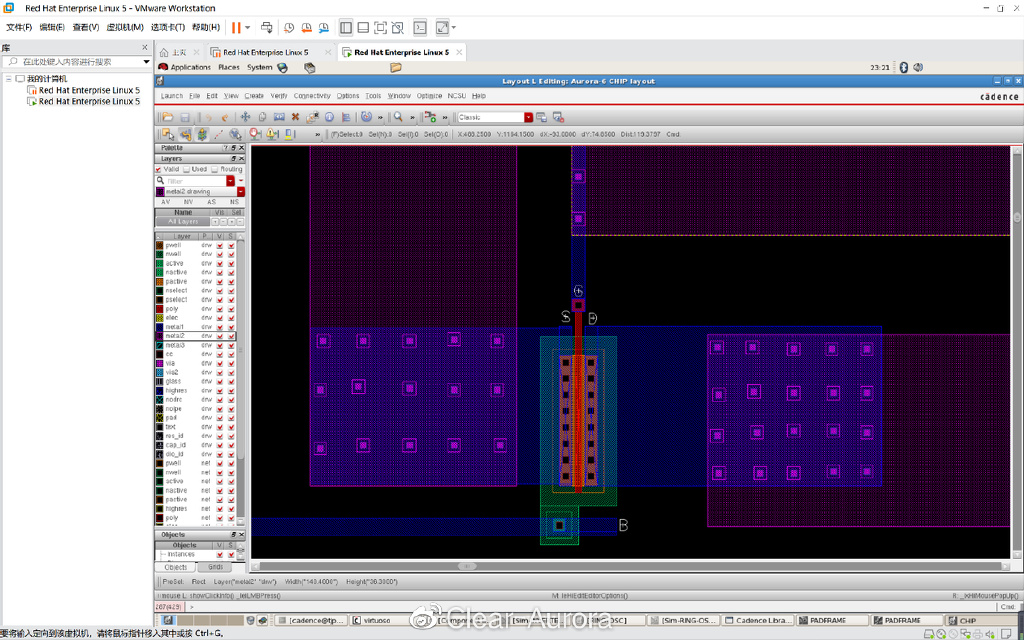

接下来进行焊盘的版图绘制,在Aurora-6库中新建一个Layout版图文件,绘制焊盘的版图,绘图布局时始终使用“drw”图层,绘制完成如下图所示:

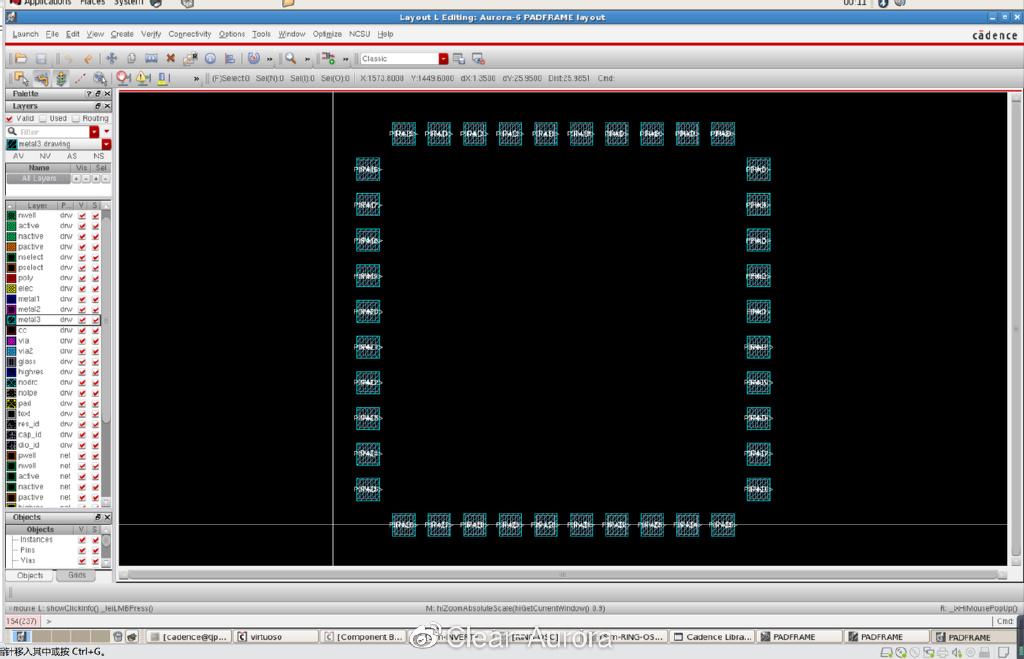

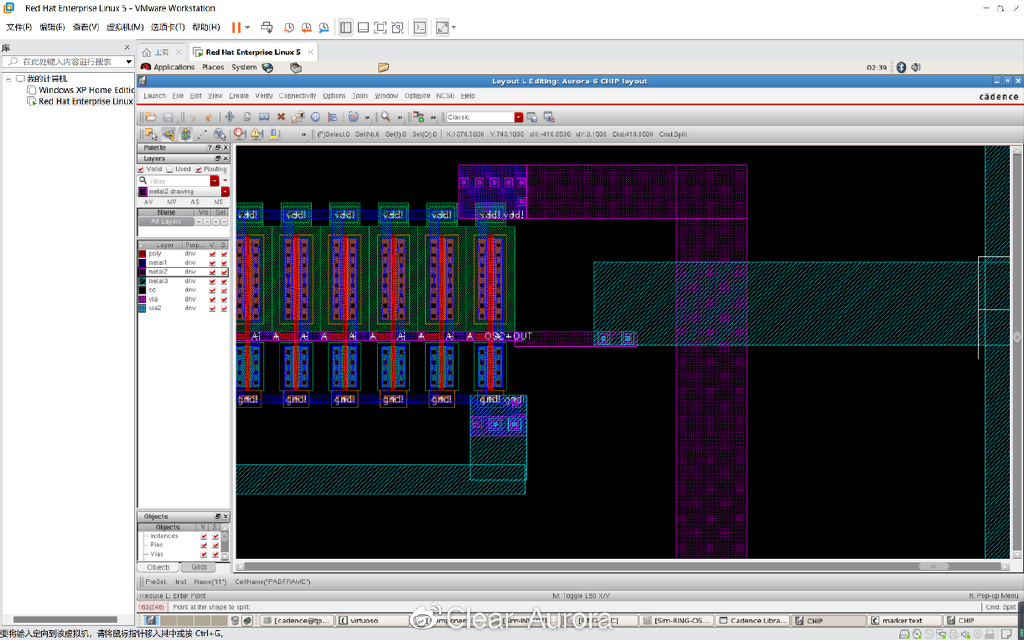

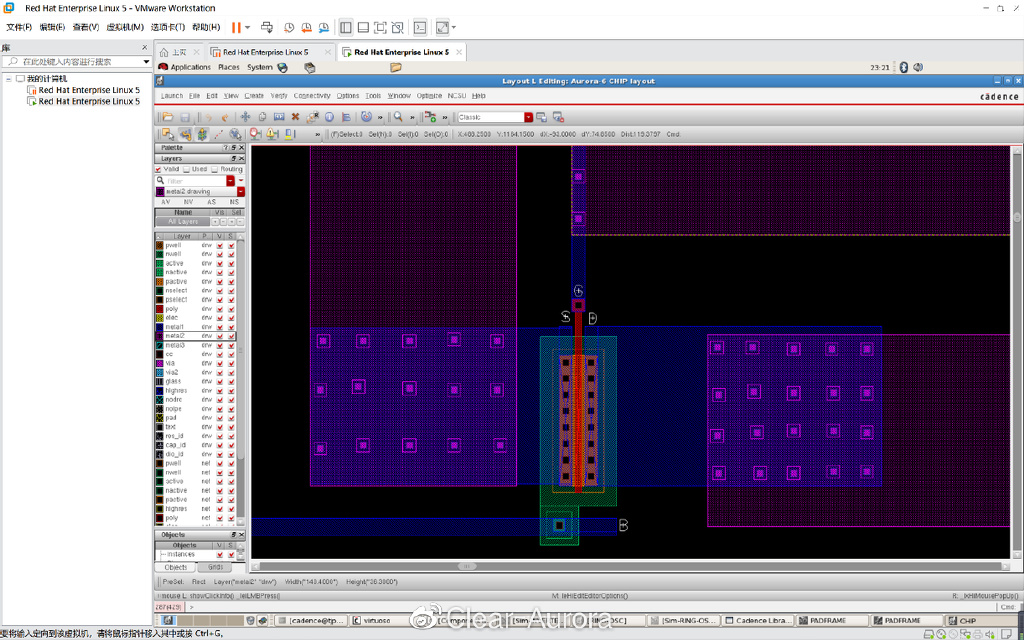

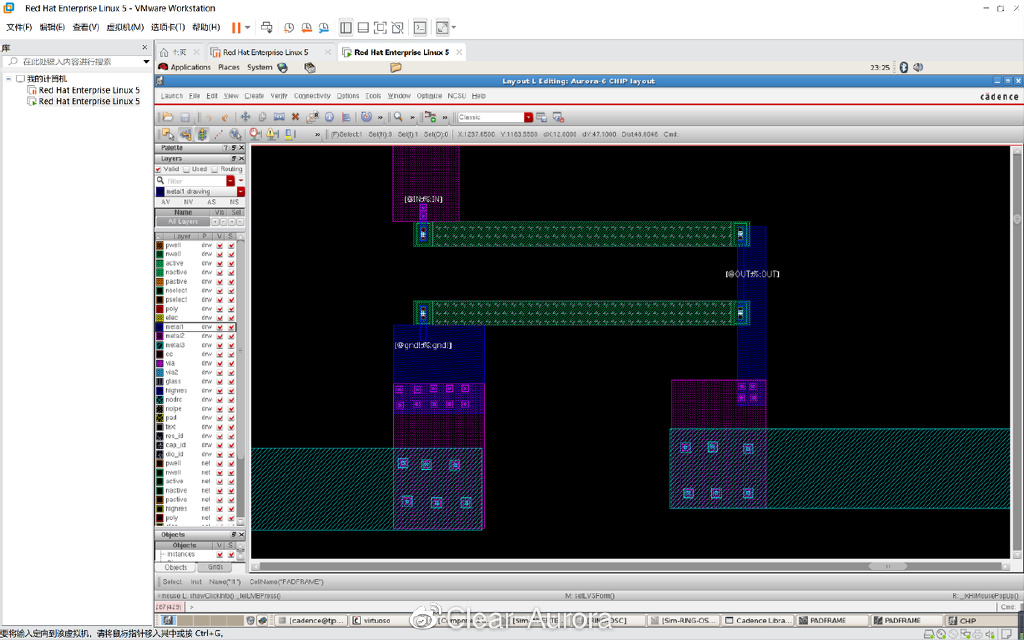

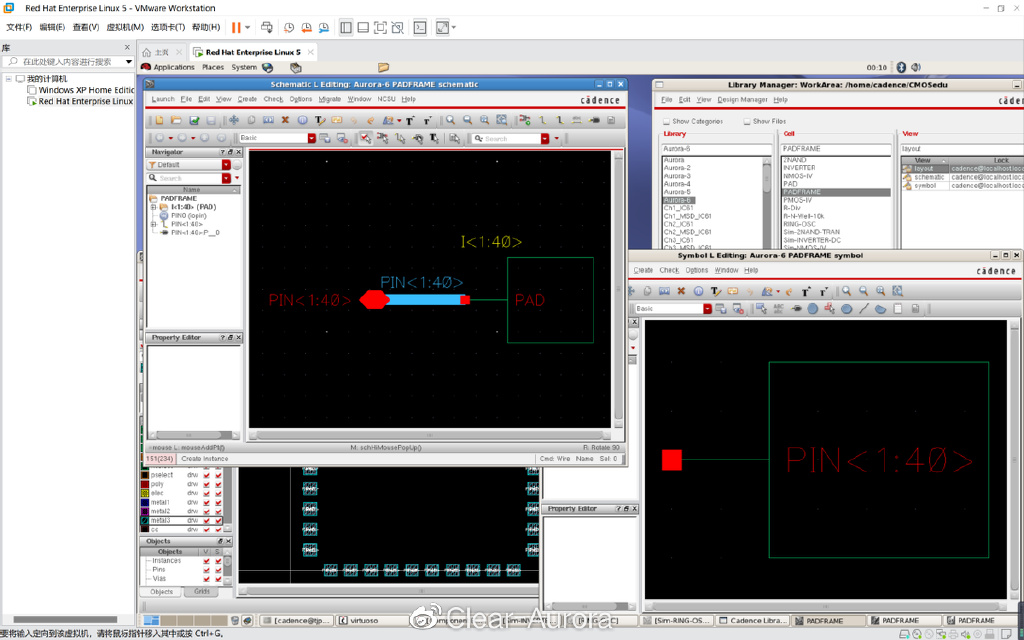

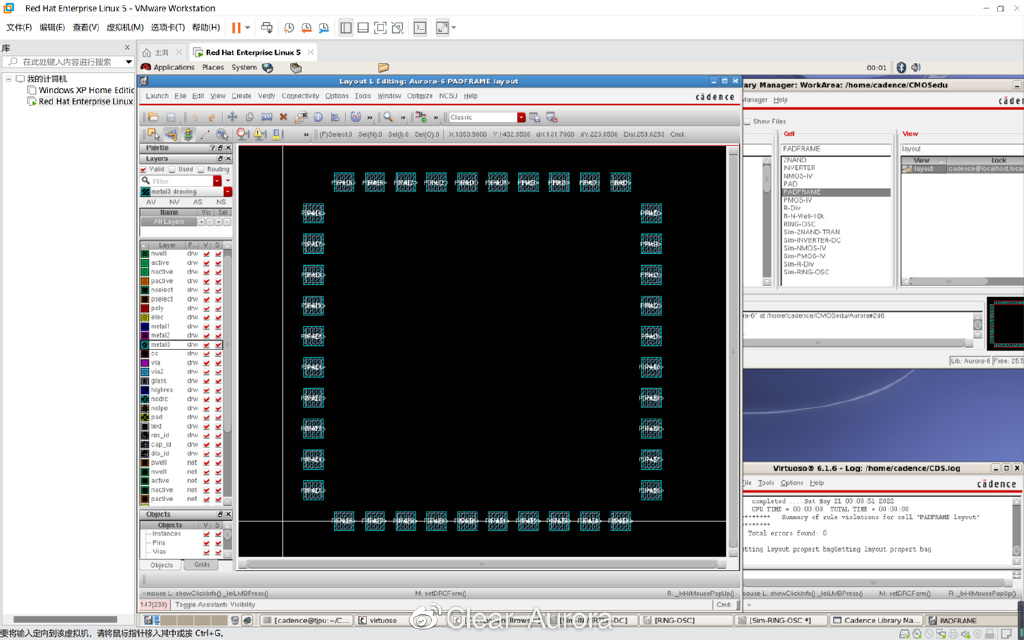

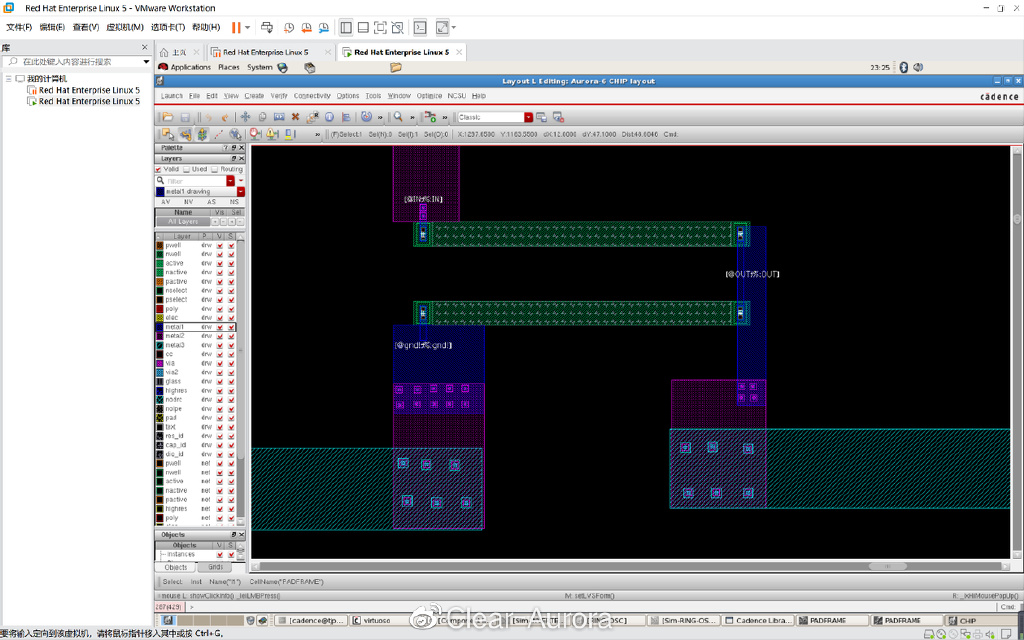

DRC焊盘版图无误后,根据要设计芯片的芯片手册,为芯片绘制所有引脚的焊盘(共40个):在Aurora-6库中建立PADFRAME,绘制芯片焊盘框架的原理图如图所示:

同样,绘制芯片焊盘框架的Symbol和版图布局Layout分别如下两图所示:

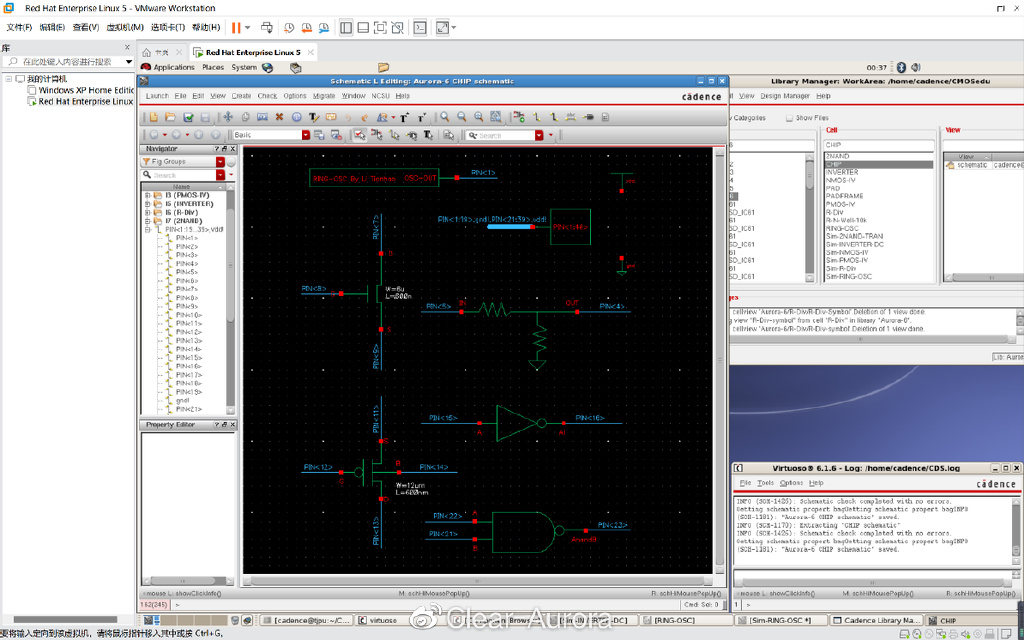

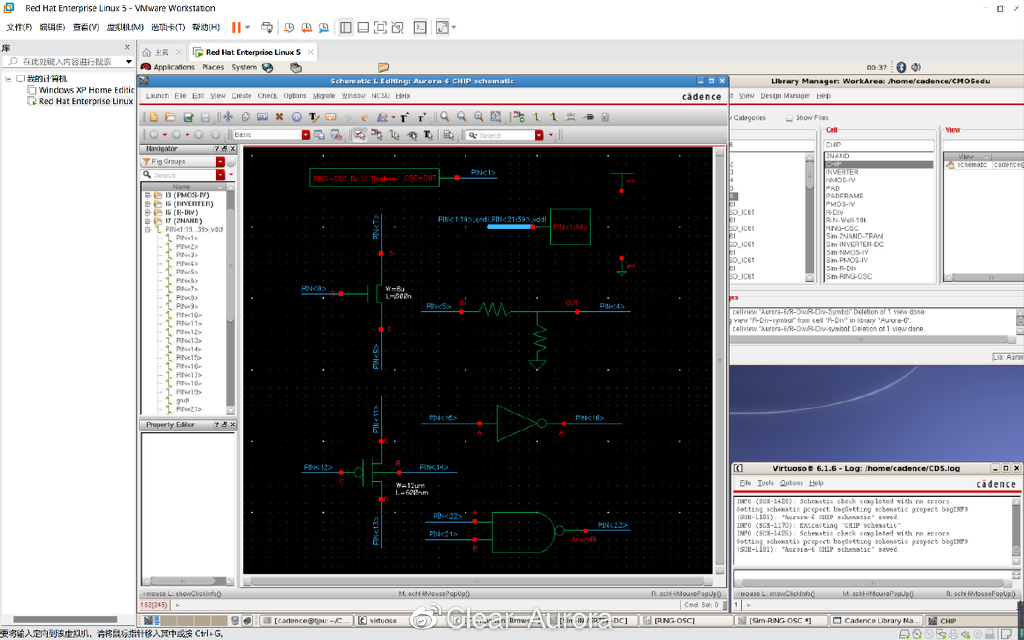

DRC芯片焊盘框架的版图后,根据所设计芯片的芯片手册要求绘制芯片原理图:在Aurora-6库中建立CHIP,从之前5次设计实验里已经设计好的库中选择芯片所需元件,绘制CHIP原理图如下图所示:

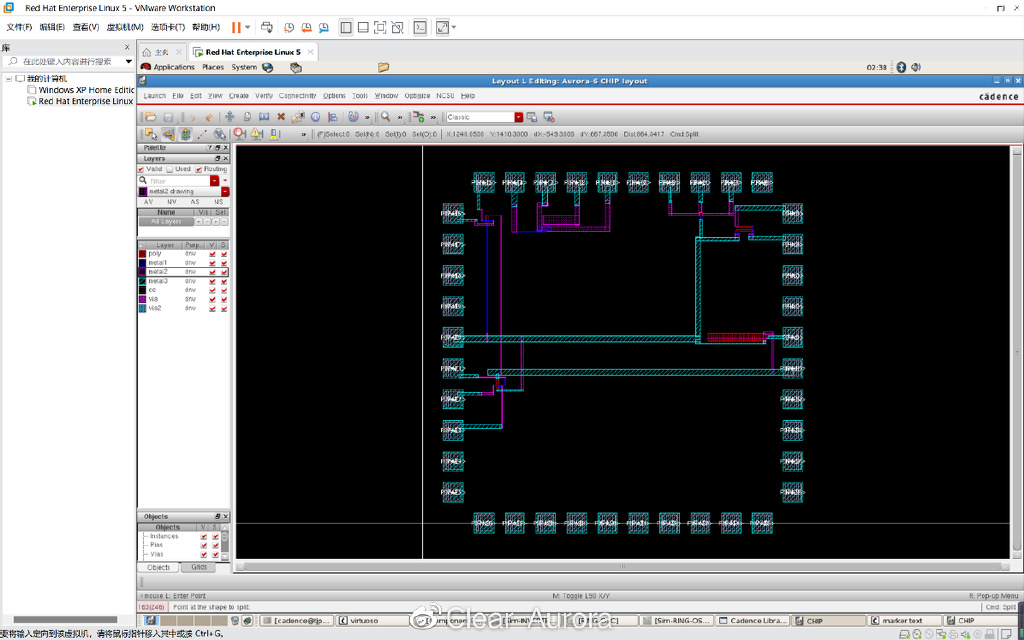

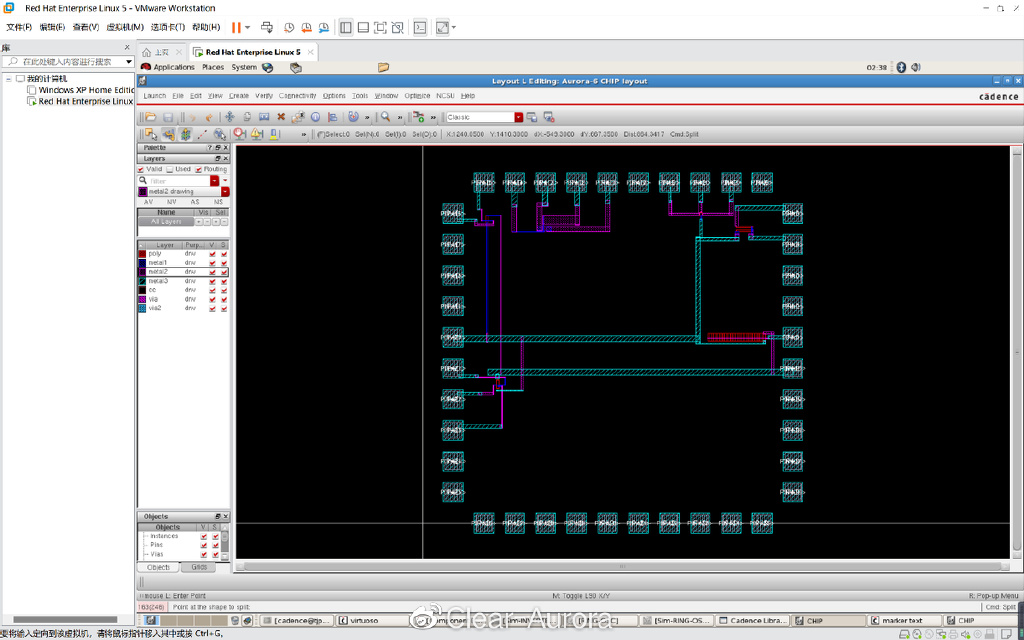

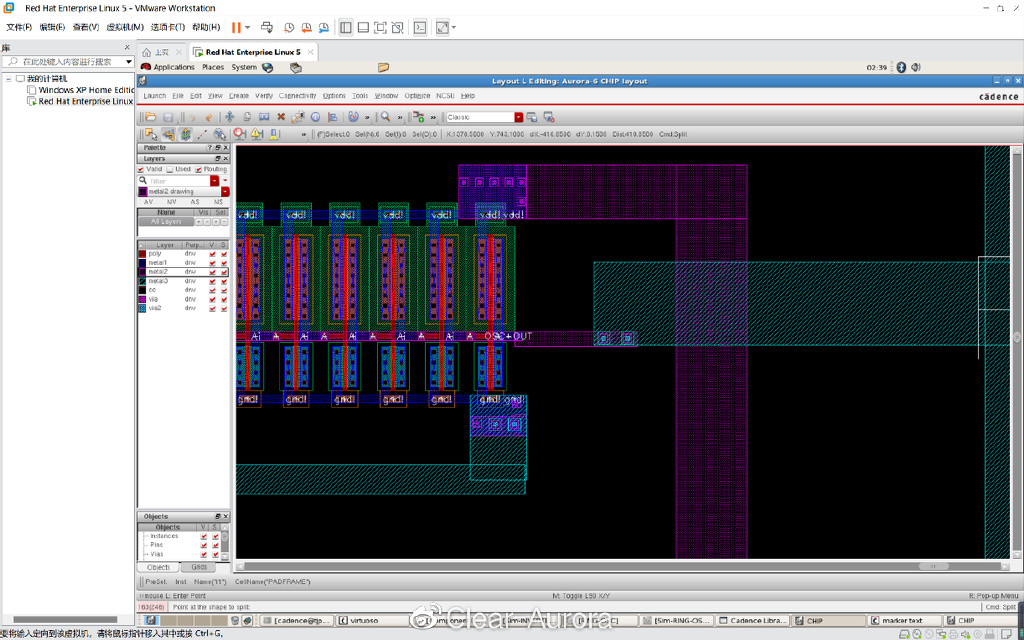

原理图检查无误并保存后,根据所设计芯片的芯片手册要求进行版图绘制,在Aurora-6库CHIP中新建一个Layout版图文件,绘制芯片版图,绘制完成如下图所示:

其中各元件与焊盘、VDD和GND的金属层具体连接如下:

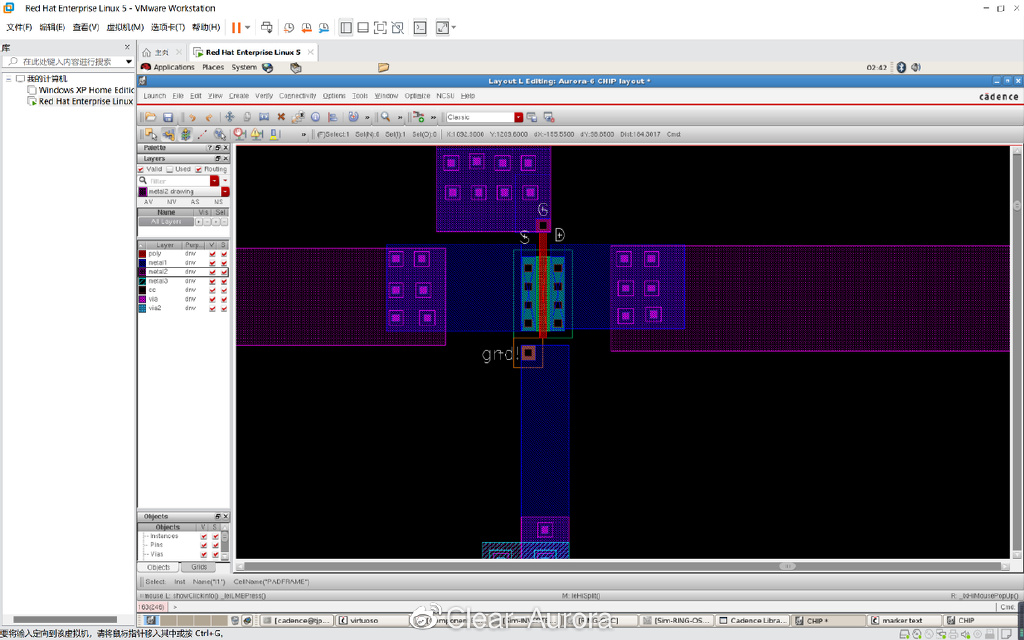

上图为环形振荡器输出端版图连接方式。

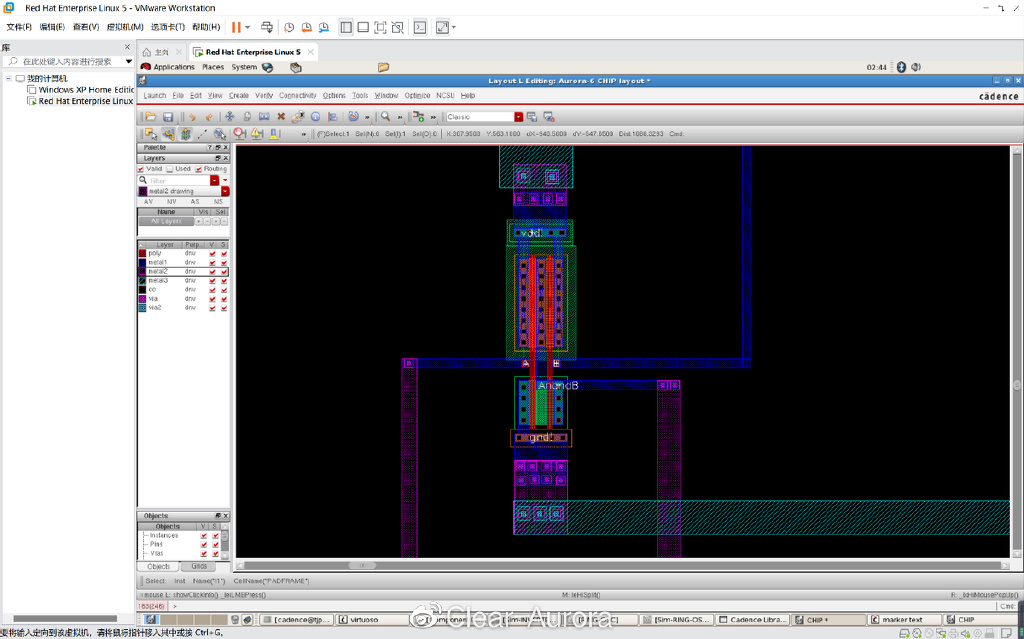

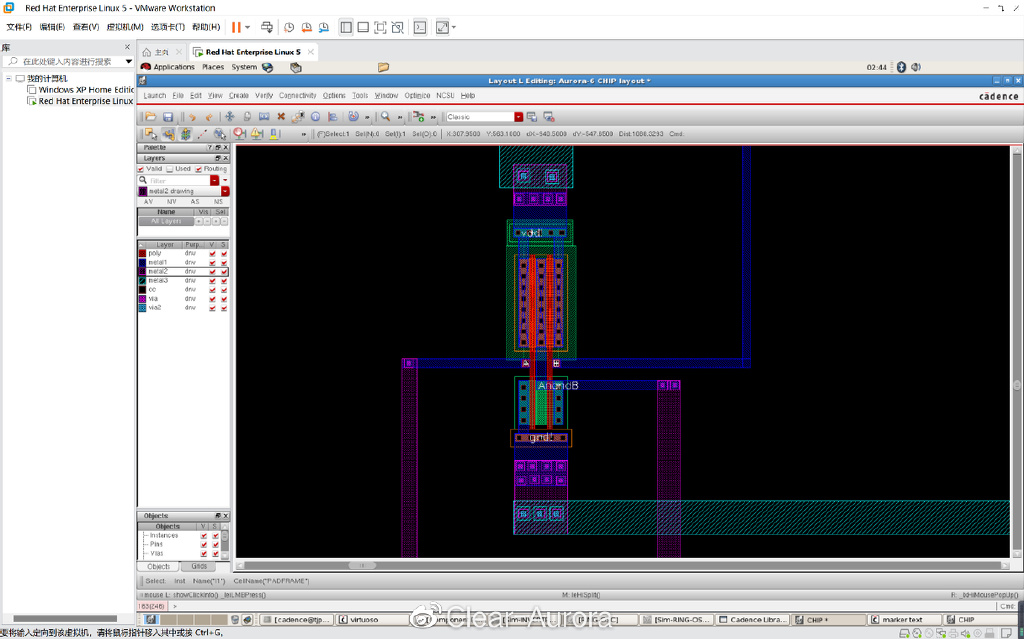

上图为二输入与非门版图连接方式。

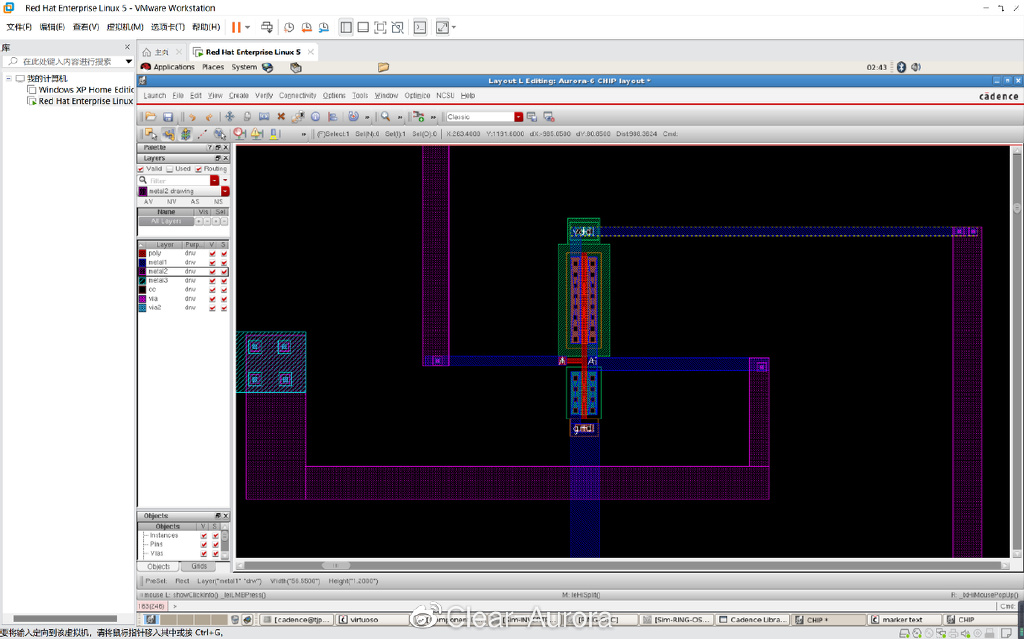

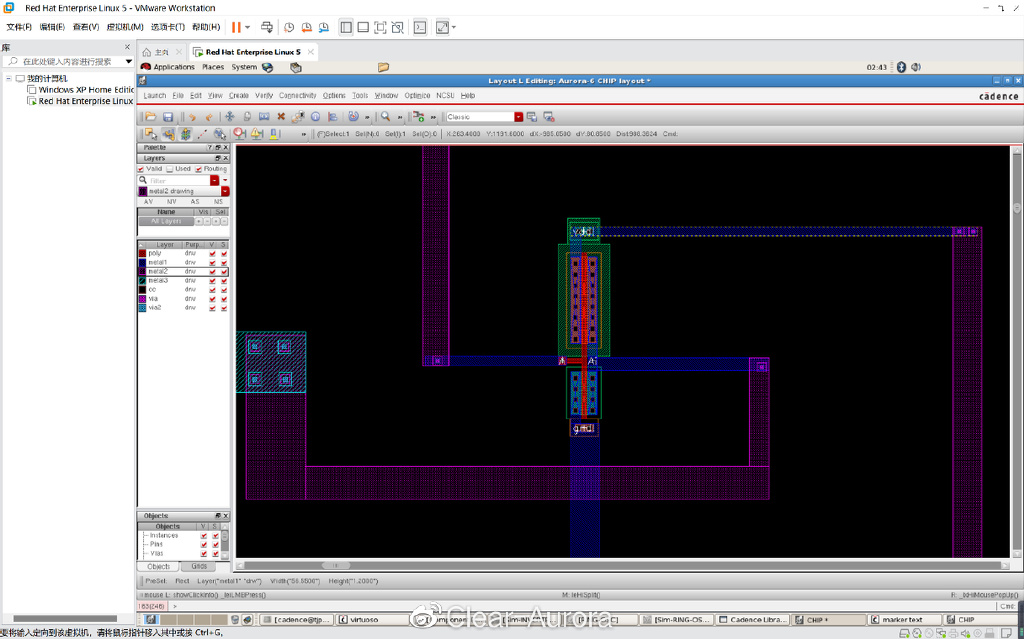

上图为反相器版图连接方式。

上图为NMOS版图连接方式。

上图为PMOS版图连接方式。

上图为电阻分压器版图连接方式。

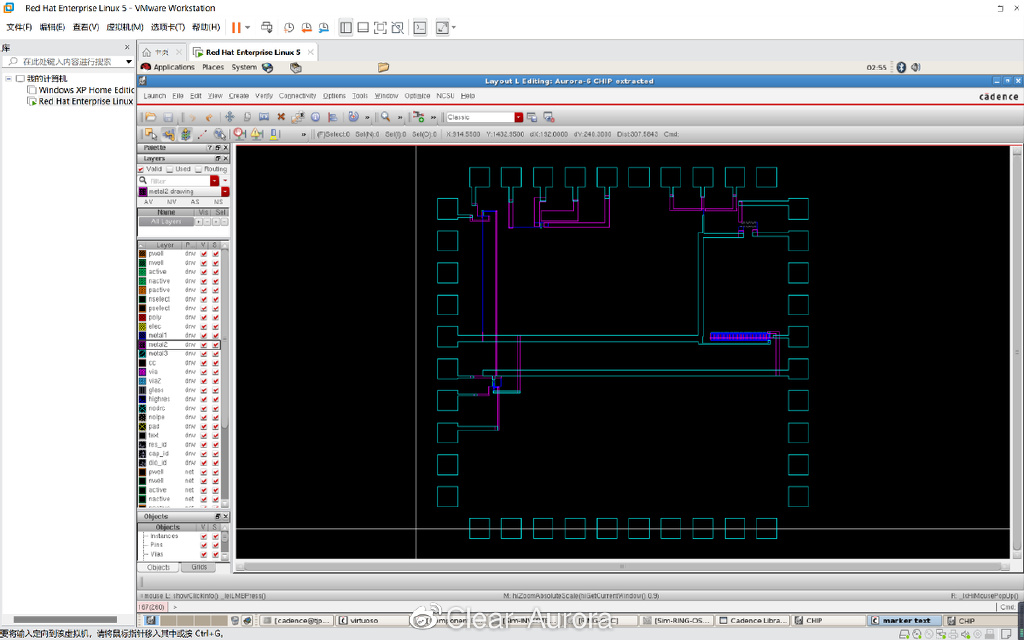

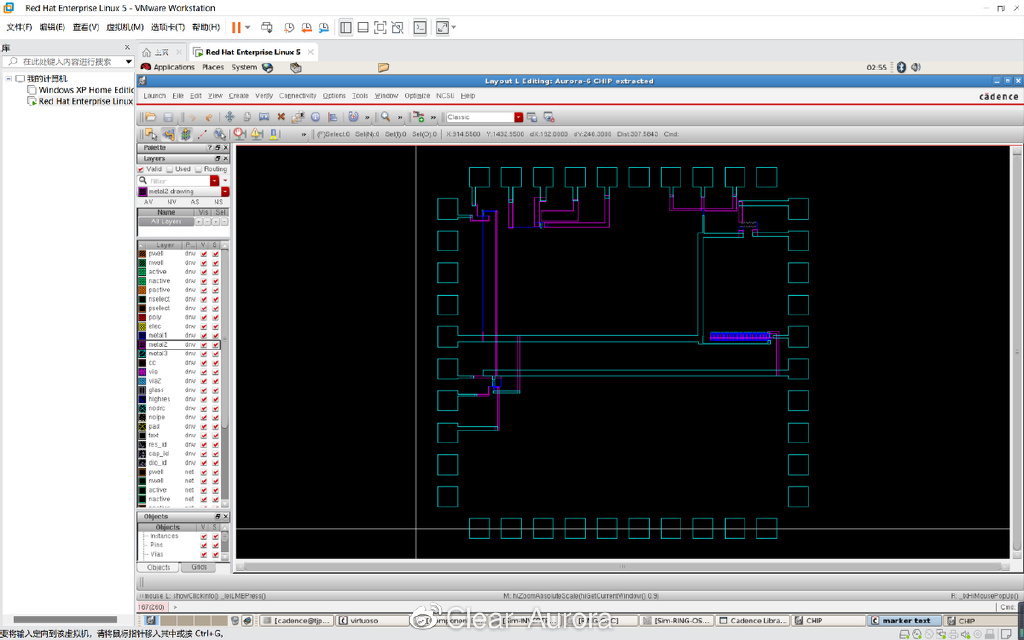

DRC芯片版图Layout后,导出CHIP版图的抽取视图(Extracted),成功后如下图所示:

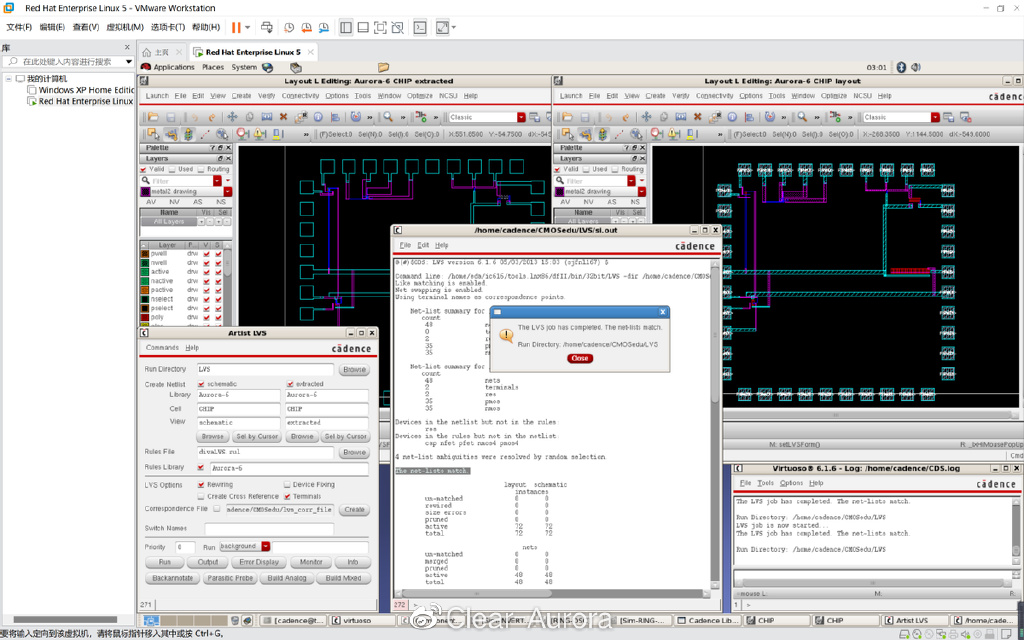

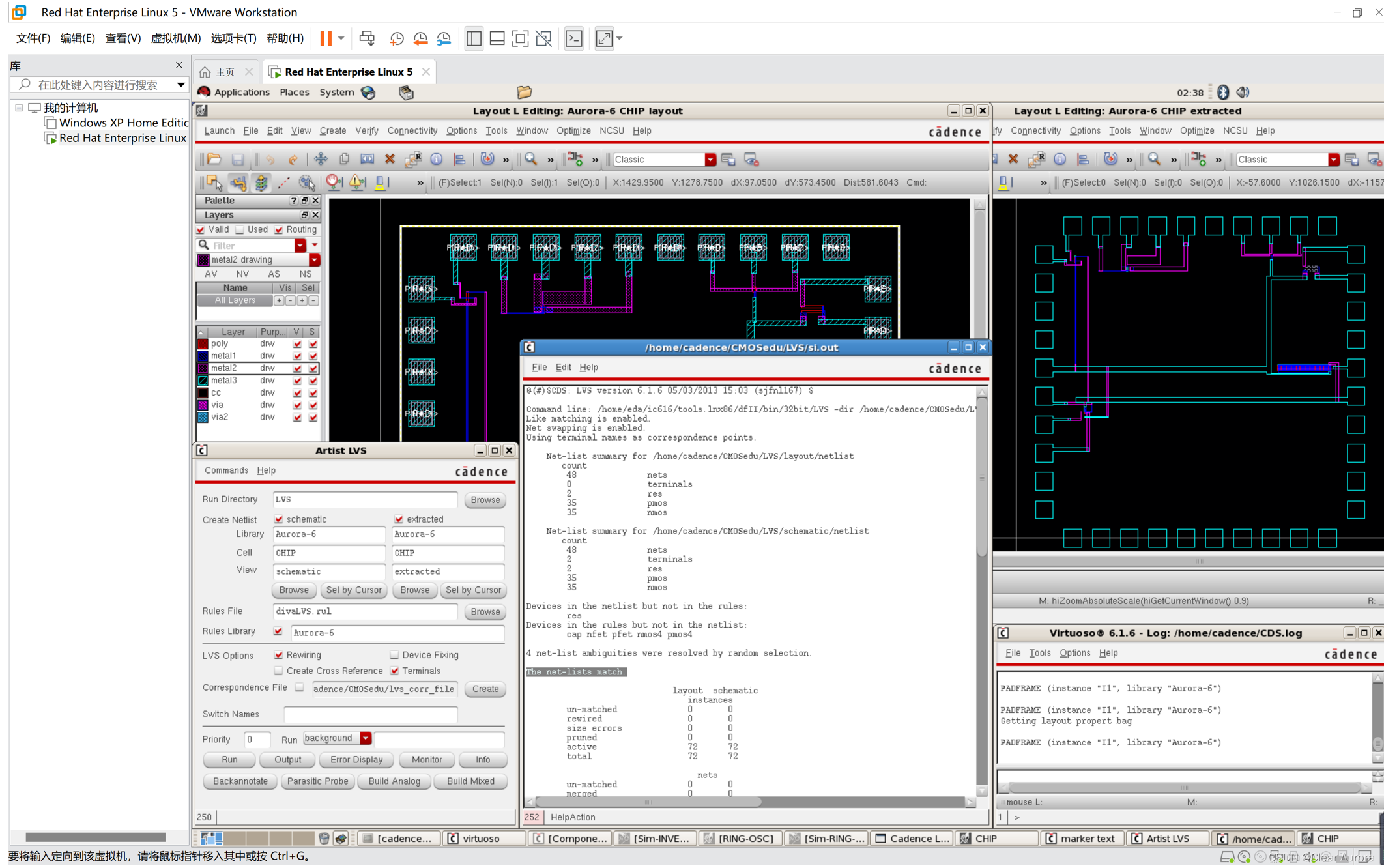

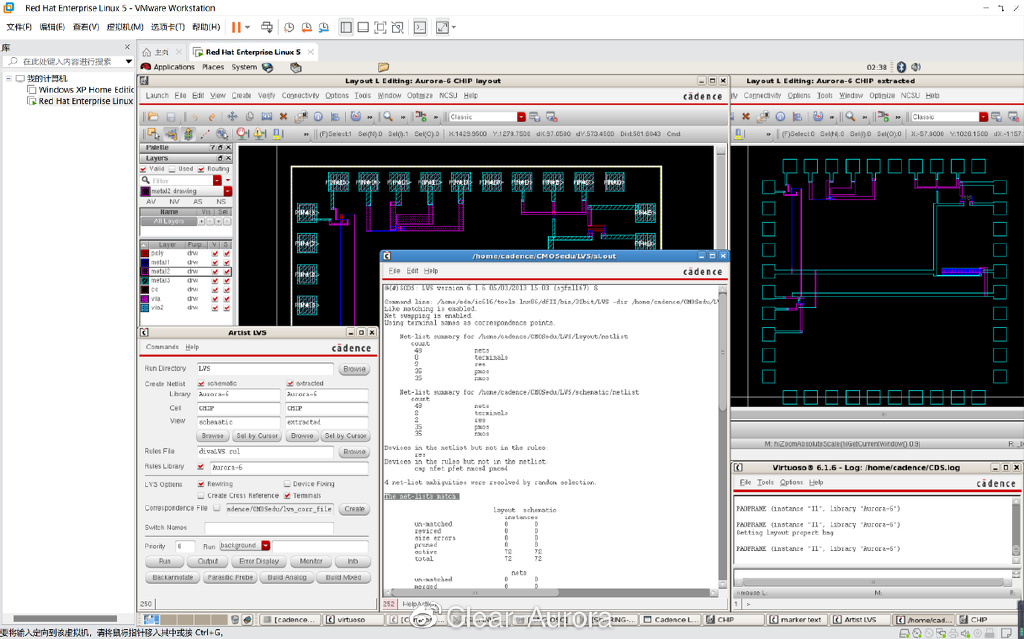

检查并使CHIP版图的抽取视图(Extracted)与CHIP的原理图相匹配,运行LVS,LVS完成后,结果如下:

芯片CHIP版图抽取视图LVS的Output显示“The net-lists match.”,Output结果如下图:

可见芯片版图设计无问题,CHIP原理图与版图及其抽取视图相匹配。至此,焊盘、芯片焊盘框架以及完整芯片(含元器件)的版图布局设计结束。

三、设计结果:

1.原理图(Schematic):

上图为焊盘PAD原理图及Symbol绘制结果。

上图为焊盘框架PADFRAME原理图及Symbol绘制结果。

上图为芯片(含元器件)原理图。

版图(Layout)设计:

上图为焊盘PAD版图绘制结果。

上图为焊盘框架PADFRAME版图绘制结果。

上图为芯片CHIP版图绘制结果。

其中各元件与焊盘、VDD和GND的金属层具体连接如下:

上图为环形振荡器输出端版图连接方式。

上图为二输入与非门版图连接方式。

上图为反相器版图连接方式。

上图为NMOS版图连接方式。

上图为PMOS版图连接方式。

上图为电阻分压器版图连接方式。

抽取视图(Extracted):

上图为芯片CHIP的版图抽取视图结果。

LVS结果:

上图为芯片CHIP版图及原理图匹配成功后LVS的Output结果。(显示“The net-lists match.”)

2019

2019

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?