ARM篇二--寄存器组织与异常处理

一、ARM寄存器组织

1 寄存器

概念

寄存器是处理器内部的存储器,没有地址作用

一般用于暂时存放参与运算的数据和运算结果分类

包括通用寄存器、专用寄存器、控制寄存器

2 ARM寄存器

注:

打三角形的是特有寄存器,属于该模式下特有别的模式无法用

没有打三角形的是共用寄存器,属于每个模式都可以使用

3 专用寄存器

R15(PC,Program Counter)

程序计数器,用于存储当前取址指令的地址R14(LR,Link Register)

链接寄存器,一般有以下两种用途:- 执行跳转指令(BL/BLX)时,

LR会自动保存跳转指令下一条指令的地址程序需要返回时将LR的值复制到PC即可实现 - 产生异常时,对应异常模式下的

LR会自动保存被异常打断的指令的下一条指令的地址,异常处理结束后将LR的值复制到PC可实现程序返回

- 执行跳转指令(BL/BLX)时,

R13(SP,Stack Pointer)

栈指针,用于存储当前模式下的栈顶地址

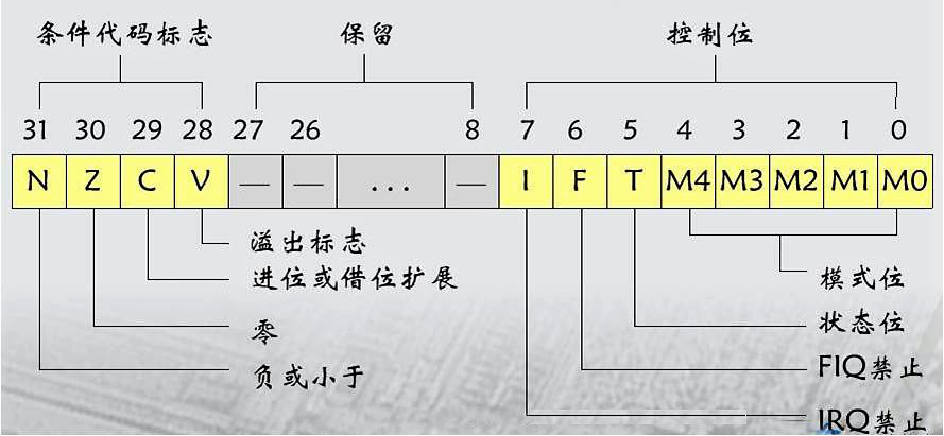

4 CPSR寄存器

CPSR(Current Program Status Register),当前程序状态寄存器CPSR寄存器分为四个域,[31:24]为条件域用F表示、[23:16]为状态域用S表示、[15:8]为预留域用X表示、[8:0]为控制域用C表示

Bit[4:0]

[10000]User [10001]FIQ [10010]IRQ [10011]SVC

[10111]Abort [11011]Undef [11111]System [10110]Monitor

Bit[5]

[0]ARM状态 [1]Thumb状态

Bit[6]

[0]开启FIQ [1]禁止FIQ

Bit[7]

[0]开启IRQ [1]禁止IRQ

Bit[28]

当运算器中进行加法运算且产生符号位进位时该位自动置1,否则为0

当运算器中进行减法运算且产生符号位借位时该位自动置0,否则为1

Bit[29]

当运算器中进行加法运算且产生进位时该位自动置1,否则为0

当运算器中进行减法运算且产生借位时该位自动置0,否则为1

Bit[30]

当运算器中产生了0的结果该位自动置1,否则为0

Bit[31]

当运算器中产生了负数的结果该位自动置1,否则为0

二、ARM异常处理

1 异常

处理器在正常执行程序的过程中可能会遇到一些不正常的事件发生,这时处理器就要将当前的程序暂停下来转而去处理这个异常的事件,异常事件处理完成之后再返回到被异常打断的点继续执行程序

1.1 异常处理机制

不同的处理器对异常的处理的流程大体相似,但是不同的处理器在具体实现的机制上有所不同;

比如处理器遇到哪些事件认为是异常事件遇到异常事件之后处理器有哪些动作、处理器如何跳转到异常处理程序如何处理异常、处理完异常之后又如何返回到被打断的程序继续执行等我们将这些细节的实现称为处理器的异常处理机制

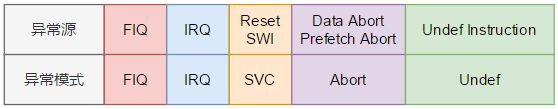

1.2 ARM异常源

导致异常产生的事件称为异常源

ARM的异常源

FIQ 快速中断请求引脚有效

IRQ 外部中断请求引脚有效

Reset 复位电平有效

Software Interrupt 执行swi指令

Data Abort 数据终止

Prefetch Abort 指令预取终止

Undefined Instruction 遇到不能处理的指令

1.3 ARM异常模式

在ARM的基本工作模式中有

5个属于异常模式,即ARM遇到异常后会切

换成对应的异常模式

2 ARM异常响应

2.1 产生异常的动作(自动)

1.拷贝CPSR中的内容到对应异常模式下的SPSR_<mode>

2.修改CPSR的值

2.1.修改中断禁止位禁止相应的中断

2.2.修改模式位进入相应的异常模式 产生异常

2.3.修改状态位进入ARM状态

3.保存返回地址到对应异常模式下的LR_<mode>

4.设置PC为相应的异常向量(异常向量表对应的地址)

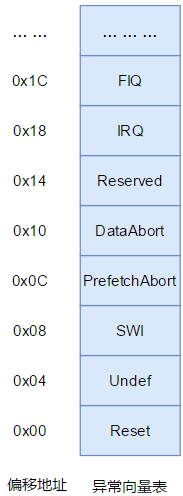

2.2 异常向量表

异常向量表的本质是内存中的一段代码- 表中为

每个异常源分配了四个字节的存储空间 - 遇到异常后

处理器自动将PC修改为对应的地址 - 因为

异常向量表空间有限一般我们不会再这里写异常处理程序,而是在对应的位置写一条跳转指令使其跳转到指定的异常处理程序的入口

注:

ARM的异常向量表的基地址默认在0x00地址,但可以通过配置协处理器来修改其地址

3 异常返回

ARM异常处理完返回的动作(自己编写)

1.将SPSR_<mode>的值复制给CPSR

使处理器恢复之前的状态

产生异常

2.将LR_<mode>的值复制给PC

使程序跳转回被打断的地址继续执行

4 异常优先级与速度

4.1 异常优先级

Reset

Data Abort

FIQ

IRQ

Prefetch Abort

Software Interrupt

Undefined instruction

优先级由高到低

4.2 异常向量表

FIQ的响应速度比IRQ快

- FIQ在

异常向量表位于最末

可直接把异常处理函数写在异常向量表之后,省去跳转 - FIQ模式有

5个私有寄存器(R8-R12)

执行中断处理程序前无需压栈保存寄存器,可直接处理中断 - FIQ的优先级高于IRQ

- 两个中断同时发生时先响应FIQ

- FIQ可以打断RIQ,但IRQ不能打断FIQ

三、ARM微架构

1 指令流水线

流水线

图例的意思是,一个货物组成需要经过组装、包装、装箱三个步骤,

当只有一个工人时,一个工人按顺序1s按顺序完成一个步骤,完成后接着下一个货物组成。

当有三个工人时,三个工人分别负责三个步骤,第一个工人完成组装后交给第二个工人完成包装,第一个工人继续下一个货物的组装,第二个工人完成包装后,这时第一个工人完成组装,第二个工人交给第三个工人完成装箱,第一个工人交给第二个工人完成包装,第一个工人继续组装下一个货物,到第四秒时,三个工人同时工作,这就是流水线模式

指令流水线

将指令的取址、解码、执行三个执行过程,变成流水线形式执行,就是流水线指令。

ARM指令流水线

ARM7采用3级流水线

ARM9采用5级流水线

Cortex-A9采用8级流水线

注1:虽然流水线级数越来越多,但都是在三级流水线的基础上进行了细分

PC的作用(取地址)

不管几级流水线,PC指向的永远是当前正在取指的指令,而当前正在执行的指令的地址为PC-8

2 多核处理器

多核处理器

即一个SOC片上系统中集成了多个CPU核作用

不同的线程可以运行在不同的核心中,做到真正的并发资源

多核处理器共用外设与接口资源

例如:

四核处理器

到这里就结束啦!

660

660

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?