注意:下面是本人的学习笔记,如有问题请留言。

分频器是数字系统中最常见的基本电路之一。分频就是将输入信号的频率变成成倍地低于输入频率的输出信号。

50MHZ,6分频后输出信号频率为8.333333MHZ

有两种方法:分频法和降频法。

分频法(占空比50%)编程:

module divider

(

input clk,

input rst,

output reg clk_6

);

reg [1:0] cnt;

always@(posedge clk or negedge rst)

if(rst == 1'b0)

begin

cnt <= 3'b0;

clk_6 <= 1'b0;

end

else if(cnt == 3'd2)

begin

cnt <= 3'b0;

clk_6 <= ~clk_6;

end

else

cnt <= cnt + 3'b1;

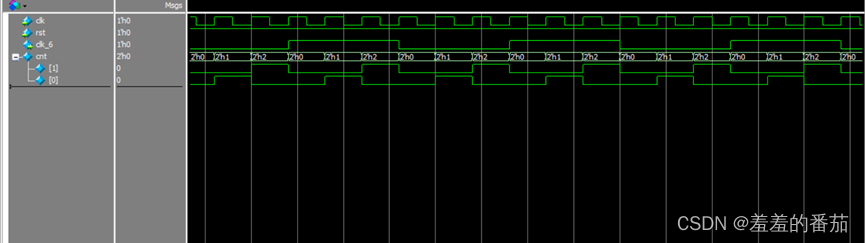

endmodule仿真波形:

降频法(占空比1/6)编程:

module divider

(

input clk,

input rst,

output reg clk_6

);

reg [2:0] cnt;

always@(posedge clk or negedge rst)

if(rst == 1'b0)

cnt <= 3'd0;

else if(cnt == 3'd5)

cnt <= 3'b0;

else

cnt <= cnt + 3'd1;

always@(posedge clk or negedge rst)

if(rst == 1'b0)

cnt <= 3'd0;

else if(cnt == 3'd4)

clk_6 <= 1'b1;

else

clk_6 <= 1'b0;

endmodule

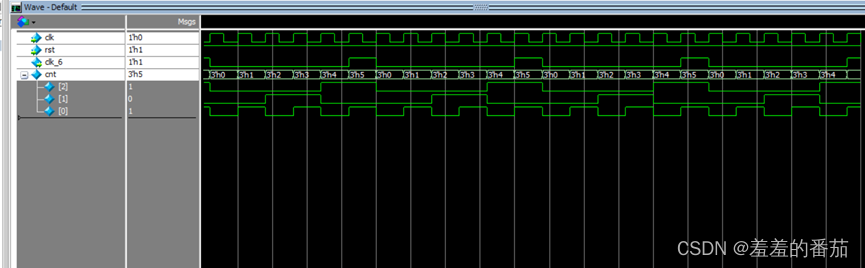

仿真波形:

1146

1146

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?